#### UNIVERSITA' DELLA CALABRIA

Dipartimento di Ingegneria Informatica, Modellistica, Elettronica e Sistemistica

Dottorato di Ricerca in

ICT

CICLO XXXIII

### STUDY AND CHARACTERIZATION OF MODERN 4H-SiC POWER MOSFETs

Settore Scientifico Disciplinare ING-INF/01

Coordinatore: Ch.mo Prof. Felice Crupi

Supervisore/Tutor: Ch.mo Prof. Felice Crupi

Dottorando: Dott. Giuseppe Consentino

#### UNIVERSITA' DELLA CALABRIA

Dipartimento di Ingegneria Informatica, Modellistica, Elettronica e Sistemistica

#### Dottorato di Ricerca in

ICT

CICLO XXXIII

### STUDY AND CHARACTERIZATION OF MODERN 4H-SiC POWER MOSFETs

### Settore Scientifico Disciplinare ING-INF/01

Dottorando: Dott. Giuseppe Consentino

COSENZA, 03/01/2021

Firma

## Contents

| Acknowle    | dgement                 |                                                                                        | iv             |

|-------------|-------------------------|----------------------------------------------------------------------------------------|----------------|

| About the   | author                  |                                                                                        | vi             |

| List of pub | lications n             | nade during the doctoral thesis                                                        | xi             |

| Abstract o  | f the disse             | rtation                                                                                | xii            |

| Chapter 1   | Introducti              | on                                                                                     | 1              |

| Chapter 2   | Power MC                | OSFET transistors                                                                      |                |

| 2.1         | Evolut                  | ion of Power MOSFET technologies                                                       | 4              |

|             | 2.1.1                   | Optimization of FOM and switching of power MOSFETs                                     | 13             |

|             | 2.1.2                   | Breakdown voltage of power MOSFETs and design rules                                    | 16             |

|             | 2.1.3                   | Absolute maximum ratings and SOA of power MOSFETs                                      | 20             |

|             | 2.1.4                   | BTI effect                                                                             | 22             |

|             | 2.1.5                   | Scaling down process of MOSFETs                                                        | 23             |

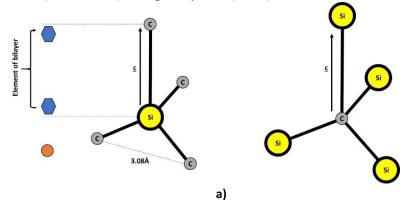

| 2.2         | Prope                   | rties of the Silicon Carbide material                                                  | 24             |

|             | 2.2.1                   | Doping mechanisms of Silicon Carbide                                                   | 28             |

|             | 2.2.2                   | Epitaxial growth of Silicon Carbide crystals                                           | 29             |

|             | 2.2.3                   | Defects in SiC crystal                                                                 | 31             |

|             | 2.2.4                   | Silicon dioxide growth process in SiC power MOSFETs                                    | 34             |

|             | 2.2.5                   | Defects in the Interface in SiC power MOSFETs                                          | 36             |

|             | 2.2.6                   | Passivation Techniques of Defects in the Interface                                     | 38             |

|             | 2.2.7                   | How POA treatments work in reducing defectiveness: simulations based the DFT technique | on<br>40       |

| Chapter 3   | Low frequ               | ency Noise in power MOSFETs                                                            |                |

| 3.1         | Funda                   | mentals of noises analysis in electronics                                              | 45             |

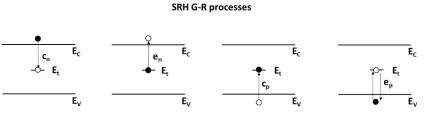

|             | 3.1.1<br>3.1.2<br>3.1.3 | Thermal noise<br>Shot noise<br>Generation-Recombination noise                          | 48<br>49<br>50 |

|             |                         | 3.1.3.1 RTS noise                                                                      | 51             |

|              | 3.1.4 Flicker noise                                                                                                                  | 2 |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|---|--|

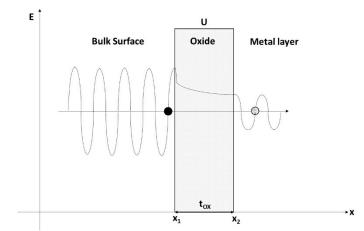

| 3.2          | McWhorter model                                                                                                                      |   |  |

| 3.3          | Mobility fluctuation model                                                                                                           |   |  |

| 3.4          | Correlated number-mobility fluctuation model                                                                                         |   |  |

| 3.5          | Unified model for flicker noise                                                                                                      |   |  |

| 3.6          | Modeling of flicker noise with stochastic processes AR and MA                                                                        |   |  |

|              | 3.6.1MA stochastic processes                                                                                                         |   |  |

| 3.7          | Entropy and approximate entropy of stochastic processes                                                                              | 3 |  |

| Chapter 4 De | fectiveness characterization of the oxide-substrate interface in SiC power MOSFETs                                                   |   |  |

| 4.1          | Description of the experimental analyses performed on some SiC power MOSFET<br>samples to characterize the oxide-substrate interface |   |  |

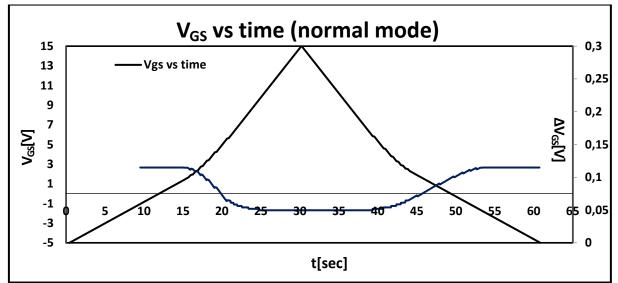

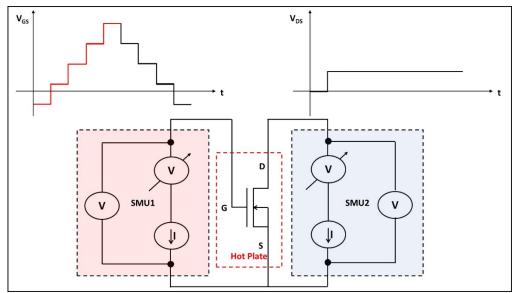

| 4.2          | Threshold-Voltage Instability Measurements in SiC power MOSFETs                                                                      | ) |  |

|              | 4.2.1 Effect of the Threshold-Voltage Instability on performance of SiC powe                                                         | r |  |

|              | MOSFETs                                                                                                                              | 1 |  |

| 4.3          | Bias Temperature Instability Measurements in SiC power MOSFETs                                                                       | 3 |  |

| 4.4          | Characterization and Modeling of BTI in SiC MOSFETs by TCAD simulations 110                                                          |   |  |

| 4.5          | Characterization of the SiC-SiO <sub>2</sub> interface using spectroscopic techniques 114                                            |   |  |

| 4.6          | Low frequency noise measurements on SiC power MOSFET devices previo<br>tested                                                        |   |  |

|              | 4.6.1 The low frequency noise studied from the point of view of the approximate                                                      | ē |  |

|              | entropy of the tested SiC power MOSFETs 136                                                                                          | 5 |  |

|              | 4.6.2 Experimental results obtained from low frequency noise measurements                                                            | S |  |

|              | carried out on the tested SiC power MOSFETs 142                                                                                      | L |  |

|              | 4.6.3 The low frequency noise studied from the point of view of the time analysis                                                    | , |  |

|              | of the tested SiC power MOSFETs 149                                                                                                  | 9 |  |

| Chapter 5 Co | nclusions                                                                                                                            | 2 |  |

| Appendix A L | ist of symbolsxii                                                                                                                    | i |  |

Bibliography..... xxv

# Acknowledgement

would like to express my sincere gratitude for my tutor and friend Prof. Felice Crupi for his guidance, continuous support and encouragement during this dissertation research. He taught me in the field of transistor noise study and gave me the opportunity to take this challenging course and complete this thesis.

On the front cover: Full-SiC module of power MOSFETs "https://eepower.com/technical-articles/the-next-generation-of-sic-power-modules/" Thank God for all the goals you have allowed me to achieve in my life and for all those that I hope you will allow me to reach in the future

To my wife, my daughter

and

to the memory of my parents,

in particular,

of my mother

who passed away recently.

They supported me morally in this enormous effort

with their affection and encouragement.

"There is nothing more difficult to take in hand, more perilous to conduct,

or more uncertain in its success than to take the

lead in the introduction of a new order of things."

Niccolò Machiavelli in his work entitled "The Prince" of 1513

## About the author

■ iuseppe Consentino was born in Messina (ME), Italy, on July 26, 1972. He received the "Diploma di perito Elettrotecnico", with full grade (60/60) from IT IS "Verona Trento" of Messina (ME), Italy, in 1991. He graduated in Electronic Engineering from University of Messina, Italy, in 1997. He also graduated in Statistical, Demographical and Social Science cum Laude from University of Messina, Italy, in 2005. He obtained the Qualification to the Profession of Engineer from University of Messina in 1998. He also obtained the Qualification to the Profession of Statistical Science from University of Messina in 2005. Currently he is tenured teacher of mathematics at ITE "Luigi Sturzo" in Gela (CL). Previously, until AS 2019/2020, he was tenured teacher of mathematics at the ITCT "Dionigi Panedda" in Olbia (SS). From 3 February 1997 to 24 October 1997, he carried out in the internship in the department NPPD (New Product Power Devices) department of STMicroelectronics of Catania in the power transistors design team. He was hired at STMicroelectronics in Catania on January 7, 1999. Until October 2001, he worked as a device engineer for no-volatile FLASH memory in the Central Front-end Manufacturing team (CFM). From November 2001 until March 2005, he worked as an Senior Application Engineer in the Power Transistor Division (PTD) always in STMicroelectronics. From April 2005 until August 2016, he worked as Senior Design engineer, in particular, for power MOSFETs, in the R&D department of the PTD division. In November of 2011, he was appointed an effective and permanent member of STMicroelectronics' technical staff as an expert in the design and development of power MOSFETs. During his time spent in STMicroelectronics, he was the inventor of four U.S. and European patents:

P1: US20120014057 entitled "Integrated power adapter system for portable computers" in 2010. <u>https://www.google.com/patents/US8472176?dq=consentino&hl=it&sa=X&ved=0ahUKEwjwqvXmgMzOAhWHyRoKHf9oDRQQ6AEIXTAH;</u>

P2: US20050088859 entitled "Push-pull converter, in particular for driving cold-cathode fluorescent lamps" in 2004.

https://www.google.com/patents/US7423890?dq=consentino&hl=it&sa=X&ved=0ahUKEwjwqvXm gMzOAhWHyRoKHf9oDRQQ6AEIZjAI;

P3: EP1879229A1, US7715159 entitled "Esd protection circuit" in 2006. <u>https://www.google.com/patents/US20080013231?dq=consentino&hl=it&sa=X&ved=0ahUKEwjYj</u> <u>s2SgczOAhVE2xoKHf\_bACg4ChDoAQgkMAE;</u>

P4: US9190492 entitled "Semiconductor device with improved linear and switching operating modes" in 2012.

https://www.google.com/patents/US20140054685?dq=consentino&hl=it&sa=X&ved=0ahUKEwjYj s2SgczOAhVE2xoKHf\_bACg4ChDoAQgtMAI.

During his time spent in STMicroelectronics, he has published technical articles in numerous International Conferences as shown below:

C1: G. Consentino, G. Bazzano, "Investigations on electro-instability of low voltage, high-current MOSFETs: Theoretical Models and Experimental Comparison Results for different Structures", POWER ELECTRONICS TECHNOLOGY, PET, Chicago, USA, 2004.

C2: G. Consentino, G. Bazzano, "Safe Operating Limits In Linear Mode for the latest generation of Low Voltage Power MOSFETs: a mathematical model and experimental results", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2005.

C3: G. Consentino, "Threshold Voltage Thermal Coefficient (TVTC) of Power MOSFETs: Theoretical Study, Measures and Simulation", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2006.

C4: G. Consentino, "How the carriers' mobility in the transistor channel and its thermal gradient affects the power MOSFET thermal coefficient (TC) during the linear zone operation mode: theoretical study, measurements and simulation", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2007.

C5: G. Consentino, "How the Power MOSFET Inversion layer carriers' mobility and its thermal gradient affects the TC", INTERNATIONAL SYMPOSIUM ON INDUSTRIAL ELECTRONIC, ISIE, Vigo, Spain, 2007.

C6: G. Consentino, G. Ardita, "Anomalous Failures in Low-Voltage P-Channel Power MOSFETs during the Intrinsic Diode Recovery Time", International Symposium on Power Electronics, Electrical Drives, Automation and Motion, SPEEDAM, Ischia, Italy, 2008.

C7: G. Consentino, G. Ardita, "A simplified and approximate power MOSFET intrinsic capacitance simulation: theoretical studies, measures and comparisons", INTERNATIONAL SYMPOSIUM ON INDUSTRIAL ELECTRONIC, ISIE, CAMBRIDGE, UK, 2008.

C8: G. Consentino, G. Ardita, R. Conti, "Power MOSFET in Linear Zone working as amplifier", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2008.

C9: G. Consentino, G. Ardita, "Power MOSFET working in switching mode: study and analysis of the device's switching time considering different operating conditions", AUTOMOTIVE POWER ELECTRONICS, APE, Paris, France, 2009.

C10: G. Consentino, "A new approach to establish the thermal instability condition and the failure time during the drain current focusing process in a power MOSFET working in linear zone", International Symposium on Power Electronics, Electrical Drives, Automation and Motion, SPEEDAM, Bari, Italy, 2010.

C11: G. Consentino, T. Scandale, "Power MOSFET with integrated poly-silicon diode to monitor junction temperature, with simplified external electrical shutdown circuit to prevent thermal runaway", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2009.

C12: G. Consentino, A. Perri, "MOSFETs or IGBTs in the modern ERC and Sustain Modules of PDPs? An empirical approach for choosing suitable Power Switches", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2010.

C13: G. Consentino, "Power MOSFETs reliability during harsh power cycling and the importance of the temperature control technique", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2011.

C14: G. Consentino, A. Gaito, "Which Power MOSFET technologies in LLC HB converters?", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2012.

C15: G. Consentino, "Power MOSFETs working in Linear Zone: the dangerous effect of the K gain factor on thermal instability", International Symposium on Power Electronics, Electrical Drives, Automation and Motion, SPEEDAM, Sorrento, Italy, 2012.

C16: D. Cavallaro, G. Consentino, "Irradiated HV Power MOSFETs working in Linear Zone: a comparison of electro-thermal behavior with standard HV products", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2013.

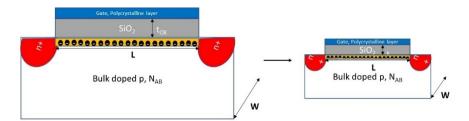

C17: S. La Mantia, G. Consentino, "Gate oxide defectiveness levels: an experimental comparison between Planar and Trench Low Voltage Power MOSFET technologies", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2013.

C18: G. Consentino, M. Laudani, G. Privitera, C. Pace, C. Giordano, J. Hernandez, M. Mazzeo, "Effects On Power Transistors Of Terrestrial Cosmic Rays: Study, Experimental Results and Analysis", POWER ELECTRONICS TECHNOLOGY, PET, Forth Worth, USA, 2014.

C19: G. Consentino, Y. Damante, "Study of the dependence between the dissipated power and the inductance when an HV power MOSFET works in UIS passive mode test", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2014.

C20: G. Consentino, "P-channel Power MOSFETs working in Lineare Zone: theoretical and experimental studies and comparison with N-channel devices", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2014.

C21: G. Consentino, M. Laudani, M. Macauda, C. Pace, C. Giordano, J. Hernandez, "Are SiC HV power MOSFETs more robust of standard silicon devices when subjected to terrestrial Neutrons?", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2015.

C22: G. Consentino, "HV Power MOSFETs working in Linear Zone: performances comparison between standard Planar and SJ devices", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2015.

C23: F. Scrimizzi, G. Bazzano, D. Cavallaro, M. Comola, G. Consentino, S. Fortuna, G. Longo, G. Pignataro, "New LV Wide SOA Power MOSFET technology for Linear Mode operation", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2016.

C24: A. Consoli, F. Gennaro, A. Testa, G. Consentino, F. Frisina, R. Letor, A. Magrì, "Thermal instability of low voltage power-MOSFETs", 30<sup>th</sup> Power Electronics Specialists Conference, PESC, 1999.

C25: G. Consentino, D. Corona, A. Grimaldi, S. Pisano, G. Sammatrice, "A hole barrier IGBT with enhanced breakdown voltage by floating P-well",2012,"PCIM Europe Conference Proceedings", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2012.

C26: G. Consentino, M. Laudani, G. Privitera, A. Parlato, N. Marchese, E. A. G. Tomarchio, C. Pace, C. Giordano, M. Mazzeo, J. Hernandez, "Dangerous effects induced on power MOSFETs by terrestrial neutrons: A theoretical study and an empirical approach based on accelerated experimental analysis", Associazione Elettronica Informatica Telecomunicazioni, AIET, Palermo, Italy, 2013

C27: G. Consentino, D. De Pasquale, S. Galiano, A. D'Ignoti, C. Pace, J. Hernandez, M. Mazzeo, C. Giordano, "Innovative instrumentation for HTRB tests on semiconductor power devices", Associazione Elettronica Informatica Telecomunicazioni, AIET, Palermo, Italy, 2013.

During his time spent in STMicroelectronics, he has published technical articles in numerous International Journal as shown below:

J1: A. Consoli, F. Gennaro, A. Testa, G. Consentino, F. Frisina, R. Letor, A. Magrì, "Thermal instability of low voltage power-MOSFET's", IEEE Transactions on Power Electronics, 2000.

J2: C. Pace, S. Pierro, V. Cilia, G. Consentino, "A model for avalanche breakdown calculation in low-voltage trench power MOSFET devices", Semiconductor Science and Technology, 2012.

J3: C. Pace, J. Hernandez-Ambato, D. De Pasquale, G. Consentino, "Instrumentation for Innovative Semiconductor Power Devices Reliability Tests", International Journal of Engineering and Industries, IJET, 2013.

J4: I. Bertuglia, G. Consentino, M. Laudani, "Proton Irradiation on SJ HV Power MOSFETs to Realize Fast Diode Devices", HINDAWI, 2014.

J5: C. Pace, J. Hernandez-Ambato, L. Fragomeni, G. Consentino, A. D'Ignoti, S. Galiano, A. Grimaldi, "A new Effective Methodology for Semiconductor Power Devices HTRB Testing", IEEE Transactions on Industrial Electronics, 2017.

He was also a company tutor for thesis students as listed below:

T1: "PDP: study and analysis of the whole system placing particular attention on the Sustain and ERC modules and on the power switches used on them", Università della Calabria, student: Andrea Perri, Supervisor: Prof. Felice Crupi.

T2: "Studio e caratterizzazione di un power MOSFET con integrato un diodo per la misura della temperatura di giunzione. Implementazione e realizzazione di un circuito elettrico esterno che traduce la tensione di forward del diodo in un segnale elettrico proporzionale alla temperatura di giunzione", Università della Calabria, student: Tommaso Scandale, Supervisor: Prof. Felice Crupi.

T3: "Studio della generazione e della trasmissione del calore all'interno dei power MOSFET: teoria, simulazioni e misure", Università della Calabria, student : Antonio Furlano, Supervisor: Prof. Felice Crupi.

T4: "Studio di un SMPS di tipo Flyback con particolare riferimento al funzionamento del power MOSFET e all'analisi della stabilità del sistema", Università della Calabria, student : Domenico Pingitore, Supervisor: Prof. Felice Crupi.

T5: "Progettazione e realizzazione di un SMPS di tipo HB per applicazioni industriali con particolare riferimento al funzionamento del power MOSFET", Università della Calabria, student: Antonio Bianco, Supervisor: Prof. Felice Crupi.

T6: "A forward DC/DC Converter for Aerospace Application. Realizzazione e test di un convertitore DC/DC Rad-Hard", Università della Calabria, student: Andrea Palmieri, Supervisor: Prof. Calogero Pace.

## List of publications during the PhD course

### INTERNATIONAL CONFERENCES AND JOURNALS

C1: C. Parisi, G. Consentino, V. Martino Cinnero, Y. Damante, A. Grimaldi, D. Murabito, "Evaluation of Miller capacitance depending on drain-source voltage when SJ HV Power MOSFETs are in reverse mode", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2018.

C2: G. Consentino, E. Guevara, F. Crupi, L. Sanchez, S. Reggiani, G. Meneghesso, "Threshold Voltage Instability in SiC Power MOSFETs", POWER ELECTRONICS INTELLIGENT MOTION POWER QUALITY, PCIM, Nuremberg, 2019.

C3: G. Consentino, E. Guevara, F. Crupi, L. Sanchez, S. Reggiani, G. Meneghesso, "Threshold Voltage Instability in SiC Power MOSFETs", First International Workshop, Tours, France, 2019.

C4: G. Consentino, "On the reversible Threshold Voltage Shift in SiC power MOSFETs", XXV International congress of aeronautics and astronautics, AIDA, Rome, Italy, 2019.

C5: D. Cornigli, A. N. Tallarico, S. Reggiani, C. Fiegna, E. Sangiorgi, L. Sanchez, C. Valdivieso, G. Consentino, F. Crupi, "Characterization and Modeling of BTI in SiC MOSFETs", 49<sup>th</sup> European Solid-State Device Research Conference, ESSDERC, Krakow, Poland, 2019.

J1: G. Carangelo, S. Reggiani, G. Consentino, F. Crupi, G.Meneghesso, "TCAD Modeling of Bias Temperature Instabilities in SiC MOSFETs", submitted to Solid-State Electronics, special issue devoted to INFOS2021

## Abstract of the dissertation

his PhD thesis is focused on the study and characterization of the defectiveness observed in the interface between the substrate and the oxide of modern SiC power MOSFETs. In particular, all analyses carried out in this work have been implemented on two different families of devices having the same planar technology, different die size and having a breakdown voltage equal to 1200 V. This PhD thesis work was included in the framework of the European project WINSiC4AP (Wide Band Gap Innovative SiC for Advanced Power) in which the DIMES department of UNICAL participates through the IUNET consortium. The dissertation is divided in two parts. The first part, chapter 2 and chapter 3, introduces the state of art of power MOSFET technologies. In these chapters, the properties of the SiC material are also discussed and a comparison is made with the silicon. In these chapters the theoretical bases of the experiments carried out on the tested devices are also introduced. In the second part of this thesis the experiments conducted on the tested devices are described in detail and the results have been carefully analysed and explained. The experiments conducted concern the threshold voltage instability phenomenon, the BTI and the analysis of flicker noise observed in the SiC power MOSFETs analysed. Simulations based of on the threshold voltage instability phenomenon and on the BTI tests were carried out using the TCAD. The conclusions obtained by the experimental results of these tests have also been validated by some spectroscopic analyses conducted by the CNR team in Catania also within the European project WInSiC4AP.

## **1** Introduction

ower electronics is a branch of electronics that deals with devices and applications for high currents and high voltages. Generally, the applications of power electronics are the DC-DC power converters used, for example, to supplier energy for computers, laptops, mobile phones, etc..., and inverters used to convert DC voltages in AC voltages in photovoltaic applications or in motor control applications. However, power electronics involves many other application segments relating to the automotive, lighting, health care, space, avionics, etc... The power electronics devices placed within the applications are resistors, inductors, capacitors, drivers and, in particular, power transistors. Typical power transistors are Bipolar Junction Transistors, BJTs, Insulated Gate Bipolar Transistors, IGBTs, and power Metal Oxide Semiconductor Field Effect Transistors, power MOSFETs. In many cases, these components are used as switches to commutate from on state to off state and vice versa. BJTs have been widely used in power electronics in linear amplifiers and lighting applications for many years up to past two decades. However, they have been replaced by power MOSFETs and IGBTs even if they are used again in low-end applications, small signals and very high voltages (over 1800V). In fact, BJTs are bipolar devices, thus, the conduction mode involves both electrons and holes and cannot be effectively used in high frequency applications due to the higher switching times when compared, in particular, with n channel power MOSFETs which are unipolar devices. In addition, longer switching times result in higher switching losses which reduce the efficiency of entire system. Another disadvantage regarding BJTs is that the base is not insulated as in IGBTs and power MOSFETs, thus, this leads to greater current leakages when driving transistors. IGBTs are basically BJTs with insulated gate terminal, so the leakage currents are comparable to the power MOSFETs when driving the devices. They are used as switches in applications that manage high power and high voltages such as, for example, motor controls for washing machines and welders. They are preferred over BJTs because they can be used in applications that require higher switching frequencies. In some applications, conduction losses becomes predominant over switching losses. Power transistors such as BJTs and IGBTs have lower conduction losses than power MOSFETs because both charges, electrons and holes, are involved in the conduction mechanism and reduce resistance in the on state. However, nowadays, power MOSFETs are largely the most used power transistors in power electronics applications, in particular, if we consider applications that can work at very high frequencies, above 100KHz, and when they have to manage medium and low power levels. Since they were introduced, power transistors have been made with silicon and this semiconductor is still the main choice today. At any rate, worldwide, reducing energy consumption and efficient energy management have become two of the biggest challenges of the modern times. The most used form of energy is the electricity generated, in the most of cases, by fossil fuels that create environmental pollution. Furthermore, even if renewable sources have been introduced to increase the ability to produce clean energy, traditional energetic resources are decreasing with the passage of time, thus, it is necessary to optimize their use by avoiding waste. In power electronics, minimizing losses in power devices can result in a significant increase in the reduction of the overall energy consumption. In case of power transistors and, in particular, power MOSFETs, the designers have implemented various suitable actions to reduce the conduction and switching losses in the standard silicon based devices. In fact, the improvement of processes in all manufacturing phases, such as lithography, oxidation, etching, also thanks to the use of new high-performance equipment, together with the introduction of new design technologies, such as the trench and the super-junction, have made it possible to drastically reduce the size of the devices while also reducing their losses in order to

#### Introduction

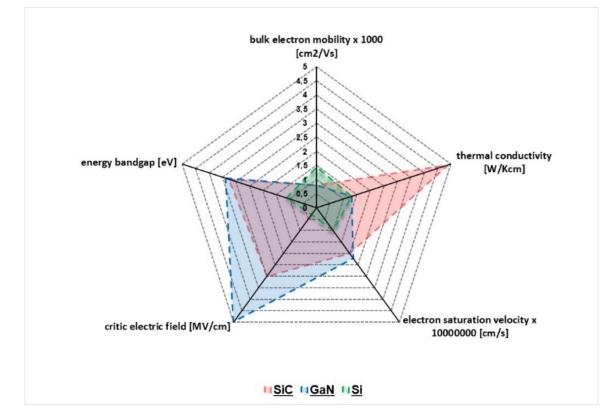

approach the limits imposed by silicon. Furthermore, from another point of view, power applications manufactures require very high performance power transistors for specific segments of high end applications in order to drastically increase the switching frequency to reduce the size of magnetic components and, thus, the volume and the weight of the whole system and significantly increase the power density managed. Silicon has been for long time, and will still be used for many years to produce electronics components because it is present in large quantities in the earth, is available at low cost and can be easily processed to produce wafers. However, in this new scenario, new semiconductor materials have recently been introduced to greatly improve the performances of power transistors in order to overcome the physical limits of silicon. These new materials are called Wide Bandgap semiconductors, WBG, because they have a greater energy bandgap than silicon. Today, the two main WBG semiconductors used to replace silicon are gallium nitride, GaN, and silicon carbide, SiC. Both materials allow to significantly increase the switching frequencies, since they have a higher electron saturation speed, reduce the switching losses, increase the breakdown voltage and decrease the resistance in the on state compared to silicon devices. In particular, the higher bandgap allows to work at higher electric field values since the impact ionization energy is higher than silicon. In fact, the critical electric field in SiC is an order of magnitude higher than silicon. Furthermore, the higher bandgap allows to obtain a much smaller concentration of intrinsic carriers in SiC and GaN compared to silicon, thus, WBG devices can work at very high temperatures. In particular, the SiC material has excellent thermal conductivity which improves power dissipation and allows operating at very high current densities. The main advantages of SiC and GaN materials compared to silicon are summarized in figure 1.1. However, SiC has a big advantage over GaN in power MOSFETs. In fact, native silicon dioxide can be grown by means of a simple thermal oxidation as in case of silicon devices. Another advantage of SiC is that high quality monocrystalline bulk substrates they can be grown at 4" or even 6". Instead, GaN is available in monocrystalline bulk substrates smaller than SiC and with extremely expensive manufacturing processes. Therefore, GaN monocrystalline bulk substrates are usually grown on silicon or sapphire substrates by heteroepitaxy processes. However, due to the lattice mismatch between GaN and silicon, many crystallographic defects are created in the active region of the device [1]. Furthermore, in GaN transistors the current generally flows horizontally while in silicon and SiC devices it flows vertically from the top to the bottom of the die to strongly increases its density. In fact, it has been observed that when making vertical GaN devices the breakdown voltage is lower and the leakage currents increase with respect to the horizontal transistors [2]. Therefore, the ability to hold high voltages in GaN devices is reduced compared to SiC transistors and, thus, they are designed to operate in low and medium voltage applications (a few hundreds of volts maximum). However, one of the main problems observed in SiC power MOSFETs concerns the high density of defects in the SiC-SiO<sub>2</sub> interface compared to the silicon devices that can cause reliability problems. In fact, it has been experimentally observed that the density of the interface defectiveness in SiC transistors can be even two orders of magnitude higher than in silicon devices. It has been observed that the interface traps in SiC devices are thermally activated and it is in stark contrast to what has been seen in silicon transistors. Consequently, the mobility of charge carriers in the channel can be at least one order of magnitude lower than the theoretical value and certainly lower than mobility measured in the silicon devices. The lower channel significantly increases the mobility observed in SiC devices channel resistance and for this reason the SiC power MOSFETs are designed to work in high or very high voltage applications where most of the resistance is mainly due to the drift region that supports the drain-source voltage applied during the off state. Finally, the high the interface defectiveness observed region of SiC power MOSFETs entails in reliability problems as instability of the threshold voltage.

Figure 1.1: Most relevant material properties of Si, SiC and GaN [5].

## **2** Power MOSFET transistors

## 2.1 Evolution of Power MOSFET technologies

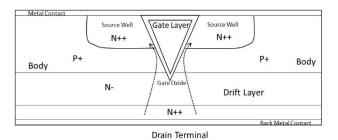

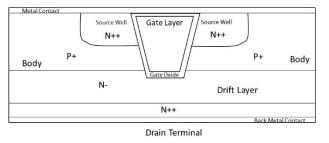

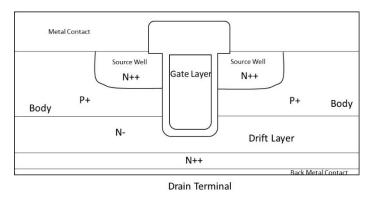

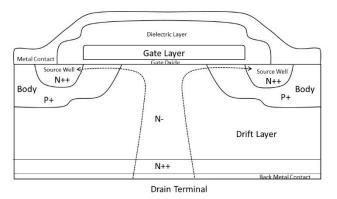

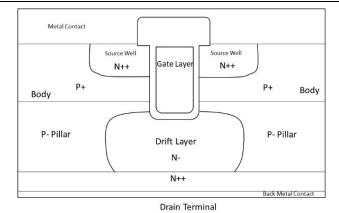

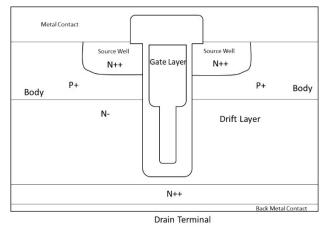

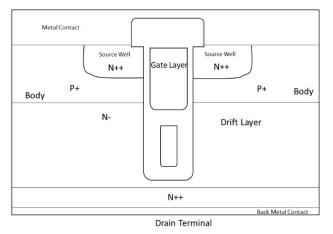

ower devices based on semiconductor materials were developed in the second half of the last century to replace large and less reliable vacuum tubes. The first commercial semiconductor device was introduced in 1954 and was a silicon based Bipolar Junction Transistor (BJT) [77]. BJT devices have been widely used for several tens of years. However, since the end of the last century they have been gradually replaced by power MOSFETs in many electronic applications even though BJTs are still used in some low-end power electronics applications [81], [92]. Indeed, it has been shows that BJTs cannot be used successfully in many new power applications due to some problems [78], [79]. One of these problems is related to the possibility that BJTs goes into thermal runaway because the coefficient between temperature and the current is positive [82]. The second point concerns the charge stored in the base of BJTs which makes the device slow during the switching regime [83], [84]. In fact, in modern devices, the switching frequencies of the BJTs do not exceeds 100kHz. Furthermore, BJTs are subjected to the phenomenon of the secondary breakdown which leads to failure of the transistors [85], [86] and have a very low base resistance which implies the passage of a high current for driving the devices [87]. Instead, power MOSFETs have the oxide and the gate current is very low because the input impedance is very high. In addition, power MOSFETs are unipolar devices and thus the charge due to minority carriers does not accumulate in the devices, thus, they are capable of supporting high switching frequencies [88]. Nowadays, considering the most advanced technologies, power MOSFETs are able to switch even beyond 300KHz. The power MOSFETs have a negative coefficient between the temperature and the current and do not go into thermal runaway, thus, power MOSFETs can be connected in parallel. However, the power MOSFETs have a greater resistance in the on state compared to the BJTs which leads to higher conduction losses. At any rate, in recent years, this disadvantages has been limited thanks to the improvements introduced in the technologies and materials of power MOSFETs that have greatly reduced the R<sub>DSON</sub> with the same die volume. However, lateral planar technology MOSFETs are not suitable for use in power applications due to DIBL problems [89], the breakdown voltage snapback phenomenon and GIDL problems near the drain [90]. Therefore, in the modern power MOSFETs, the current flows in a vertical direction from the source to the drain of the devices. The only lateral planar power MOSFETs used concerns LDMOS technology in which a light doped region is introduced into the edge of the drain to limit the drawbacks just described. However, LDMOS power MOSFETs are used only in power applications for radio frequency because they have a very limited integration capability compared to vertical devices. MOSFETs were invented by Atalla and Kahng in 1959 at Bell Labs. The first vertical power MOSFET prototype called VMOS was produced only in 1969 thanks the introduction of a V-groove shape in the gate region [80] (see figure 2.1.1). As can be seen in this figure, the current flows vertically from the drain to the source (even if in n-channel devices electrons flow in the opposite direction). The drain contact is placed on the bottom of the die while the source wells are placed on the surface. The gate structure is placed inside the substrate between two adjacent source wells. The channel is created in the interface region between the substrate and the gate oxide. The drift region allows to sustain the voltage applied between the source and the drain during the off state since the body-drift junction is reverse polarized. In particular, the drift layer is slightly doped with respect to the body region and, thus, the depletion region will widely extend along the drift layer. VMOS structures can be considered the first prototypes of modern Trench power MOSFETs.

Figure 2.1.1: Cross section of a cell of a n-channel power MOSFET with a VMOS gate structure.

Figure 2.1.2: Cross section of a cell of a n-channel power MOSFET with a UMOS gate structure.

Figure 2.1.3: Cross section of a cell of a n-channel Trench power MOSFET (UMOS of the gate structure).

Figure 2.1.4: Cross section of a cell of a VDMOS n-channel power MOSFET.

As can be seen in the same figure, power MOSFETs have an intrinsic BJT component composed of the drift and body regions. This intrinsic bipolar component could be activated if a sufficient current flows in the base (body) due to a snapback of the voltage of the device.

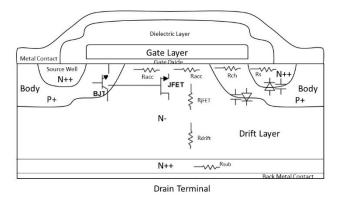

Figure 2.1.5: Cross section of a cell of a n-channel VDMOS power MOSFET which highlights the parasitic components.

Therefore, the body and source regions (the source is the BJT emitter) must be short-circuited and the concentration of the body layer must be high enough to reduce the base resistance and disable permanent bipolar conduction [91]. However, the VMOS structure of a power MOSFET is used to make low voltage devices due to the crowding of electric field lines on its bottom of the gate which does not allow to obtain particularly high breakdown voltages [93]. Subsequently, this problem was partially solved by smoothing the V-shape of the gate into a U-shape (see figure 2.1.2). Only in 1985, thanks to the introduction of the Reactive Ion Beam Etching (RIBE) process [94], a perfect rectangular groove was created in the gate structure which almost entirely solved the phenomenon of crowding the electric field (see figure 2.1.3). However, nowadays, commercial silicon-based Trench power MOSFETs are designed to withstand breakdown voltages up about to 200V even if they also starts to be used in high voltage applications together with other technical solutions that will explore later. The most common structure of power MOSFETs is planar VDMOS (Vertical Diffused MOS) as shown in figure 2.1.4. In VDMOS power MOSFETs, the gate structure is made in the upper part of the substrate and the source wells are doubly diffused in the body regions. As in case of Trench power MOSFETs, the current flows in vertical direction. VDMOS power MOSFETs are planar devices because the gate oxide has thermally grown on the die surface. The VDMOS structure introduces a parasitic JFET component that does not exist in Trench devices. The JFET is composed of the P+ regions of two adjacent cells and the drift layer between them. The JFET transistor introduces an additional resistive component to the R<sub>DSON</sub> called R<sub>JFET</sub>. When VDMOS power MOSFETs work in the on state, a suitable positive polarization is applied on the gate terminal and a carrier accumulation layer is created under the interface in the intercell region. This accumulation layer, composed of electrons in n-channel devices, introduces a new resistive component which is added to the R<sub>DSON</sub> called R<sub>acc</sub> which does not exist in the Trench power MOSFET. Others resistive components of R<sub>DSON</sub> are R<sub>drift</sub>, due to the drift layer, R<sub>sub</sub>, due to the epitaxial layer N++, R<sub>s</sub>, due to the source regions. Furthermore, it is also necessary to consider the resistance introduced by the wires, which connect the die to the package, the contact resistances of the source, drain and substrate, and the resistance of the lead frame (R<sub>wcml</sub>) (figure 2.1.5). Therefore, R<sub>DSON</sub> is equal to:

$$R_{\text{DSON}} = R_{\text{s}} + R_{\text{ch}} + R_{\text{acc}} + R_{\text{IFET}} + R_{\text{drift}} + R_{\text{sub}} + R_{\text{WCML}}$$

(2.1.1)

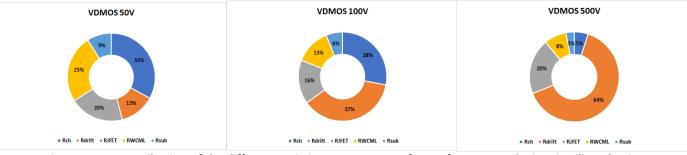

Typically,  $R_s$  and  $R_{acc}$  can be neglected if compared to other resistive components of the  $R_{DSON}$ . All these resistive components differently affect the  $R_{DSON}$  of a standard silicon VDMOS device based on the breakdown voltages for which they were designed (see figure 2.1.6 referenced to typical commercial devices [7]). As can be seen in this figure, in a 500V silicon device,  $R_{drift}$  is about 60% of the entire  $R_{DSON}$  while its contribution decreases for devices that have lower breakdown voltages.

Figure 2.1.6: Contribution of the different resistive components of R<sub>DSON</sub> for VDMOS devices in silicon having different BV<sub>DS</sub> and referenced to typical commercial devices [7].

In fact, the greater the breakdown voltage the greater the depth of the drift layer and the related resistive component. Instead, the contribution of RJFET increases slightly in a range of 15-20% of R<sub>DSON</sub> to the increase of the breakdown voltage. R<sub>ch</sub> is about 30% of R<sub>DSON</sub> for devices with breakdown voltage up to 100V. Instead, in 500V devices, its contribution decreases rapidly down to 5% of R<sub>DSON</sub> becoming almost negligible. The other components of R<sub>DSON</sub>, R<sub>sub</sub> and R<sub>wcml</sub>, maintain the same resistance values as the breakdown voltage increases but their contribution decreases because R<sub>DSON</sub> increases due to the growth of R<sub>drift</sub>. R<sub>JFET</sub> does not exist in Trench transistors, thus, they are the preferred solution for making devices with breakdown voltages up to 200V. Instead, for device with a higher breakdown voltage, it is necessary to introduce new technologies and/or materials that allow to reduce the impact of the R<sub>drift</sub> as will discussed later in this chapter. It is also important to note that the capacitances and diodes relating to the body-drift and source-body junctions respectively are also included in figure 2.1.5. In particular, the diode due to the bodydrift junction is used in some applications as freewheeling diode as, for example, in boost converters. If used in this operating conditions, the diode must be able to quickly switch from the on to the off states and vice versa, thus, the lifetimes of the carriers in the junction region must be very low. To create very fast diodes, permanent damages are created in the body-drift junctions through ionizing radiations with electrons, protons or helium or, still, in some other cases, through thermal diffusion of gold or platinum atoms [123]. These damages create traps within the semiconductor bandgap which reduce the lifetimes of the carriers due to SRH generation and recombination processes. One of the main goals of power MOSFET manufactures is to minimize R<sub>DSON</sub>, die size and intrinsic capacitance components. The decrease in R<sub>DSON</sub> allows to reduce the conduction losses while the decrease in the die size allows to lower the switching losses and, thus, to increase the switching frequency. R<sub>DSON</sub> can be reduced by acting on each of the resistive components of which is composed. For example, it is possible to reduce R<sub>ch</sub> by decreasing the length of the channel and thickness of gate oxide through a process of scaling of the technology (front-end process). Instead, Rwcml can be decreased by optimizing the diffusion processes of the source, introducing new more performing materials and improving the metallization processes (back-end process). Finally, R<sub>sub</sub> can be reduced by acting on the back of the wafer by means of chemical and mechanical scrubber processes which thins the substrate thickness or by using degenerate substrates to reduce the resistivity of the same. Regarding the Trench power MOSFETs, even after the introduction of the RIBE process [94] and the planarization of the bottom of the trench, other process innovations have been introduced to create reliable devices such as shielding of the electric field in the Trench region, the introduction of a sacrificial oxide before realizing the gate structure, the protection against avalanche multiplication phenomena of the carriers. The introduction of a fully planarized polysilicon gate in the Trench region was initially proposed by Blanchard [95], [96]. In this process of making the Trench, the source and body regions are firstly implemented through a double diffusion of the dopant, thus, the Trench is created which has a width of about 0.8-1.5µm.

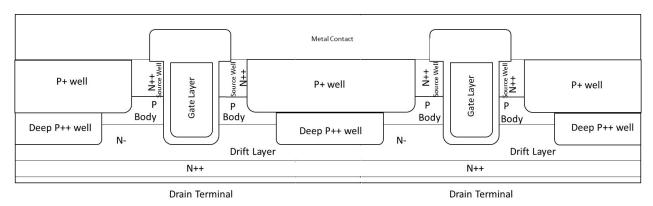

Subsequently, the etched region is oxidized to grow the gate oxide and, finally, it is filled with in situ doped polysilicon with phosphorus through a Chemical Vapor Deposition process, CVD. The polysilicon completely fills the Trench and overflows, thus, it must be etched in surface. The polysilicon is slightly overlapped with the source wells and these geometries are made through a recessed etching process as shown in figure 2.1.3. The process of the Trench gate can be optimized through thermal oxidation which seals the recessed polysilicon with a protective oxide layer. Alternatively, instead of growing the protective oxide, it can be deposited by the CVD process after the oxidation phase of the polysilicon. This protective layer of oxide must be etched with a suitable mask since a metallization layer will be deposited to contact the source wells. The oxide etching can be performed by a wet chemical etch containing HF acid or a plasma dry etch or, also, by a combination of both methods. After the deposition of the metal layer, the photolithographic patterning are performed by interconnecting the distinct VDMOS cells of the Trench to create the power MOSFET. It has been experimentally proved that the resulting cell pitch was half that obtained with any other vertical device, thus, this leads to a strong increase in the cell density and a decrease of the R<sub>DSON</sub> [92]. However, due to the variability of the process in fixing the depth of the diffused regions of the body and the Trench, avalanche multiplication phenomena could occur when the device is reverse polarized in the area near the bottom of the gate oxide which can cause both catastrophically rupture and permanent damages in the dielectric due to the injection of hot carriers. Therefore, in 1987, Blanchard proposed to grow a thick bottom oxide (TBOX) [97]. An interesting alternative approach to solving the problem was subsequently proposed by Bulucea and Rossen by introducing a deep diffusion p++ between two adjacent cells as shown in figure 2.1.7 [98], [99]. However, a small drawback with regard to this solution is related to the spreading of the current in the drift region and to the higher intercell space that must be created between the p++ wells and this increases the R<sub>DSON</sub> a little. Another solution was also proposed by Baliga in 1999 introducing oxides with graduated thickness along the vertical direction of the wall-shaped die to smooth the electric field near the bottom of the gate structure [100]. Furthermore, the peak of the electric field in the edges of the bottom of the gate structure can be greatly reduced rounding the corners of the gate oxide and optimizing the curvature of the edges, the oxide thickness and the doping concentration by using appropriate annealing processes in a hydrogen environment to increase the breakdown voltage of the Trench power MOSFETs [101]. It has been observed that while optimizing the depth of the Trench and the length of the drift region, it is possible that an increase in the breakdown voltage may occur [132]. As already explained, the drift region sustains the  $V_{DS}$  voltage when the device is turned off since it is slightly doped with respect to the body. In any case, the low doping concentration increases the resistivity of the layer which leads to an increase in the R<sub>drift</sub> and, thus, in the R<sub>DSON</sub>. This phenomenon is more marked in high voltage devices because the drift region is deeper. Therefore, it is necessary to reach a trade-off between the two electrical parameters in the designing phase to optimize the performances of the transistors considering the specific power applications in which power MOSFETs are used. The relationship between R<sub>DSON</sub> and breakdown voltage, BV<sub>DS</sub>, in silicon-based power MOSFET technologies is proportional to [102], [107]:

$$R_{\rm DSON} \propto {\rm BV}_{\rm DS}^{2.5} \tag{2.1.2}$$

However, the introduction of new technologies has improved the trade-off between  $R_{DSON}$ -BV<sub>DS</sub> as in the case of Super Junction devices, SJ, where some floating islands are inserted in the drift layer and also through the Reduced Surface Field (RESURF) techniques based on the lateral charge balancing principle [106], [109]. In particular, SJ devices show an almost linear relationship between  $R_{DSON}$ -BV<sub>DS</sub> [103]:  $R_{DSON} \propto VB_{VDS}^{1.03}$  (2.1.3)

Figure 2.1.7: Cross section of a n-channel Trench power MOSFET with p+ deep regions between two adjacent cells.

Figure 2.1.8: Cross section of an SJ cell of a n-channel VDMOS power MOSFET with floating islands of elliptical shapes.

In fact, the addition of suitable floating islands within the drift region under the body changes the distribution of the electric field in the same drift region creating several small peaks depending on the number of floating islands, thus, avoiding having a single high peak [104]. This technique greatly increases the  $BV_{DS}$  by decreasing the depth of the drift region and also significantly reducing the R<sub>drift</sub> (see figure 2.1.8) [105]. In addition, this technique also improves the performances of the body-drift intrinsic diode because it increases its switching speed. However, the floating islands in the drift region layer increase the effects produced by the JFET of the power MOSFETs which make R<sub>DSON</sub> partially grow, in particular, during the switching regimes. This latter drawback was solved by introducing passive hole gates to control the density of minority carriers [105]. The typical shapes of the floating islands used during the multiple diffusion processes by power MOSFETs manufactures have elliptical forms. From figure 2.1.8, when the body-drift junctions are reverse polarized, it is seen that the electrical field in the drift layer is arranged both along the horizontal direction and along the vertical one. Furthermore, pillars made under the P+ doped body regions do not cause any effect during the on state of the device but only contribute to increase the BV<sub>DS</sub>. When they are reverse polarized, pillars deplete completely before reaching the breakdown and the profile of the electric field becomes almost flat along the vertical direction since there are only small electrical peaks. Instead, in standard devices the shape of the electrical field along the vertical direction assumes a triangular shape. The pillars begin to deplete along the horizontal direction and then, once they are completely depleted, the electric field increases vertically until the breakdown is reached.

#### Power MOSFET transistors - Evolution of Power MOSFET technologies

Figure 2.1.9: Cross section of a n-channel VDMOS SJ-Trench power MOSFET: solution 1.

Figure 2.1.10: Cross section of a n-channel VDMOS SJ-Trench power MOSFET: solution 2.

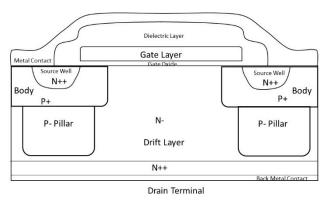

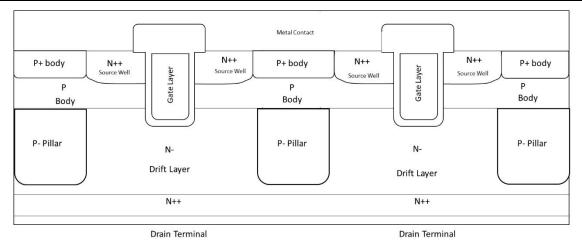

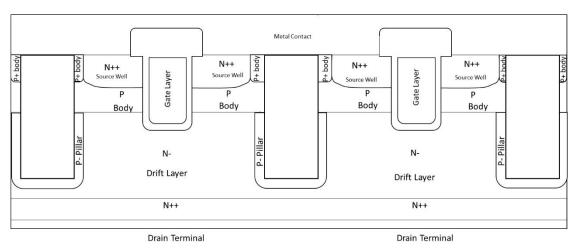

Based on how the charge is balanced in the pillars and in the drift layer, R<sub>DSON</sub> can be reduced at least 5 times compared to the VDMOS structures and the BV<sub>DS</sub> grows by about 50% for devices that have the same drift depth of the standard devices [108]. However, the ability to efficiently reduce BV<sub>DS</sub> also depends on the cell pitch. In particular, it has been shown by some simulation with TCAD that when the pitch and the doping concentration in the drift region are increased, the electric field starts to increase vertically rather than horizontally and the BV<sub>DS</sub> decreases [108]. However, it is important to emphasize that making SJ devices is a rather complex and expansive process. At any rate, despite this issue, SJ design technique is in some cases combined with Trench technology to strongly improve the performances of the devices in high-end power applications (see figure 2.1.9). The first SJ-Trench power MOSFET as shown in figure 2.1.9 was made by Hattori in 2001 [116]. In this figure it is noted how the doped pillars P- are implanted several times and subsequently diffused between two adjacent structures of Trench gate under the body regions P [110], [111]. Another example of solution of the SJ-Trench power MOSFETs is shown in figure 2.1.10 where a deep Trench with P- type implants create pillars between two adjacent Trench gate structure. The columns of the Trench can be filled with suitable deposited epitaxial layers [112], with oxide, or with sealed air gap [113]. A further new and interesting solution is also shown in figure 2.1.11 where the drift region is created under the bottom of the gate trench by means of high energy implants, typically using phosphorus, while the pillars P- are created by the layer epitaxial [114], [115].

Figure 2.1.11: Cross section of a VDMOS n-channel SJ-Trench power MOSFET: solution 3.

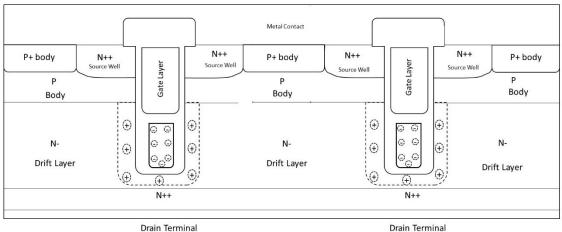

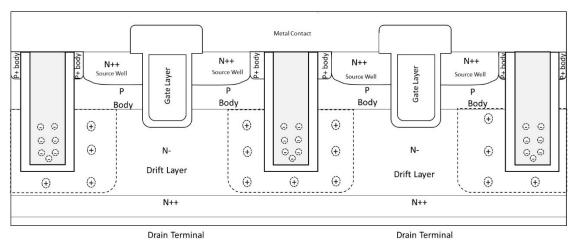

Drain Terminal

Figure 2.1.12: Cross section of a VDMOS n-channel SJ-Trench power MOSFET: solution 4.

Figure 2.1.13: Cross section of a VDMOS n-channel SJ-Trench power MOSFET: solution 5.

Finally, two other new technological solutions of the SJ-Trench power MOSFETs are shown in figures 2.1.12 and 2.1.13. In these two last methodologies the charge balancing process can be carried out using MOS capacitors instead of P- pillars since they induce a depletion region due to a negative polarization in the polysilicon layers [118], [119], [120].

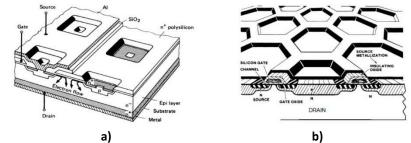

Figure 2.1.14: Two different design topologies to create power MOSFETs (figures taken from page 75 of ref. [123]): a) square cells; b) hexagonal cells.

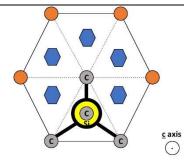

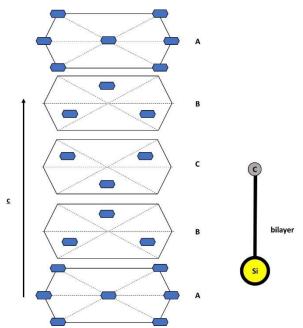

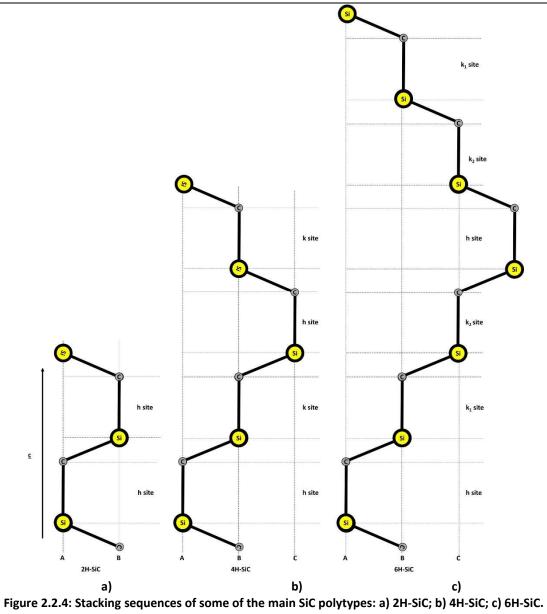

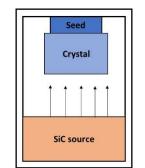

This technique can be implemented through field plates buried in trenches where the gate is split into two regions (see figure 2.1.12) or by field plates obtained from trenches alternating with the gate structures (see figure 2.1.13). The latter two techniques are called RSO. This type of technology was initially introduced in very low voltage devices but later it was even extended to power MOSFETs with higher breakdown voltages [121]. All the technological solutions just described allow to reduce the R<sub>DSON</sub> down to 30-35% compared to the Trench devices [117]. As already explained, the current flowing in power MOSFETs passes through many cells. The density of the cells is inversely proportional to the breakdown voltage of the device and depends on the technology and the scaling process. This density is in the range of 200,000-1,000,000 cells per cm<sup>2</sup> [123]. Figures 2.1.14a and 2.1.14b show two different methodologies used to integrate the cells in the structure of a power MOSFET. In the first solution, figure 2.1.14a, the power MOSFET is made by integrating square cells with standard planar VDMOS structure. Instead, in the second solution, figure 2.1.14b, the power transistor is composed of the integration of hexagonal cells. All cells are connected in parallel. These were the first solutions adopted to make power MOSFETs. Subsequently, power MOSFETs were also made with strip-shaped cells. In addition to the active region of the cell, it is also necessary to design the edge of the device in order to prevent the thickening of the electric field lines in this region by reducing the breakdown voltage of the transistor. Typically, in trench VDMOS devices along the perimeter of the die a thick oxide is grown on which metal layers are deposited which allow to lower the electric field. In very high voltage devices, design solutions have also proposed with floating field rings and new terminations that use the trench to reduce the size of the edge [124]. Typically, the doping concentrations of n++ source wells and the epitaxial drain region are in the order of 10<sup>19</sup> cm<sup>-3</sup>. In the body region, the p doping concentration reaches up to 10<sup>16</sup>cm<sup>-3</sup>. Instead, in the n- drift layer, the doping concentration is in the order of 10<sup>15</sup>-10<sup>16</sup>cm<sup>-3</sup> [122]. The silicon carbide substrates are nitrogen doped if n-type and aluminium or boron if p-type by ion implantation or with epitaxial growth. Instead, typically, silicon substrates are doped with arsenic or phosphorous to create n-type semiconductors and boron for p-type semiconductors.

## 2.1.1 Optimization of FOM and switching of power MOSFETs

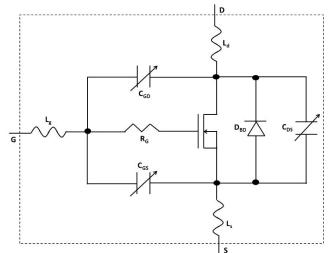

igure Of Merit, FOM, is given by the product between the gate charge, Q<sub>G</sub>, and R<sub>DSON</sub> and it is often used to evaluate the performances of power MOSFETs given their breakdown voltages. In particular, the FOM must be minimized to improve the transistor performances because the lower is the FOM the lower the conduction and switching losses. As R<sub>DSON</sub> has already been studied thoroughly in the previous paragraph, attention will now be placed on Q<sub>G</sub>. The dynamic characteristics of power MOSFETs depend on the intrinsic capacitances of the devices. Figure 2.1.1.1 shows the intrinsic components for a packaged n-channel power MOSFET. In this figure it is possible to observe that within the power MOSFETs there are three equivalent variable capacitances: C<sub>GS</sub>, C<sub>GD</sub> and C<sub>DS</sub>. These capacitances are largely determined by the size of the chip and the cell topology used and also strongly depends on the external potentials applied, V<sub>GS</sub> and V<sub>DS</sub>. With reference to the VDMOS topology, C<sub>GS</sub> is essentially given by the C<sub>OX</sub>. C<sub>GD</sub> depends on either the capacitance in the channel interface region and the drift region between two adjacent cells or on the capacitance due to the lower part of the interface with the oxide of the gate structure of a Trench power MOSFET as shown in figure 2.1.3. Therefore, to greatly reduce the C<sub>GD</sub>, for example, the cell pitch and width of the Trench could be reduced, or even the thickness of the oxide in the affected area could increase as in the case of TBOX solution for Trench devices. In planar VDMOS structure, the thickness of the oxide between two adjacent cells has grown considerably compared to the oxide along the channel. In this intercellular region, the so-called field oxide is grown which has a thickness similar to that of the edge of the die and is in the order of 1,000nm against 50-100nm in the channel region. In the case of Trench devices, even if TBOX solution is widely used to decrease C<sub>GD</sub>, other solutions have been introduced that allow to reduce the C<sub>GD</sub> along the sides of the Trench as shown in figure 2.1.1.2. In this solution the upper part of the oxide of the Trench gate has a thinner thickness but it increases going towards the bottom so that the shape resembles a terraced or stepped structure with an extended field plate [125], [126], [127]. This extended field plate allows to shield the electric field in the region where the gate oxide is thinner but, on the other hand, slightly increases the C<sub>GD</sub> by reducing the effect of the TBOX. In 2003 Baliga proposed a new design solution defined as split-gate or shielded-gate Trench VDMOS as shown in figure 2.1.1.3 [128], [129].

Figure 2.1.1.1: Equivalent circuit of a n-channel power MOSFET with intrinsic components included.

In the latter figure, the gate structure is divided in two parts filled with in situ doped polysilicon: the upper polysilicon is connected to the gate electrode while the lower one is a grounded polysilicon field plate. However, it is important to highlight that the grounded buried polysilicon introduces a capacitance placed in parallel with the gate electrode which slightly increases the C<sub>GS</sub>. Furthermore, the buried polysilicon introduces as additional capacitance placed in parallel with the C<sub>DS</sub> which increases its value overall. These latter one is mainly due to the depletion region of the junction between the body and the drift regions. Figure 2.1.1.1 highlights three small inductances, generally of few nanohenrys, L<sub>g</sub>, L<sub>s</sub> and L<sub>d</sub>, which are those introduced by the wires that connect the gate, source and drain terminals to the package.

Figure 2.1.1.2: Cross section of a n-channel Trench power MOSFET with the polysilicon gate with terraced oxide.

Figure 2.1.1.3: Cross section of a n-channel Trench power MOSFET with split gate VDMOS structure.

Figure 2.1.1.4: Typical variation of the intrinsic capacitances of the power MOSFET with the V<sub>DS</sub>.

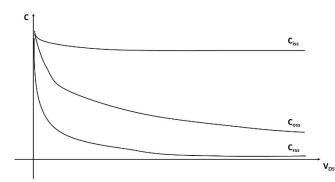

Furthermore, the intrinsic diode due to the junction between the body and the drift region was also highlighted. The resistor shown in figure 2.1.1.1, R<sub>G</sub>, is the intrinsic resistance observed dynamically by the gate terminal due to the resistivity of the polysilicon layer on which the displacement current flows during the switch on and switch off processes. It is important to underline that the manufactures of the power MOSFETs do not indicate the C<sub>GS</sub>, C<sub>GD</sub> and C<sub>DS</sub> in their datasheets but the input capacitance, C<sub>iss</sub>, the output capacitance, C<sub>oss</sub> and the reverse capacitance, C<sub>rss</sub> [123]. The C<sub>iss</sub> is measured when the drain and source terminals are short-circuited and is given by:

$$C_{iss} = C_{GS} + C_{GD}$$

(2.1.1.2)

Coss is measured when the gate and source terminals are short-circuited and is given by:

$$C_{oss} = C_{DS} + C_{GD}$$

(2.1.1.3)

Instead, the  $C_{RSS}$  is roughly equal to the  $C_{GD}$ . Typically, these capacitances are measured with signal that have a frequency of 1MHz and their variations with respect to  $V_{DS}$  are shown in figure 2.1.1.4.  $C_{RSS}$  is the component that connect the output voltage,  $V_{DS}$ , to the input terminal and, in the analysis of small signal, it is even defined as Miller capacitance. It can be classified as a feedback capacitance which is larger than real value as it can be observed in vacuum tubes amplifiers (Miller effect) [131].

## 2.1.2 Breakdown voltage of power MOSFETs and design rules

hen a power MOSFET is turned off, no current flows in the device even if a voltage is applied between the terminals of the drain and source because the V<sub>GS</sub> is lower than the Vth. In any case, the power MOSFETs are designed to sustain a predetermined maximum  $V_{DS}$  when they are turned off. Exceeding this voltage, the power transistors can no longer sustain this potential and a current begins to flow into the device. This V<sub>DS</sub> value is called the breakdown voltage, BV<sub>DS</sub>, of a power MOSFET. As already mentioned, power MOSFETs have an intrinsic diode connected between drain and source terminals and this is composed of the body and drift junction. Therefore, when a power MOSFET reaches to its breakdown voltage it means that BV<sub>DS</sub> of this diode has been reached. The breakdown mechanisms are mainly three: thermal instability, tunneling and avalanche multiplication [3]. In general, even if the breakdown of the power MOSFET is due to the phenomenon of avalanche multiplication, in this section, all mechanisms will be briefly discussed for a complete analysis of the phenomenon. When the body-drift junction is reversed polarized, a small current flows due to minority carries. This current strongly depends on the junction temperature and, in particular, it is correlated to the concentration of the intrinsic carriers: the higher the temperature the higher the concentration of intrinsic carriers. The product between the potential of the reverse junction applied and the current produces power losses which increase the junction temperature. As the temperature rises, more intrinsic carriers are thermally generated in the junction, the current increases and, thus, the junction temperature increases even more. Therefore, the device may fail due to this positive feedback between current and temperature responsible for thermal instability even called thermal runaway process. In germanium or silicon, semiconductors with low bandgap energy, this phenomenon is more evident than in silicon carbide devices. In the junctions with high concentrations of impurities on both sides, the tunnel effect due to a large reverse potential applied is the main breakdown mechanism. In fact, carriers can jump a potential barrier due to a large electric field applied if this barrier is sufficiently thin (Zener effect of band-to-band tunneling from that of valence of the body to that the conduction When a breakdown phenomenon due to the tunneling effect occurs, the BV<sub>DS</sub> of the drift). decreases with increasing temperature. In fact, as the temperature increases, it is possible to obtain the same tunneling current for smaller reverse potentials. As will be explained later, in the avalanche process the breakdown voltage increases with increasing junction temperature, thus, it is easy to distinguish between the two tunneling mechanisms. Avalanche breakdown is caused by a physical mechanism called impact ionization. In fact, when the body-drift junction is reverse polarized, the high electric field applied on the space charge layer may be sufficient to increase the kinetic energy of the free electrons until they can break the reticular bonds when they impact the structure creating additional free electrons (impact ionization mechanism). These additional electrons can in turn gain enough kinetic energy to break other bonds by creating further free electrons. Therefore, in a small time, this cascade mechanism produces a large number of free electrons which, when dragged by the reverse electric field, cause a great loss of power in the junction region until a failure occurs. This mechanism is irreversible and occurs when the electric field applied in the reverse polarized junction reaches a critical value defined as EBD. To generate an additional free electron, the incident electron must release energy at least equal to or greater than the energy bandgap during the collision. Therefore, if  $\tau_c$  is the average period so that a released electron impacts with the reticule, EBD can be estimated as [122]:

$$E_{BD} = \sqrt{\frac{2mE_g}{q\tau_c^2}}$$

(2.1.2.1)

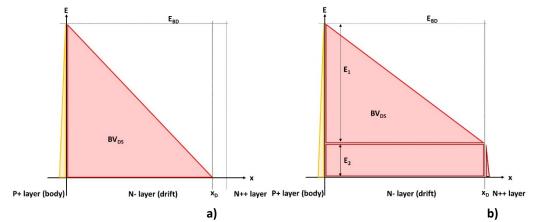

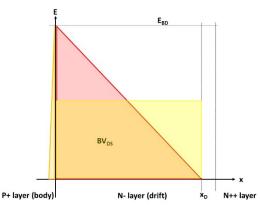

For example, in silicon semiconductors,  $\tau_{C}$  is in the order than 10<sup>-13</sup>s and, thus,  $E_{BD}$  is equal to about 0.3MVcm<sup>-1</sup>, thus, a value quite similar to that experimentally measured in power MOSFETs (0.2MVcm<sup>-1</sup>). Probably, the measured value which is lower than the estimated theorical one is due to the fact that the incident electrons do not completely lose their kinetic energy in collision with the reticule. Instead, in SiC semiconductors the  $E_{BD}$  is equal to about 3MVcm<sup>-1</sup>. As already mentioned, the p-type body region is more doped that than the n-type drift region, thus, applying a reverse potential in the junction, the depleted region spreads almost entirely in drift rather than in the body layer, thus, the BV<sub>DS</sub> can be obtained as (see figure 2.1.2.1a):

$$BV_{DS} = \frac{E_{BD}x_d}{2} = \frac{\varepsilon_{SiC}E_{BD}^2}{2qN_D}$$

(2.1.2.2)

Therefore, once the  $E_{BD}$  has been set, the  $BV_{DS}$  depends heavily on the  $N_D$ . In particular, Eq. (2.1.2.2) can be rewritten as:

$$x_{d} = 2 \frac{BV_{DS}}{E_{BD}}$$

(2.1.2.3)

Therefore, with the same  $x_d$ , the  $BV_{DS}$  in SiC substrates is 10 times greater than the  $BV_{DS}$  in silicon ones. In fact, in the SiC power MOSFETs the drift region is about a tenth compared to those in silicon. Now, considering that R<sub>DRIFT</sub> can be obtained as:

$$R_{drift} = \frac{x_d}{q\mu_n N_D}$$

(2.1.2.4)

from Eq. (2.1.2.2) and Eq. (2.1.2.3), it is possible to obtain:

$$R_{drift} = 4 \frac{BV_{DS}^2}{\varepsilon_{SiC} \mu_n E_{BD}^3}$$

(2.1.2.5)

As it is possible to see, R<sub>drift</sub> can be obtained on the square of the BV<sub>DS</sub> even if this is a theoretical approach because in real power MOSFETs this relationship can be better approximated as in Eq. (2.1.2). Even if  $\varepsilon_{SIC}$  is about 80% of the  $\varepsilon_{SI}$  and the  $\mu_n$  in the SiC is about 60% of the  $\mu_n$  in silicon, R<sub>drift</sub> depends on the inverse of cube power of the E<sub>BD</sub> which in silicon is one tenth of the SiC, thus, once the BV<sub>DS</sub> is fixed, the drift resistance in SiC is very low compared to silicon devices. In addition, the doping concentration on the drift layer can also be about one hundred times higher than that in silicon power transistors. As it is possible to see in figure 2.1.2.1a, the maximum value of the electric field,  $E_{BD}$ , is reached in the border between the body and the drift layers. The electric field decreases linearly along the body and the drift regions up to zero with a triangular shape. Since the drift region has a lower doping concentration than the body, the electric field extends along a large portion of the drift layer while only a very small portion spreads in the body and, thus, the latter part can be neglected. The breakdown potential, BVDS, is obtained from the area of the triangle as in Eq. (2.1.2.2). In this case we work in non-punch-through conditions. If the drift region is too light doped, the depleted layer can spread down to the N++ layer before reaching the breakdown condition as shown in figure 2.1.2.1b. In this case, the device is in punch-through condition, the electric field decreases drastically in the N++ region and it takes a trapezoidal shape in the drift region. Therefore, the BV<sub>DS</sub> becomes equal to the sum of the rectangular and triangular areas of the electric field in the entire drift region. The area of the triangular portion is given by:  $aN_{D}Xd^{2}$ .1.2.6)

$$V_1 = \frac{q_{\rm NDAd}}{2\varepsilon_{\rm SiC}} \tag{2}$$

and the portion of rectangular area is equal to:

$$V_2 = E_2 x_d$$

(2.1.2.7)

Considering that:

$$E_{BD} = E_1 + E_2$$

(2.1.2.8)

and:

$$BV_{DS} = V_1 + V_2 \tag{2.1.2.9}$$

we obtain:

Power MOSFET transistors - Evolution of Power MOSFET technologies - Breakdown voltage of power MOSFETs and design rules

$$BV_{DS} = E_{BD} x_d - \frac{q N_D x_d^2}{2\varepsilon_{SiC}}$$

(2.1.2.10)

Therefore, it is possible to obtain:

$$BV_{DS} > E_{BD}x_d \tag{2.1.2.11}$$

and, again:

$$x_{d} < \frac{BV_{DS}}{E_{BD}} < 2\frac{BV_{DS}}{E_{BD}}$$

(2.1.2.12)

However, even if  $x_d$  is lower in punch-through devices, the greater resistivity in the drift region due to the lower doping concentrations increases  $R_{drift}$ , and, thus, increases the conduction losses. In case of SJ devices as shown in figure 2.1.8, the electric field in the drift region is quite flat and can be represented as a rectangular rather than a triangle along the x axis (see figure 2.1.2.2). As seen in figure 2.1.2.2, while the breakdown voltage is reached quickly in the standard devices, in the SJ power transistors the electric field remains lower than the critical  $E_{BD}$  value and, thus, the  $V_{DS}$  can also be doubled before reaching the critical electric field. In any case, in SJ devices the doping concentrations in the drift and body regions must be readjusted to obtain an adequate balance of charge in the pillars and, thus, the study is more complicated to describe. In these example the  $BV_{DS}$  is obtained by considering flat junctions but this case is not realistic in practice. In fact, the region of the body is created through diffusion of impurities which determine a certain degree of curvature of the body-drain junction. The radius of curvature depends on the size of the substrate etch masks, on the time and temperature of the diffusion processes, also considering that impurities spread more quickly laterally rather than vertically.

Figure 2.1.2.1: Spread of the depleted region along the body-drift junction: a) no punch-through; b) punch-through.

Figure 2.1.2.2: Spread of the depleted region along the body-drift: comparison between standard VDMOS and SJ.

This phenomenon is particularly evident when the radius of curvature becomes comparable to the width of the depletion layer of the junction. In fact, the electric field increases in the junction and becomes larger as the radius of curvature decreases and this determines a lowering of the breakdown voltage of the device with respect to a perfectly flat junction. Therefore, the radius of curvature must be controlled and metal plates must be introduced to smooth the electric field along the edge of the junction. However, in the case of power MOSFETs as shown in figure 2.1.4, the gate plates located in the intercell region perform this function, thus, it is not necessary to introduce other structures for this scope.

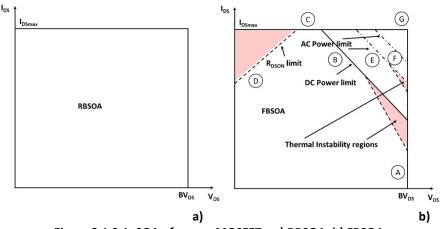

### 2.1.3 Absolute maximum ratings and SOA of power MOSFETs

Solutions is limited by four lines: the maximum sustainable voltage, BV<sub>DS</sub>, region A, the maximum power that can dissipate, region B, the maximum allowed current, I<sub>DSmax</sub>, region C, and the maximum current flowing in the device limited by R<sub>DSON</sub>, region D. In particular, in region B, it is possible to obtain:

$$\Delta T_{\text{max}} = T_{\text{Jmax}} - T_{\text{C}} = R_{\text{thJC}}(V_{\text{DS}}I_{\text{DS}})$$

(2.1.3.1)

$T_{Jmax}$  is the maximum allowed junction temperature,  $T_C$  is the temperature of the case and  $R_{thJC}$  is the thermal resistance of the junction-case and is a measure of the difficulty in removing the heat from the junction to the case region. In fact, the die is housed in a suitable package and the operating temperature of the latter is different from the internal temperature. The FBSOA of the power MOSFETs is assessed by setting the ambient temperature, generally 25°C, and fixing the V<sub>DS</sub>. The maximum allowed current can be obtained as:

$$I_{\rm DS} = \frac{\Delta T_{\rm max}}{V_{\rm DS} R_{\rm thJC}}$$

(2.1.3.2)

If the device works in switching mode instead of DC, it is necessary to introduce the junctioncase thermal impedance and Eq. (2.1.3.2) can be rewritten as  $(Z_{thJC}$  is the thermal impedance):

$$I_{\rm DS} = \frac{\Delta T_{\rm max}}{V_{\rm DS} \, Z_{\rm thJC}} \tag{2.1.3.3}$$

$Z_{thJC}$  is lower than the  $R_{thJC}$  and its value decreases as the stress time decreases. Under these operating conditions, the shorter the time the device remains on, the greater the maximum power that can be dissipated (see operating regions E and F in figure 2.1.3.1b). In case the time in which the device is switched on is very small, the FBSOA becomes equal to RBSOA. In region D, the device works completely in the on state, thus, once the V<sub>DS</sub> is fixed, the maximum current that can pass through the device is equal to:

$$I_{\rm DS} = \frac{V_{\rm DS}}{R_{\rm DSON}} \tag{2.1.3.4}$$

It is important to underline that the maximum allowable limits of the current, applied voltage and power dissipation are defined as the maximum ratings and that none of these values can be exceeded if the device is to work for a long time and in reliable conditions. These maximum ratings strongly depends on the materials used, structures, the design rules, the assembly techniques and processes and, in some cases, the application conditions as well as the operating temperatures. For example, the rated current can be established as the value at which the junction temperature does not exceed the maximum allowed value or at that value for which the wires that connect the die to the package do not evaporate. The maximum allowable junction temperature depends on the quality of the materials used, also considering that the higher the junction temperature, the higher the deterioration rate and, thus, the shorter the life of the device.

Figure 2.1.3.1: SOA of power MOSFETs: a) RBSOA; b) FBSOA.

It is also important to highlight that the area of the real FBSOA is lower than theoretical one because when the device works in saturation mode it can be subjected to the phenomenon of thermal runaway due to an electrothermal instability mechanism between current and temperature [131] (see figure 2.1.3.1b). In fact, when the operating temperature increases, even if the mobility of the carriers decrease, the V<sub>th</sub> decreases and the I<sub>DS</sub> could increase until a failure occurs. The normalized increase of the I<sub>DS</sub> as function of T can be obtained by:

$$\frac{1}{I_{DSsat}} \frac{\partial I_{DSsat}}{\partial T} = \frac{2}{V_{GS} - V_{th}} \left| \frac{\partial V_{th}}{\partial T} \right| - \frac{1}{\mu_n} \left| \frac{\partial \mu_n}{\partial T} \right|$$

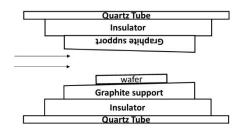

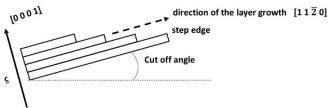

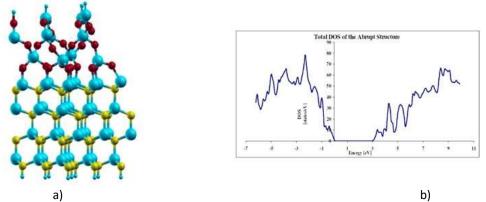

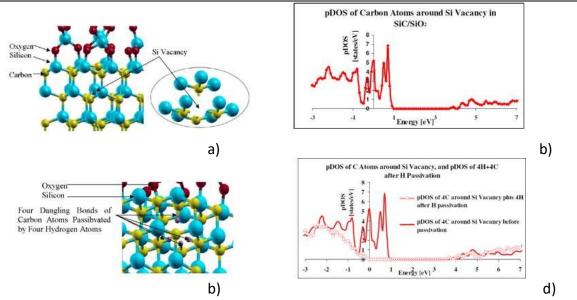

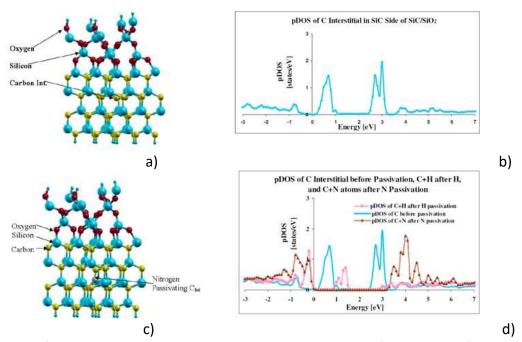

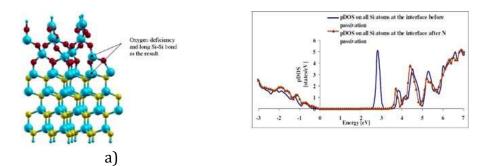

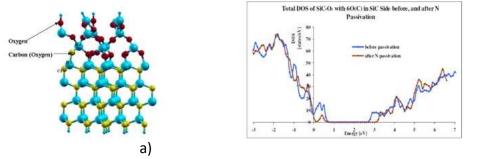

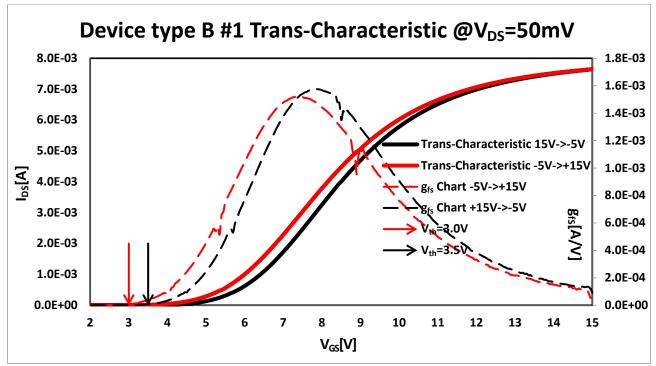

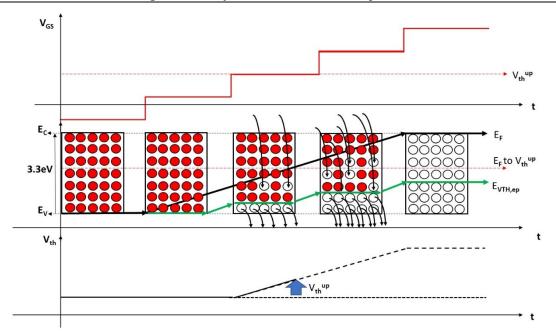

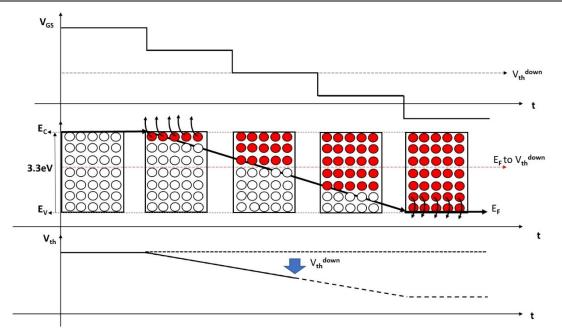

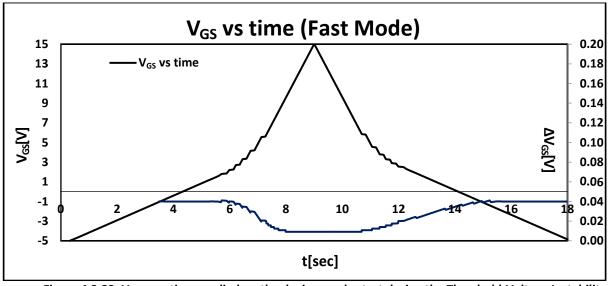

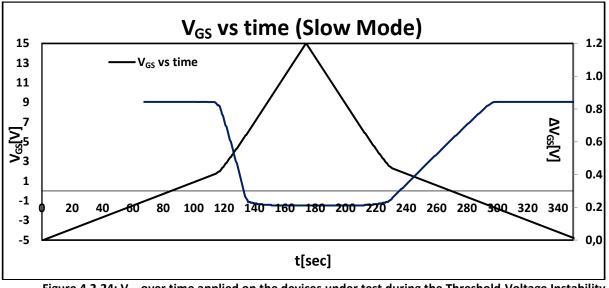

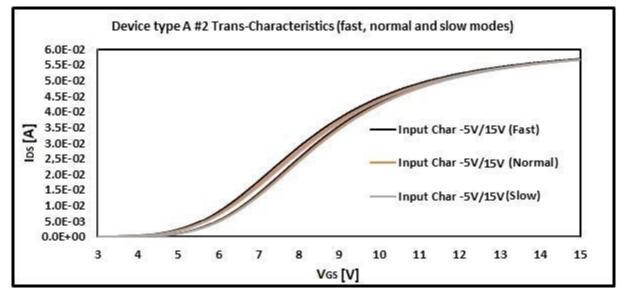

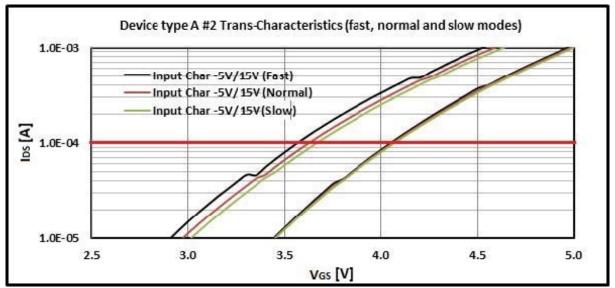

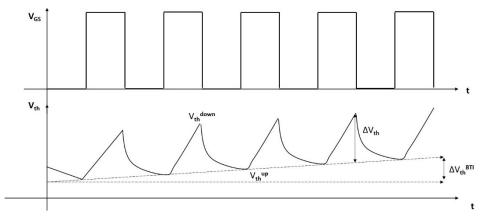

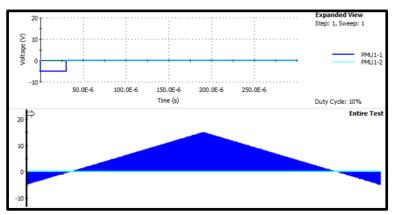

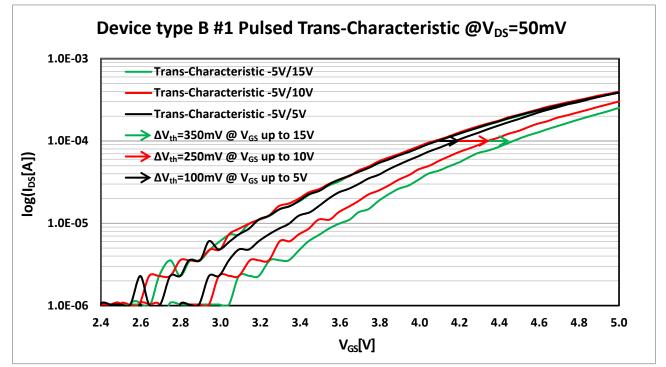

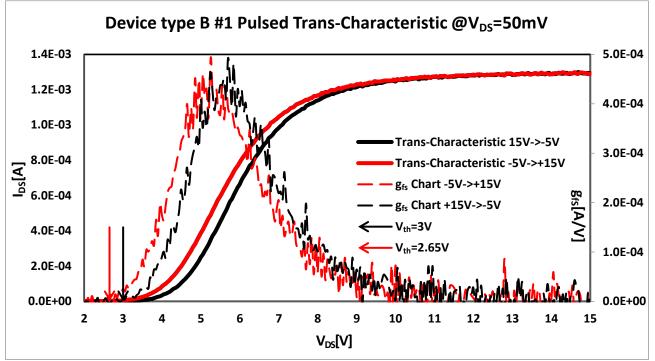

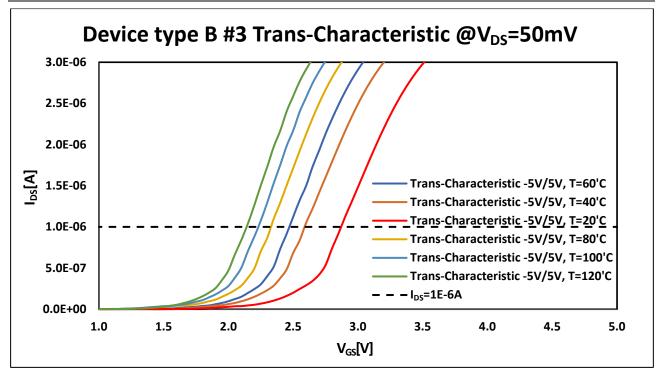

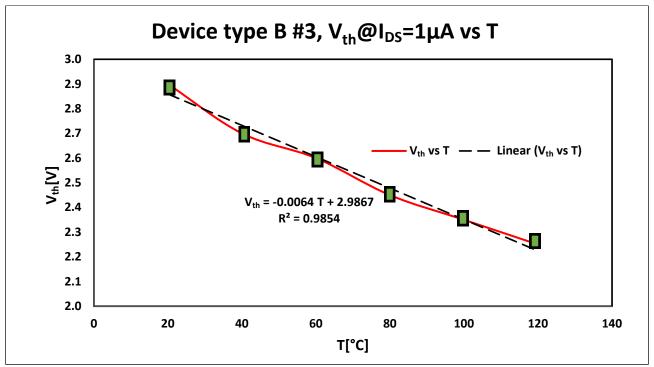

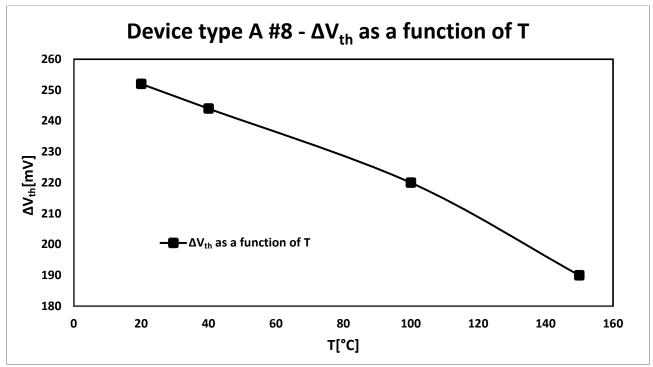

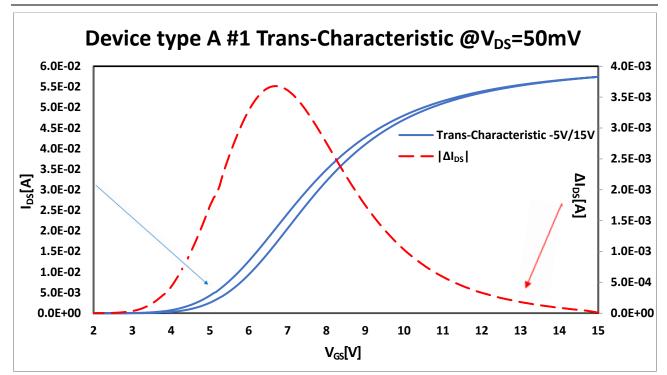

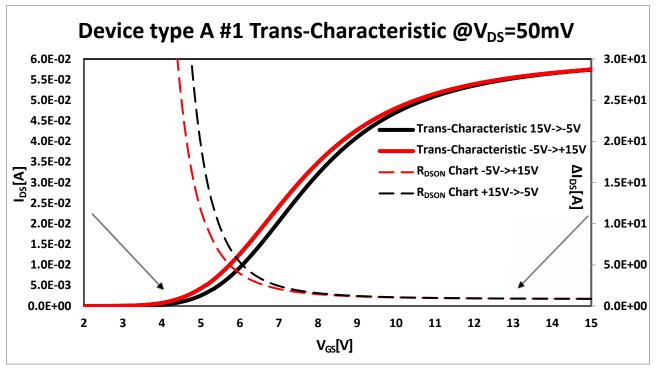

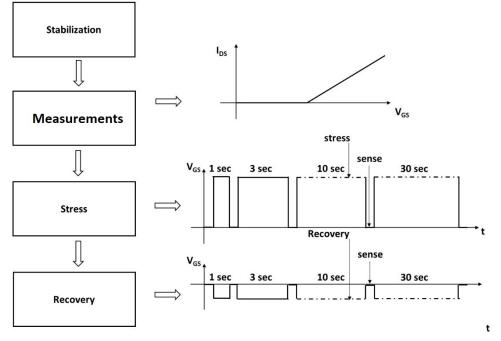

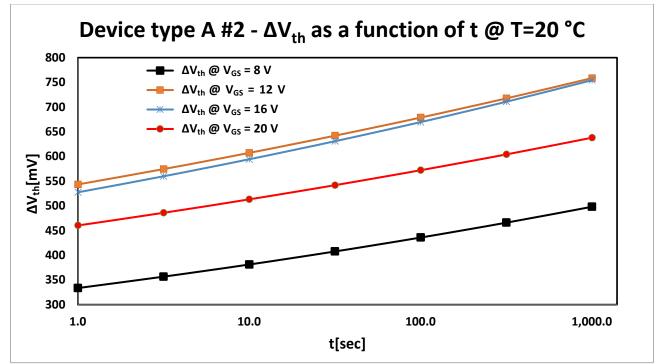

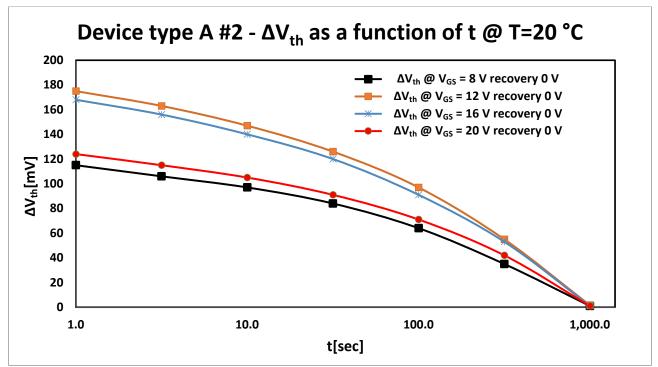

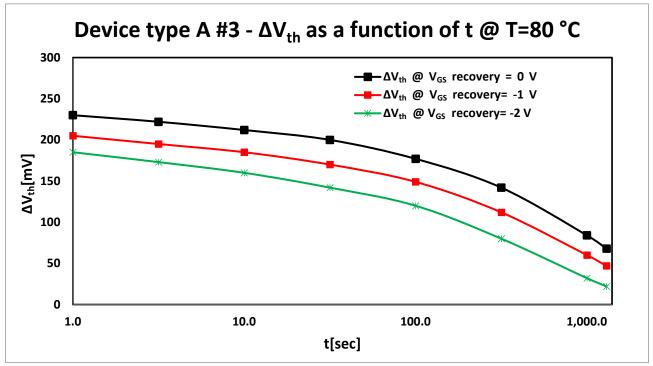

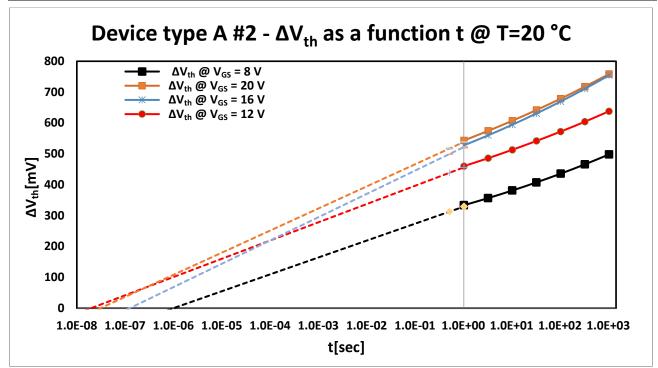

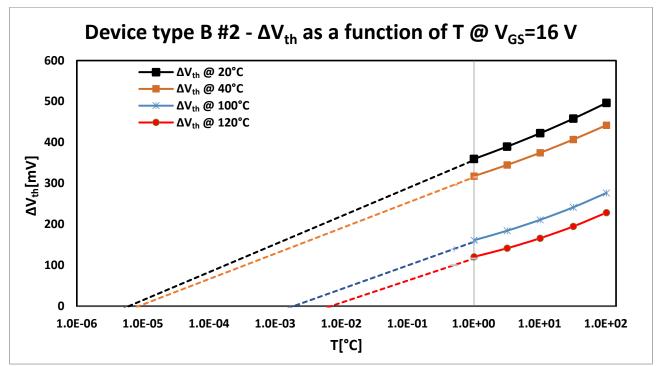

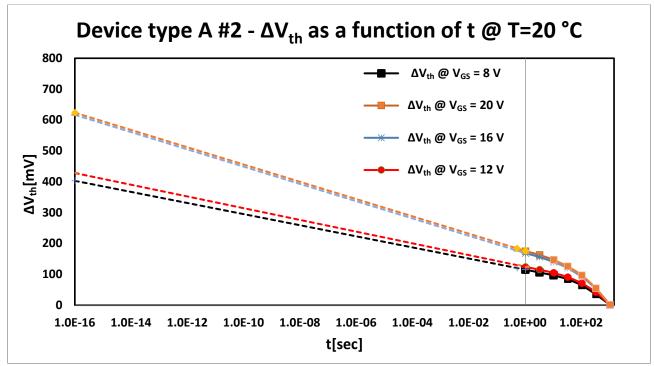

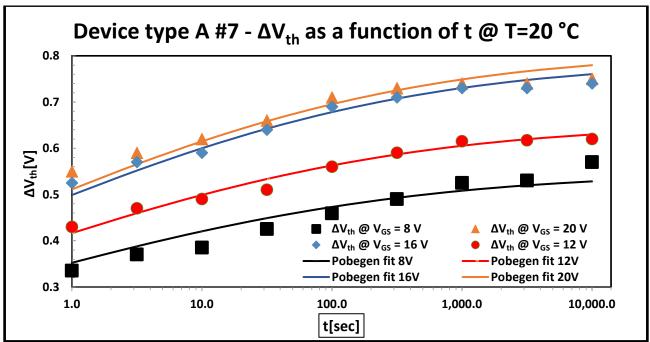

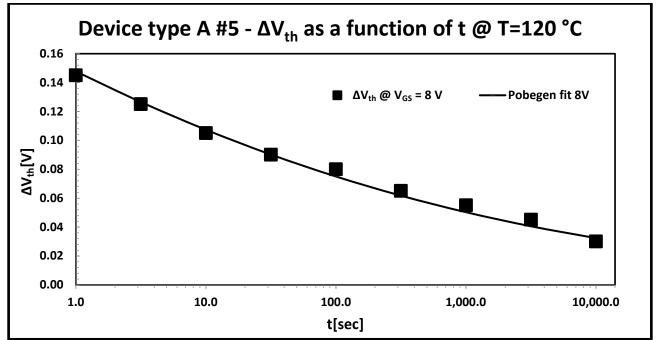

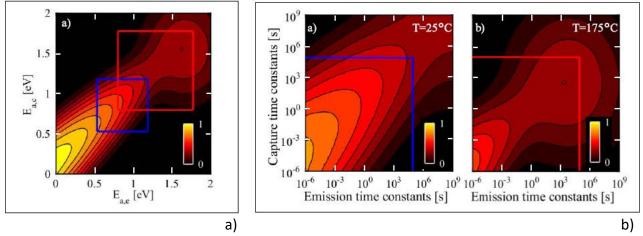

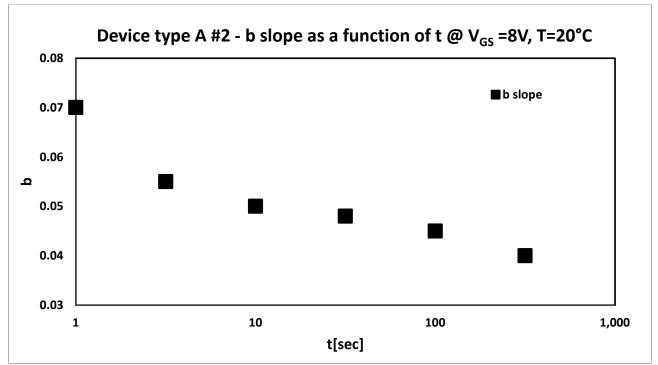

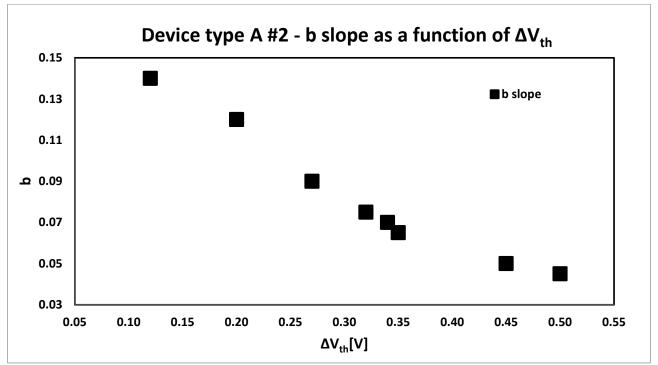

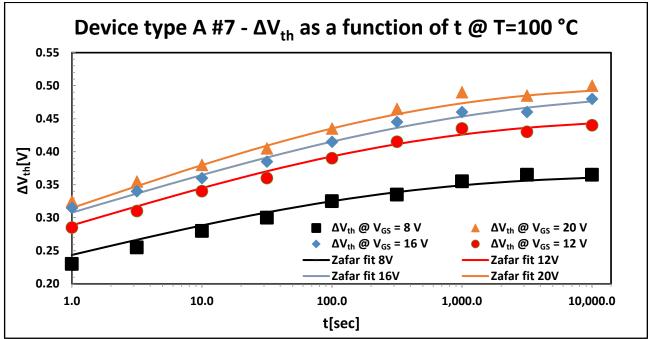

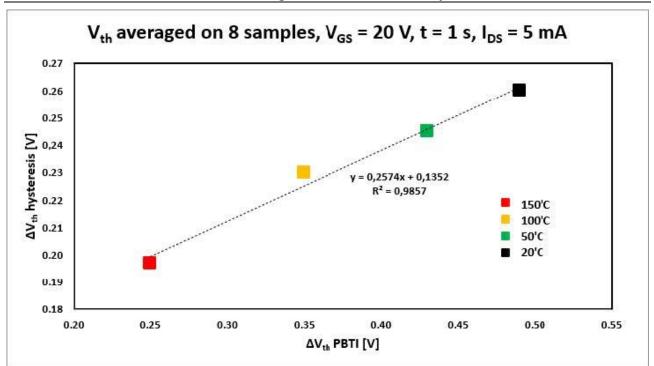

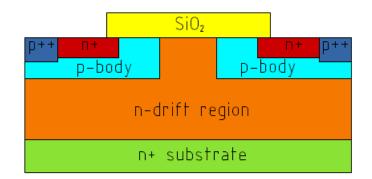

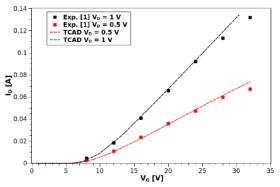

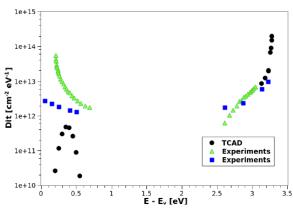

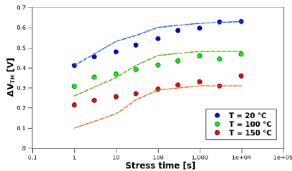

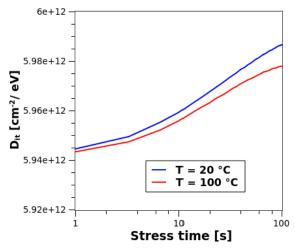

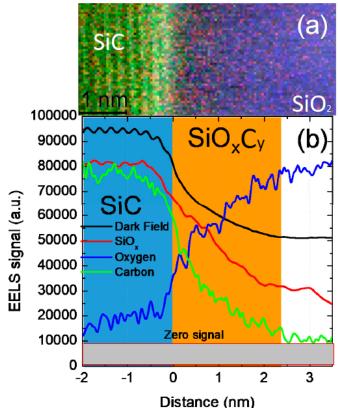

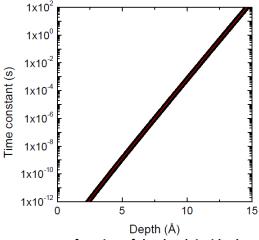

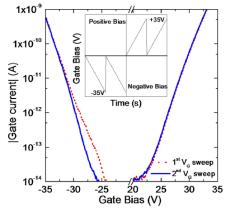

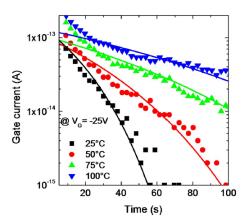

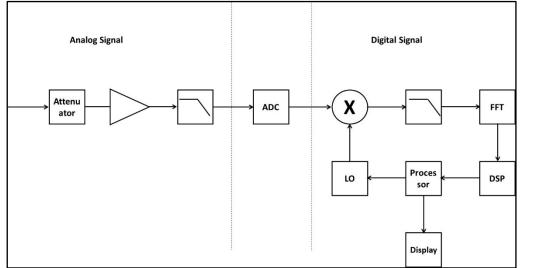

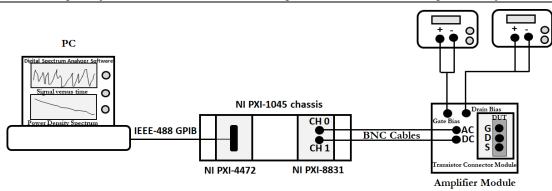

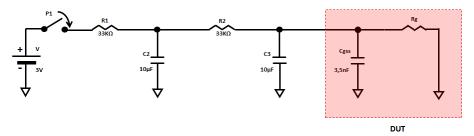

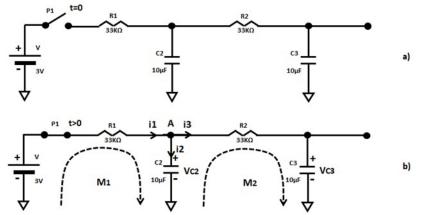

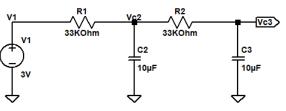

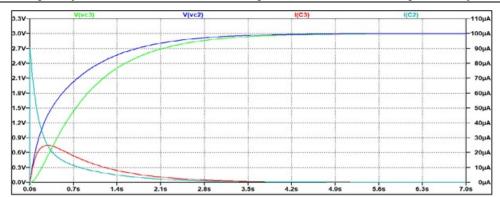

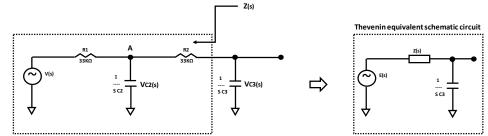

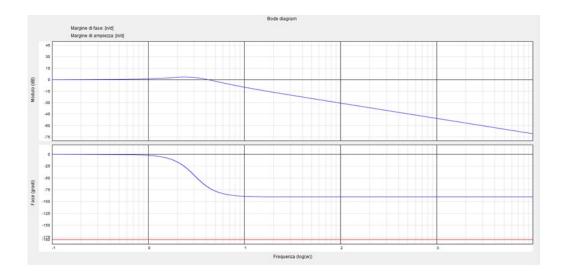

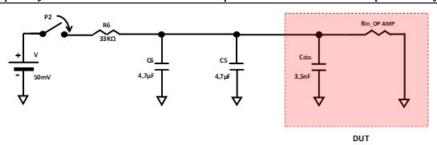

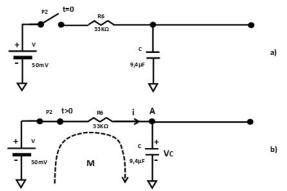

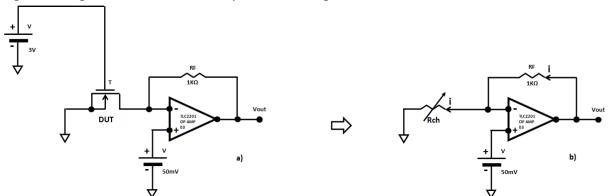

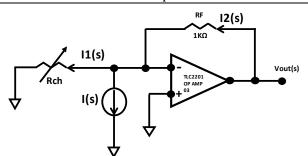

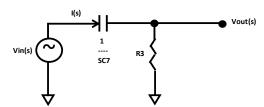

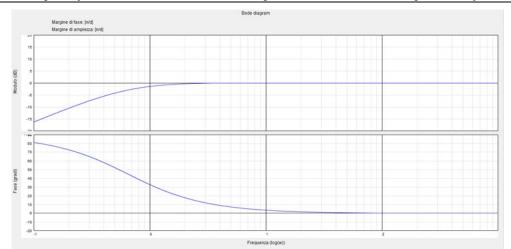

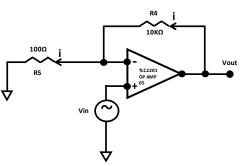

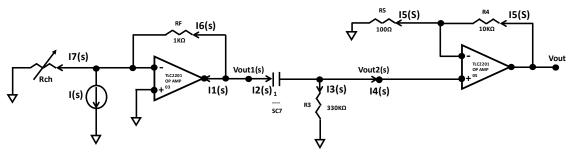

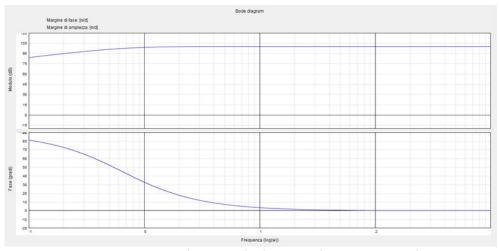

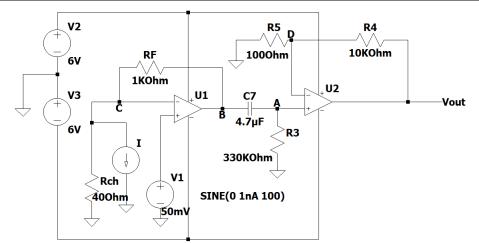

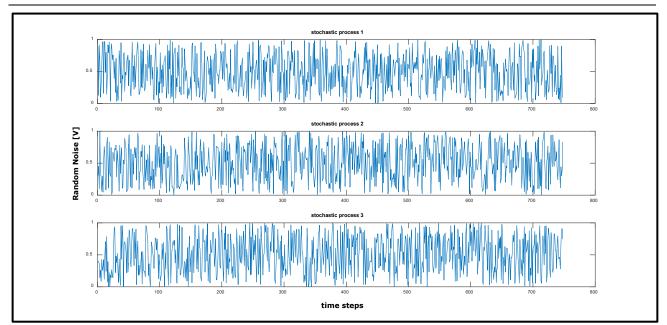

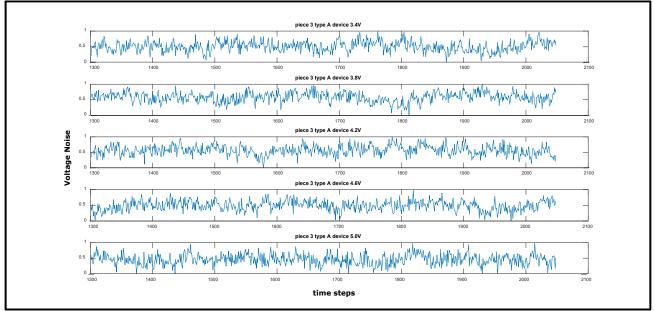

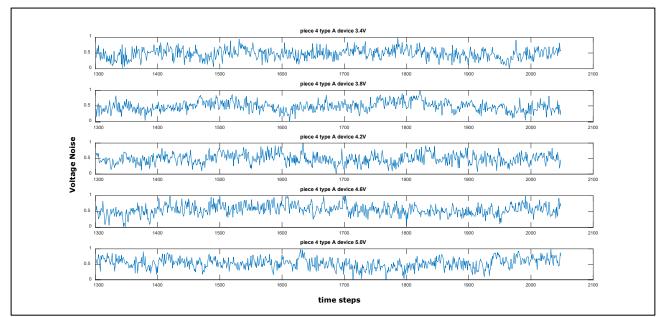

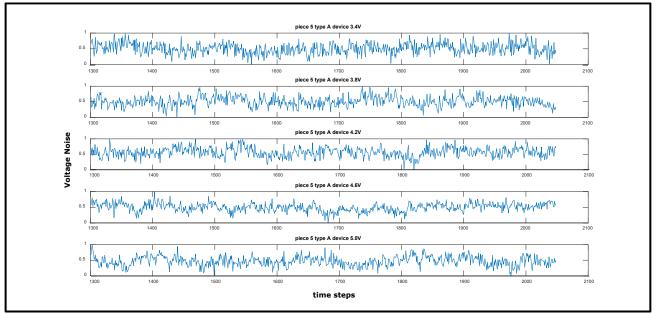

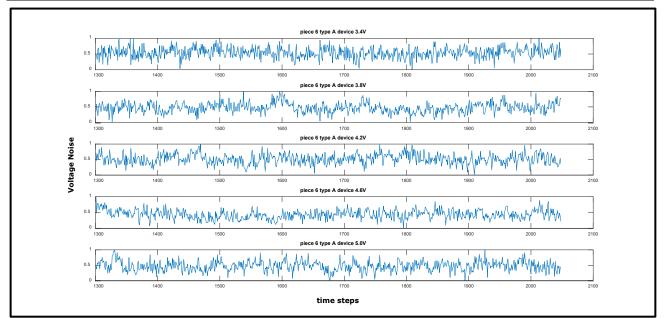

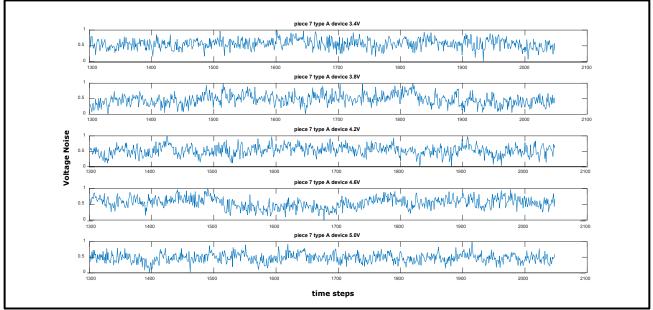

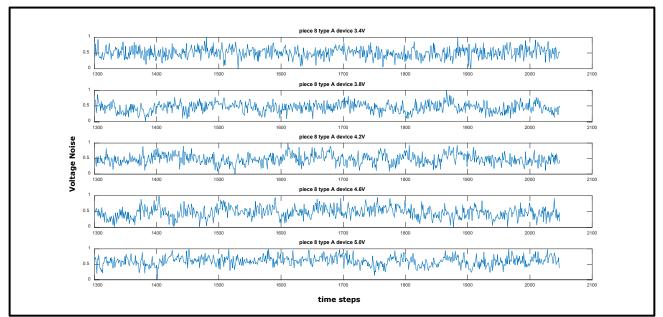

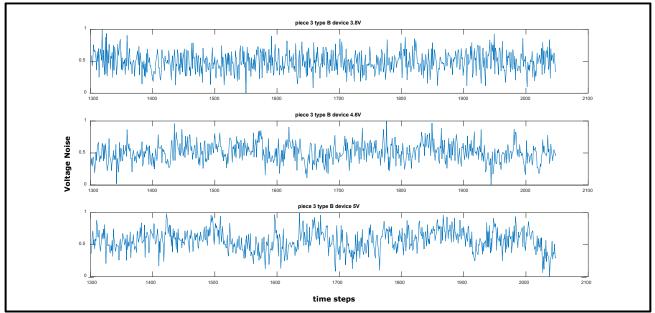

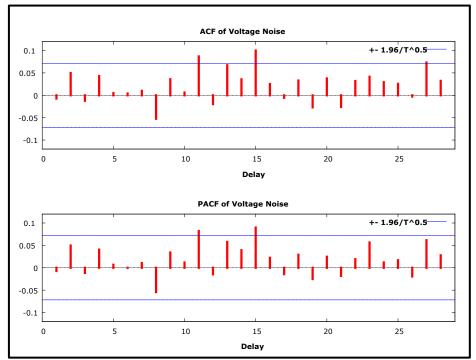

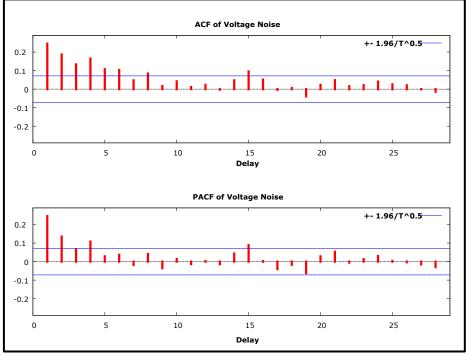

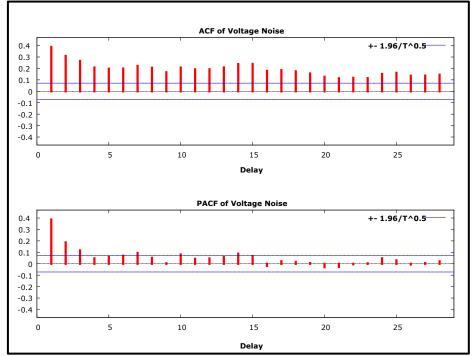

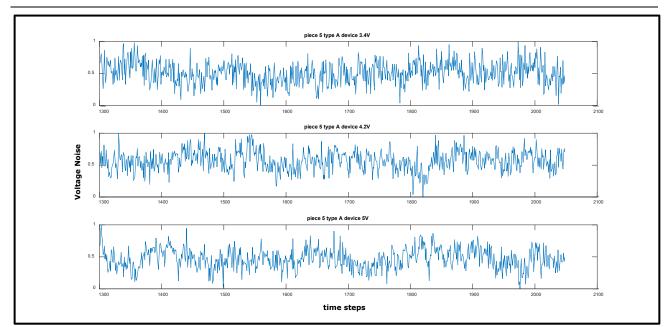

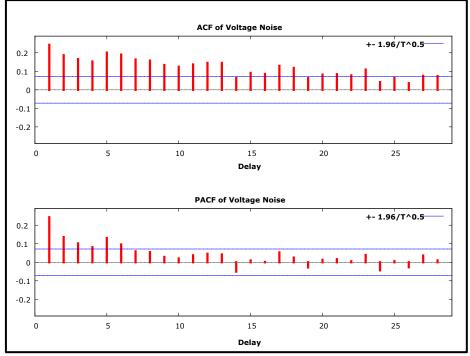

(2.1.3.5)