UNIVERSITÀ DELLA CALABRIA

Dipartimento di Elettronica, Informatica e Sistemistica

Dottorato di Ricerca in Ingegneria dei Sistemi e Informatica XX ciclo

Tesi di Dottorato

# Scheduling Techniques In High-Speed Packet Switches

# Alessandra Scicchitano

# UNIVERSITÀ DELLA CALABRIA

Dipartimento di Elettronica, Informatica e Sistemistica

Dottorato di Ricerca in Ingegneria dei Sistemi e Informatica XX ciclo

# Tesi di Dottorato

# Scheduling Techniques in High – Speed Packet Switches

Alessandra Scicchitano Alessandre Sciechtono

Coordinatore Prof. Domenico Talia

L

Supervisori Prof. Andrea Bianco Judicebranes Prof. Antonella Molinaro Judonelle Molinaro

DEIS

$\mbox{DEIS}$  – Dipartimento di Elettronica, Informatica e Sistemi<br/>stica Novembre 2007

Settore Scientifico Disciplinare: ING-INF/05

Ad Andrea ed alla mia famiglia

# Prefazione

Packet switches are at the heart of modern communication networks. Initially deployed for local- and wide-area computer networking, they are now being used in different contexts, such as interconnection networks for High-Performance Computing (HPC), Storage Area Networks (SANs) and Systemson-Chip (SoC) communication. Each application domain, however, has particular requirements in terms of bandwidth, latency, scalability and delivery guarantee. These requirements must be carefully taken into account and have a major impact on the design of the switch.

We propose novel scheduling techniques that enable the construction of distributed (multi-chip) schedulers for large crossbars, develop a scheme for integrated scheduling of unicast and multicast traffic and study flow-control mechanisms that allow switches to achieve lossless behavior while providing fine-grained control of active flows. We also present a comparison between synchronous and asyncronous systems showing that asynchronous switching seems a competitive solution with respect to the more traditional synchronous approach.

November 2007

Rende, Alessandra Scicchitano

# Indice

| 1        | <b>Int</b><br>1.1<br>1.2<br>1.3 | roductiongBackgroundgContributions10Outline of the Thesis10      | )<br>) |

|----------|---------------------------------|------------------------------------------------------------------|--------|

| <b>2</b> | Pac                             | ket Switch                                                       | 3      |

|          | 2.1                             | General Architecture                                             | 3      |

|          |                                 | 2.1.1 Switching Fabric 14                                        | 1      |

|          | 2.2                             | · · · · · · · · · · · · · · · · · · ·                            | 3      |

|          | 2.3                             | Buffering Strategies 17                                          | 7      |

|          |                                 | 2.3.1 Output-queued (OQ) 17                                      | 7      |

|          |                                 | 2.3.2 Input-queued (IQ) 18                                       | 3      |

|          |                                 | 2.3.3 IQ switches with Virtual Output Queueing (VOQ) $\ldots$ 19 | )      |

|          |                                 | 2.3.4 Combined Input-Output-Queued (CIOQ) Switches 21            | Ĺ      |

|          | 2.4                             |                                                                  | 2      |

|          |                                 | 2.4.1 Optimal Scheduling Algorithm 22                            | 2      |

|          |                                 | 2.4.2 Parallel Iterative Matching Algorithms 22                  | -      |

|          |                                 | 2.4.3 Sequential Matching Algorithms 25                          |        |

|          | 2.5                             | Scheduling Multicast Traffic in IQ Switches                      | -      |

|          |                                 | 2.5.1 Queueing                                                   | -      |

|          |                                 | 2.5.2 Scheduling                                                 | 7      |

# Parte I A Switching Architecture for Synchronous IQ Switch

| 3 | <b>B</b> Distributed Implementation of Crossbar Schedulers |                                 |    |

|---|------------------------------------------------------------|---------------------------------|----|

|   | 3.1                                                        | Introduction                    | 31 |

|   | 3.2                                                        | Two- vs. three-phase algorithms | 31 |

|   | 3.3                                                        | Round Trip Time Latencies       | 32 |

|   | 3.4                                                        | Multi-chip implementation       | 33 |

6 Indice

| 4 | Dis | tributed Scheduler under Unicast Traffic Conditions      | 35 |

|---|-----|----------------------------------------------------------|----|

|   | 4.1 | Scheduling algorithms with RTT latencies                 | 35 |

|   | 4.2 | Synchronous Round Robin                                  | 36 |

|   | 4.3 | Performance results                                      |    |

| 5 | Dis | tributed Scheduler under Multicast Traffic Conditions    | 41 |

|   | 5.1 | Multicast scheduling algorithms                          | 41 |

|   | 5.2 | Improved Multicast Round Robin                           | 42 |

|   | 5.3 | Performance results                                      | 43 |

| 6 | Dis | tributed Integration of Unicast and Multicast Scheduling | 49 |

|   | 6.1 | Introduction                                             | 49 |

|   | 6.2 | Frame Integration                                        | 50 |

|   | 6.3 | Description of Scheduler                                 | 50 |

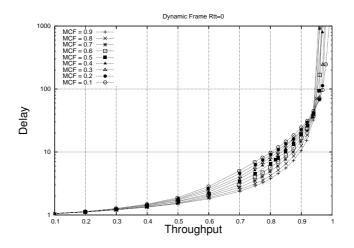

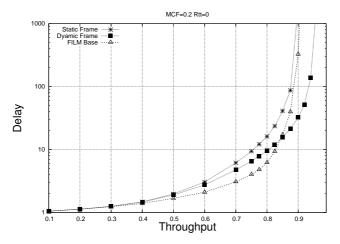

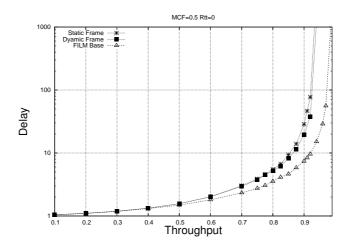

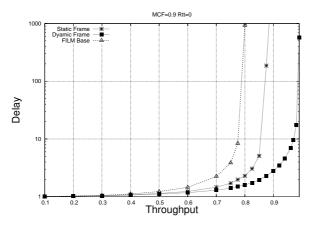

|   | 6.4 | Dynamic Frame                                            |    |

|   | 6.5 | Simulation Result                                        |    |

# Parte II A Switching Architecture for Asynchronous SANs

| 7 |     | roduction to Storage Area Networks                     |    |

|---|-----|--------------------------------------------------------|----|

|   | 7.1 | Storage Area Networks                                  |    |

|   | 7.2 | Networking Technologies for SANs                       | 65 |

|   |     | 7.2.1 Fibre Channel                                    | 65 |

|   |     | 7.2.2 Credit-based flow control                        | 66 |

| 8 | The | Switching Architecture                                 | 69 |

|   | 8.1 | System Overview                                        | 69 |

|   | 8.2 | Line-cards                                             | 70 |

|   | 8.3 | Switching fabric                                       | 70 |

|   |     | 8.3.1 Improvement of multicast scheduling              | 71 |

|   | 8.4 | Control mechanisms for lossless delivery               | 73 |

| 9 | Per | formance Results                                       | 75 |

|   | 9.1 | Performance results under multicast traffic conditions | 75 |

# Parte III Synchronous vs Asynchronous Switching

| 10 | Synchronous versus Asynchronous under Multicast Traffic . | 83 |

|----|-----------------------------------------------------------|----|

|    | 10.1 Introduction                                         | 83 |

|    | 10.2 System Model                                         | 84 |

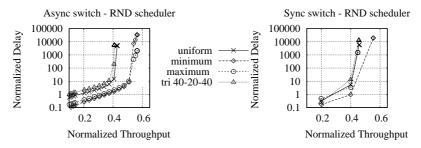

|    | 10.3 Performance results                                  | 86 |

| Indice | 7 |  |

|--------|---|--|

| Par  | Parte IV Conclusion    |    |  |  |  |

|------|------------------------|----|--|--|--|

| 11   | Conclusion             | 93 |  |  |  |

| Rife | erimenti bibliografici | 95 |  |  |  |

# Introduction

#### 1.1 Background

The history of packet-switched networks dates back to the '60s, when deployment of the ARPANET, ancestor of the Internet, was initiated. In the '90s the Internet became a global and ubiquitous networking infrastructure, used for business, entertainment and scientific purposes. Since then, the bandwidth demand of the Internet community has been steadily increasing at exponential rates. To satisfy it, researchers and engineers have studied extensively the design of high-performance switching fabrics, that are at the heart of Internet routers. Today's commercial Internet routers offer aggregate bandwidths on the order of terabits per second and employ sophisticated algorithms for packet buffering, processing and scheduling.

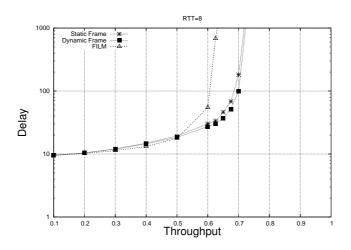

The success of this technology has led researchers to investigate its usage in other domains, where the communication subsystem has become a primary performance bottleneck. Packet switching is being used to build interconnection networks for High-Performance Computing (HPC) systems, where a large number of computing nodes and memory banks must be interconnected. It is replacing the traditional bus-based interconnection between servers and storage devices, giving birth to Storage Area Networks (SANs).

While the benefits of using packet switching in these domains have long been recognized, it is important to remember that each of them has its specific set of requirements, significantly different from those typical of computer networks. Table 1.1 summarizes the requirements for packet switches used in computer networks as well as in the two other domains we are considering. The most significant differences are in terms of latency, aggregate bandwidth and delivery guarantee.

Moreover, current technology trends are playing a significant role in the design of packet switches. Issues such as power consumption, chip I/O bandwidth limitations and packaging constraints are becoming primary concerns for designers.

#### 10 1 Introduction

|            | IP Routers        | Fibre Channel            | HPC Interconnects    |

|------------|-------------------|--------------------------|----------------------|

|            |                   | SAN Switches             |                      |

| Throughput | Very Important    | Very Important           | Moderately Important |

| Latency    | Not Important     | Moderately Important     | Very Important       |

| Delivery   | Can Tolerate      | Losses not               | Losses not           |

| Guarantee  | Small Losses      | Acceptable               | Acceptable           |

| Line Rate/ | $< 10 { m ~Gb/s}$ | $< 10 { m ~Gb/s}$        | $\geq$ 40 Gb/s       |

| Port Count | $\sim$ 100 ports  | $\sim 100 \text{ ports}$ | $\sim$ 1000 ports    |

Tabella 1.1. Requirements of domain-specific interconnection networks.

# 1.2 Contributions

In this thesis we present new scheduling algorithms, aimed at distributed switch implementation and Storage Area Networks respectively. We discuss how the specific requirements of the respective domains and current technology trends have influenced the design. More importantly, we present some of the architectural innovations that allow them to satisfy the demanding needs of their operating environments.

In Part I we study the distributed implementation of a crossbar scheduler, considering the effect of big latencies on its performance. Referring to this, we present new scheduling algorithms, both for unicast and multicast, that achieve a level of performance that is close to that of a single-chip implementation.

In Part II we discuss the performance of a Storage Area Network under multicast traffic conditions. The architecture presents a number of important features, such as an asynchronous design and the presence of a central arbiter that allow the switch to achieve lossless behavior and isolate congesting flows.

Finally in Part III, asynchronous and synchronous switch architectures are compared under multicast traffic.

### 1.3 Outline of the Thesis

The thesis is organized as follows:

**Chapter 2** introduces basic concepts and the terminology used in the rest of the thesis. It provides an overview of switching architectures and a brief survey of scheduling algorithms.

**Chapter 3** introduces the problem of big latencies for interconnections in multichip implementation.

**Chapter 4** is devoted to the specific problem in unicast scenario: how to build schedulers for large crossbars using multiple chips and overcoming the delay and I/O bandwidth limitations caused by distribution.

**Chapter 5** described how to solve the same problem but in a multicast scenario.

**Chapter 6** addresses the problem of scheduling unicast and multicast traffic concurrently over a single fabric, achieving high overall performance and providing fairness guarantees.

**Chapter 7** opens Part II of the thesis, describing the evolution of the server-storage interface and illustrating how Storage Area Networks improve the organization of storage resources.

**Chapter 8** introduces the switching architecture for SANs, focusing in particular on the mechanisms used to achieve loss-free operation and isolate congesting flows.

**Chapter 9** contains a simulation-based study of system performance under multicast traffic, analyzing the effects of system parameters (buffer sizes, fabric and link speed-up) and traffic characteristics (uniformity, packet size distribution).

**Chapter 10** studies differences between synchronous and asynchronous performance under multicast traffic.

Chapter 11 draws conclusions of the thesis.

In this chapter we introduce the basic concepts and the terminology used in the rest of the thesis. We first present the general architecture of a packet switch and discuss the main distinguishing feature: buffer placement. After an overview of output-queued (OQ), input-queued (IQ) and combined inputoutput-queued (CIOQ) switches, we focus on the problem of scheduling unicast and multicast traffic in IQ switches. We provide a survey of the most popular scheduling algorithms and discuss their characteristics in terms of performance and complexity.

Packet switching is a broad field, which has been studied extensively for decades. A comprehensive treatment of the topic can be found in [1], [2] and [3].

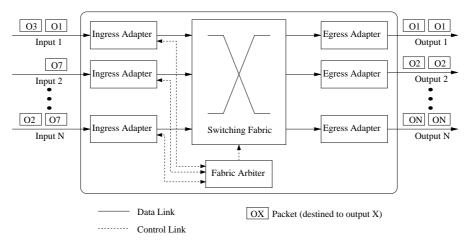

## 2.1 General Architecture

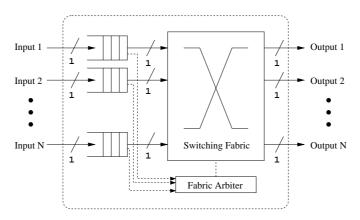

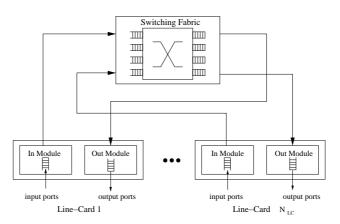

A packet switch is a network device that receives packets on *input ports* and forwards them on the appropriate *output ports*. Figure 2.1 shows the architecture of a packet switch with N input/output ports. Packets are received on an input port and enter an *ingress adapter*, where they are stored (if necessary) and processed. Processing may include look-up of the destination port, recalculation of header fields (TTL, CRC, etc.) and filtering. Packets are then transmitted through the *switching fabric* and reach the *egress adapters*, where they are stored (if necessary) and properties only on fixed-size data units, variable-size packets have to be segmented on the ingress adapter and reassembled on the egress adapter. Usually an ingress adapter is coupled to an egress adapter and they physically reside on a single board called *linecard* that can host multiple bi-directional ports.

A switch is *synchronous* if the linecards and the fabric are coordinated by mean of global clock signal and all ingress adapters start cell transmission at the same time. If the switch is *asynchronous*, on the contrary, the linecards

Figura 2.1. General architecture of a packet switch.

and the fabric work on independent clock domains and transmission from different ingress adapters is not coordinated. In general synchronous switches internally operate on fixed-size cells, whereas asynchronous switches may natively support variable-size packets. Synchronous architectures are more popular because synchronicity simplifies many aspects of the design and implementation of the device. However, asynchronous switches have advantages as well, so they are being actively researched [4, 5, 6]. In the rest of this chapter we will implicitly refer to synchronous, cell-based switches.

#### 2.1.1 Switching Fabric

The switching fabric sets up connections between ingress and egress adapters. It is *non-blocking* if a connection between an idle input and an idle output can always be set-up, regardless of which other connections have already been established. This is a very desirable property, because it helps the switch in forwarding multiple packets concurrently, thus increasing throughput and reducing latency.

The fabric may run at a higher data rate than the linecards; in this case the ratio between the data rate of the fabric ports and that of the switch ports is called *speed-up*. For example, in a synchronous switch with speed-up two, at every time slot ingress/egress adapters can transmit/receive two cells to/from the fabric. When speed-up is used, the egress adapters can receive cells from the fabric at a higher rate than they can transmit on the output links, so they need buffers to temporarily store cells in excess. The term speed-up generally refers to the case in which both input and output fabric ports run faster than the switch ports; however, it is possible to have output speed-up only, i.e. to have only fabric output ports run at a higher data rate. Speed-up on the fabric inputs only is possible but has no practical use.

#### Crossbar

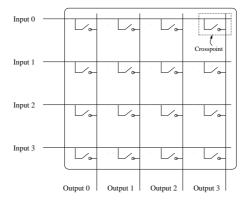

Figura 2.2. A  $4 \times 4$  crossbar.

The crossbar is a very simple fabric that directly connects n inputs to m outputs, without intermediate stages. From a conceptual point of view, it is composed by n + m lines, one for each input and one for each output, and  $n \times m$  crosspoints, arranged as depicted in Figure 2.2. Input i is connected to output j if crosspoint (i, j) is closed.

Every output can be connected to only one input at a time, i.e. at most one crosspoint can be closed on a column. However, one input can be connected to multiple outputs at the same time by closing the corresponding crosspoints on the input row. In this case the signal at the input port is replicated to all the outputs for which the crosspoint is closed. The fabric has intrinsic support for *multicast* (one-to-many) communication. The crossbar is obviously non-blocking: an idle input (output) has all crosspoints its row (column) open, thus it is enough to close the crosspoint at the intersection to connect them.

The simplicity of the crossbar and its non-blocking property make it a very popular choice for packet switches. The main drawback is its intrinsic quadratic complexity, due to the presence of  $n \times m$  crosspoints. Crossbars implemented on a single chip may also be limited by the amount of I/O signals that must be mapped to chip pins. However, it is possible to build a large multi-chip crossbar by properly interconnecting smaller single-chip ones [7]. The complexity in terms of gates remains quadratic.

# 2.2 Traffic conditions for a packet switch

The arrival of packets at the switch inputs can be modeled with a discretetime stochastic process. At every timeslot at most one fixed-size data unit, called *cell* can arrive on each input. Variable-size packets can be considered as "bursts" of cells received at the same input in subsequent timeslots and directed to the same output.

We denote with  $\lambda_{ij}$  the average arrival rate on input *i* of cells directed to output *j*, normalized to the input/output link speed. The offered load from input *i* is the (normalized) rate at which cells enter the switch on input *i* and is represented by the term  $\sum_{j=1}^{N} \lambda_{ij}$ , where *N* is the number of input/output ports. Conversely, the offered load to output *j* is the (normalized) rate at which cells destined to output *j* enter the switch and is equal to the sum  $\sum_{i=1}^{N} \lambda_{ij}$ .

Traffic is *admissible* if no input/output links are overloaded, i.e. if the arrival rate at the inputs and the offered load to the outputs are less than or equal to the capacity of the input/output links. Formally, the admissibility conditions can be stated as:

$$\sum_{j=1}^{N} \lambda_{ij} \le 1 \ \forall i = 1, \dots, N$$

$$\sum_{i=1}^{N} \lambda_{ij} \le 1 \ \forall j = 1, \dots, N$$

In these conditions it is theoretically possible for the switch to forward to the outputs all the cells it receives on the inputs in finite time.

Traffic is *uniform* if a cell entering the switch can be directed to any output with equal probability:

$$\lambda_{ij} = 1/N \; \forall \, i, j$$

It is *independent and identically distributed (i.i.d.)*, also called *Bernoulli*, if the probability that a cell arrives at an input in a certain timeslot:

- is identical to and independent from the probability that a cell arrives at the same input in a different timeslot AND

- is independent from the probability that a cell arrives at another input.

The performance of a packet switch is mainly measured in terms of *throughput* and *latency*. Throughput is the (normalized) rate at which the device forwards packets to the outputs, latency is the time taken by a packet to traverse the switch. A switch achieves 100% throughput if it is able to sustain an offered load to all outputs equal to 1, under the hypothesis that traffic is admissible.

#### Multicast traffic

Under unicast traffic conditions, every packet received on input port has direct to just one output port. In multicast traffic, conditions are different. Traffic generated by a single source and directed to multiple destinations is called *multicast*. The set of outputs a multicast cell is destined to is called the *fanout set* and its cardinality the *fanout*<sup>1</sup>. For clarity, we distinguish between the *input cell* that is transmitted to the switching fabric and the *output cells* that are generated by the replication process.

A scheduling discipline is termed *fanout splitting* if it allows partial service of an input cell, i.e. if the associated set of output cells can be transferred to the outputs over multiple timeslots. *No fanout splitting* disciplines, on the contrary, require all the output cells associated to an input cell to be delivered at the outputs in the same timeslot. Fanout splitting offers a clear advantage because it allows the fabric to deliver in every timeslot as many cells as possible to the outputs, at the price of a small increase of implementation complexity.

The *residue* is the set of all output cells that lose contention for output ports in a timeslot and have to be transmitted in subsequent timeslots.

## 2.3 Buffering Strategies

Due to traffic independence, the switch may receive in the same time slot multiple cells directed to the same output. In this case there is a *conflict* between inputs caused by *output contention*. It is not possible to forward one of the contending cells and discard all the other, because the drop rate would be unacceptable for any practical application. Therefore, the switch is endowed with internal buffers to store cells that cannot be transmitted immediately on the output link. The buffering strategy, mainly if the cells are buffered before being transferred through the switching fabric or after, is a major architectural trait and strongly influences performance, scalability and cost of a switch [8].

#### 2.3.1 Output-queued (OQ)

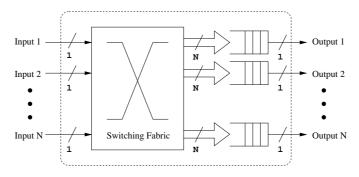

In OQ switches all cells arriving at the fabric inputs are immediately transferred through the switching fabric and stored at the outputs. At every timeslot up to N cells directed to the same output can arrive, so the fabric must operate with speed-up S = N and the memory bandwidth at each egress adapter must be equal to N times the line rate of the switch ports<sup>2</sup> (Figure 2.3).

If multiple cells are buffered at an egress adapter, it is necessary to decide in which order they will be transmitted on the output link. This choice allows the switch to prioritize different flows but does not have an impact on throughput. The OQ switch offers ideal performance, i.e. it achieves 100% throughput under any traffic pattern.

<sup>&</sup>lt;sup>1</sup> The term "fanout" is often used to refer also to the set itself.

$<sup>^2</sup>$  For simplicity we only consider memory *write* bandwidth.

Figura 2.3. An Output-queued switch.

The problem with OQ switches is scalability: fabric speed-up and, above all, egress adapters memory bandwidth, grow linearly with N. As the bandwidth offered by commercial memories is on the same order of link rates, the OQ architecture is a suitable choice only for systems with a small number of ports or low link rates.

## 2.3.2 Input-queued (IQ)

In IQ switches the fabric transfers to the egress adapters only cells that can be transmitted immediately on the output links. Those that are blocked because of output contention are buffered on the ingress adapters (Figure 2.4).

Figura 2.4. Input-queued switch.

This strategy has the following crucial consequences:

- buffers are not needed on the egress adapters, because at every timeslot the cell received from the switching fabric can be transmitted immediately on the output link<sup>3</sup>;

- the switching fabric does not need speed-up, because it must be able to deliver at most one cell per timeslot to each egress adapter;

- the memory bandwidth of the buffers on the ingress adapters is equal to the switch ports line rate, irrespective of N, because at most one cell per timeslot arrives at each input;

- a scheduler is required to decide which among multiple cells contending for the same output will be transferred; the fabric must be configured accordingly.

In the simplest case, arriving cells are stored in FIFO queues and each ingress adapter can only transmit the cell that is at the head of its queue. This constraint leads to a phenomenon called "Head-of-the-line (HOL) Blocking": a cell that is at the head of its input queue and cannot be transferred because of output contention blocks all the other cells in the same queue. Blocked cells may be destined to outputs for which no other input is contending, so the opportunity to transfer a cell is lost. HOL-blocking can severely degrade performance: for large values of N it limits switch throughput to about 58% under uniform i.i.d. traffic [8].

This level of performance is not acceptable, so in the past there have been many attempts to overcome the problem, in general by relaxing the FIFO constraint and allowing the scheduler to consider multiple cells from the same queue. In recent years increased CMOS densities have made feasible a new queueing architecture, called Virtual Output Queueing, that completely eliminates HOL blocking and allows IQ switches to achieve high performance.

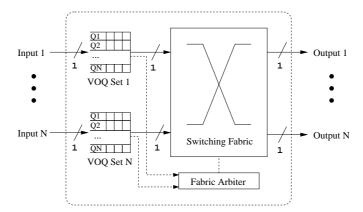

#### 2.3.3 IQ switches with Virtual Output Queueing (VOQ)

Virtual Output Queues (VOQs) are sets of independent FIFO queues, each of which is associated to a specific output [9]. In an IQ switch it is possible to avoid HOL-blocking by deploying a set of N VOQs on each ingress adapter (Figure 2.5). With VOQs, cells destined to different outputs can be served in any order and do not interfere with each other; cells destined to the same output, on the contrary, are served with a FIFO policy to preserve the ordering of packets belonging to the same flow.

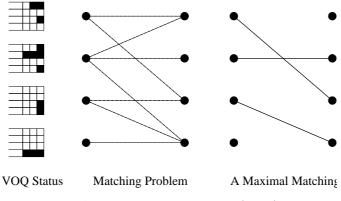

At every timeslot the scheduler must decide which cells to transfer through the switching fabric, subject to the constraints that at most one cell can depart from an ingress adapter and at most one cell can be delivered to an egress adapter. The problem is equivalent to calculating a matching on a bipartite graph, as illustrated in Figure 2.6. Nodes on the left and right side represent

<sup>&</sup>lt;sup>3</sup> We neglect flow-control issues and assume that a cell can always be transmitted on an idle output link.

Figura 2.5. Input-queued switch with Virtual Output Queues.

fabric inputs and outputs respectively; dashed lines (edges) represent nonempty VOQs, i.e. cells that can be chosen for transfer. A *matching* is a set of edges such that each input is connected to at most one output and each output to at most one input.

Figura 2.6. A Bipartite Graph Matching (BGM) problem.

A matching is *maximum size* if it contains the highest number of edges among all valid matchings; it is *maximal* if it is not possible to add new edges without removing previously inserted ones. For instance, the matching shown in Figure 2.6 is maximal but not maximum: no edges can be added, but it is easy to verify that there exists valid matchings with four edges. Edges can be assigned weights, such as the number of cells enqueued in the corresponding VOQ, or the time the cell at the head-of-the-line has been waiting for service. If weights are defined, the *Maximum Weight Matching* (MWM) is the one that maximizes the sum of the weights associated to the edges it contains.

IQ switches with VOQs can achieve 100% throughput under any i.i.d. traffic pattern, but only if very sophisticated scheduling algorithms are employed [10]. These algorithms are in general difficult to implement in fast hardware and too complex to be executed in a single timeslot. However, as we will discuss in Section 2.4, a number of heuristic matching algorithms that achieve satisfactory performance with reasonable complexity have been devised. Therefore input-queueing with VOQs is today the preferred architecture for the construction of large, high-performance packet switches. From this point on, when discussing IQ switches we will implicitly assume that VOQs are present.

#### 2.3.4 Combined Input-Output-Queued (CIOQ) Switches

OQ and IQ switches represent two diametrically opposing points in the tradeoff between speed-up and scheduling complexity. The former employ maximum speed-up but require no scheduling, the latter run without speed-up but need complex schedulers. CIOQ switches (with VOQs) represent an intermediate point: they buffer packets both at the inputs and at the outputs, employ moderate speed-up S ( $1 \le S \le N$ ) and use simpler schedulers.

Early simulation studies of CIOQ switches showed that, under a variety of switch sizes and traffic patterns, a small speed-up (between two and five) leads to performance levels close to those offered by OQ switches. These hints led a number of researchers to analytically investigate the maximum performance achievable by CIOQ switches. Among the many results that were published, these are particularly significant:

- With a speed-up S = 2 and proper scheduling algorithms, a CIOQ switch can exactly *emulate* an OQ switch, for any switch size and under any traffic pattern [11, 12]. "Emulating" means producing exactly the same cell departure process at the outputs given the same cell arrival process at the inputs.

- A CIOQ switch employing any maximal matching algorithm with a speedup of two achieves 100% throughput under any traffic pattern, under the restriction that no input or output is oversubscribed and that the arrival process satisfies the strong law of large numbers [13].

These results prove that with moderate speed-up the performance of an IQ switch can be dramatically improved and that it can even reach the performance of an OQ switch if proper scheduling is used. A small fractional speed-up (S < 2) is also typically used to compensate for various forms of overhead, such as additional headers that must be internally prepended to cells and padding imposed by segmentation [14].

# 2.4 Scheduling Unicast Traffic in IQ Switches

### 2.4.1 Optimal Scheduling Algorithm

The optimal scheduling algorithms for an IQ switch, i.e. the one that maximizes throughput, is the Maximum Weight Matching (MWM), when queue lengths are used as weights [15]. McKeown et al. noted that, with this choice of the weights, specific traffic patterns can lead to permanent starvation of some queues [10]. However, they also proved that 100% throughput is still achieved for any i.i.d. traffic pattern if the ages of HOL cells are used as weights; in this case starvation cannot happen. The most efficient known algorithm for calculating the MWM of a bipartite graph converges in  $O(N^3 \log N)$  time [16]. Despite polynomial complexity, this algorithm is not practical for high-performance packet switches, because it is difficult to implement in fast hardware and cannot be executed in the short duration of a timeslot. For this reason, a number of heuristic algorithms have been developed.

#### 2.4.2 Parallel Iterative Matching Algorithms

Parallel iterative matching algorithms are the most popular class of heuristic matching algorithms. All inputs in parallel try to match themselves to one output by using a request-grant protocol. VOQ selection at the inputs and contention resolution at the outputs are performed by *arbiters* (also called *selectors*) using round-robin or random criteria. The process is iterated multiple times, until a maximal matching is obtained or the maximum number of iterations is reached. On average these algorithms converge in  $\log_2 N$  iterations, but in the worst case they can take N.

#### $\mathbf{PIM}$

PIM [17] (Parallel Iterative Matching) is one of the first parallel iterative matching algorithms that have been proposed. In every timeslot the following three *phases* are executed and possibly repeated multiple times:

- 1. *Request:* every unmatched input sends a request to every unmatched output for which it has a queued cell.

- 2. *Grant:* every output that has been requested by at least one input *randomly* selects one to grant.

- 3. Accept: if an input receives more than one grant, it selects randomly one to accept.

The main disadvantage of PIM is that it does not perform well, as it achieves only 63% throughput with a single iteration under uniform i.i.d. traffic. Moreover, it employs random selection, which is difficult and expensive to perform at high speed and can cause unfairness under specific traffic patterns [18].

#### $\mathbf{RRM}$

RRM (Round-Robin Matching) [18] addresses some of the drawbacks of PIM by replacing random selection with round-robin. The selection logic at each input and output is composed by a round-robin selector and a pointer. Pointers at the outputs are named *grant pointers*, whereas those at the inputs *accept pointers*.

Every iteration of RRM entails the following three phases:

- 1. *Request:* every unmatched input sends a request to every output for which it has a queued cell.

- 2. Grant: every output that has been requested by at least one input selects one to grant in round-robin order, starting from the position indicated by the grant pointer. The pointer is advanced (modulo N) to one input beyond the one just granted.

- 3. Accept: if an input receives more than one grant it selects one to accept in round-robin order, starting from the position indicated by the accept pointer. The pointer is advanced (modulo N) to one output beyond the one just accepted.

The performance of RRM is very close to that of PIM, so still quite poor.

## *i*-SLIP

*i*-SLIP [19] is a improvement of RRM that, with an apparently minor modification, achieves much higher performance. The three phases are modified as follows:

- 1. *Request:* same as RRM.

- 2. Grant: every output that has been requested by at least one input selects one to grant in round-robin order, starting from the position indicated by the pointer. The pointer is advanced (modulo N) to one input beyond the one just granted *if and only if the released grant is accepted in the accept phase*.

- 3. Accept: same as RRM.

Moreover, the grant and accept pointers are updated only in the first iteration; a detail that is crucial to prevent starvation of any VOQ under any traffic pattern.

*i*-SLIP performs extremely well: under uniform i.i.d. traffic it achieves 100% throughput with a single iteration, because it guarantees *desynchronization* of the grant pointers. When the switch is loaded at 100% and traffic is uniform i.i.d, all VOQs are backlogged. Assume that the grant pointers at multiple outputs point to the same input, i.e. they are *synchronized*. The input receives multiple grants, accepts one and moves the accept pointer. Thanks to the modification of the grant phase, only one of the grant pointers (the one corresponding to the grant that has been accepted) is moved and leaves the

group. For the same reason, at most one new grant pointer can join the group. It is possible to prove that, after a transient period, all grant pointers point to different inputs, regardless of their initial position. A *maximum* matching is produced at every timeslot and 100% throughput is achieved. Desynchronization is preserved as long as all VOQs are non-empty, because all the released grants are accepted and so all the grant pointers move "in lockstep".

Another important feature of *i*-SLIP is that it is fair and starvation free, i.e. it does not favor some flows over others and guarantees that a cell at the head of a VOQ will be served within finite time.

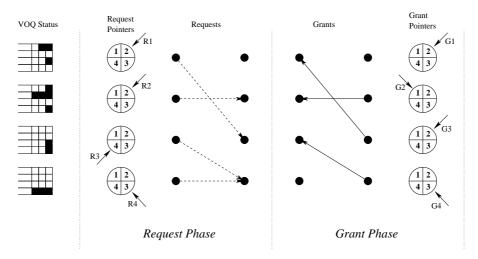

### DRRM

DRRM [20] (Dual Round-Robin Matching) is a further variant of i-SLIP that achieves similar performance with one less phase and less information exchange between the input and the outputs.

The two phases performed in each iteration are:

- 1. Request: every unmatched input selects one unmatched output to request in round-robin order, starting from the position indicated by a request pointer. In the first iteration, the pointer is updated to one position beyond the input just requested (modulo N) if and only if a grant is received in the grant phase.

- 2. Grant: each output that has been requested by at least one input selects one to grant in round-robin order, starting from the position indicated by a grant pointer. In the first iteration the pointer is updated to one position past the input just granted (modulo N).

A grant phase is not required because each input requests only one output, so it can receive at most one grant, which is automatically accepted.

DRRM achieves 100% throughput under uniform i.i.d. traffic because in this situation request pointers (moved only if a grant is received) desynchronize.

Figure 2.7 shows the operation of the DRRM algorithm for a  $4 \times 4$  switch. At the end of the first iteration all pointers (except R4 and G1) are moved forward by one position. As the matching is maximal, it is not necessary to perform additional iterations.

#### FIRM

FIRM [21] is an improvement of *i*-SLIP that achieves lower average latency by favoring FCFS order of arriving cells. It does so by introducing a minor modification in the pointer update rule of the grant phase of *i*-SLIP: in the first iteration, if a grant is not accepted, the grant pointer is moved to the granted input. The authors also show that this modification reduces the maximum waiting time for any request from  $(N-1)^2 + N^2$  to  $N^2$ .

A similar modification has been proposed for DRRM in [22].

Figura 2.7. The behavior of the DRRM algorithm in a sample scenario.

## Weighted Algorithms

As an attempt to approximate the behavior of MWM and improve performance under non-uniform traffic, heuristic iterative weighted algorithms have been developed. Among these are *i*-OCF (Oldest Cell First), *i*-LQF (Longest Queue First) and *i*-LPF (Longest Port First), proposed by Mekkittikul and McKeown [23].

#### 2.4.3 Sequential Matching Algorithms

Sequential scheduling algorithms produce a maximal matching by letting each input add an edge at a time to an initially empty matching.

RPA [24] (Reservation with Pre-emption and Acknowledgement) and RRGS [25] (Round Robin Greedy Scheduler) are examples of sequential matching algorithms. An input receives a partial matching, adds an edge by selecting a free output and passes it on to the next input. Inputs considered first are favored, because they find most outputs still available. To avoid unfairness, the order in which inputs are considered is rotated at every timeslot. These algorithms always produce a maximal matching, are fair and can be pipelined to improve the matching rate. However, they require strong interaction among the inputs and introduce latency at low load when pipelined.

The Wavefront Arbiter [26] (WFA) is another popular sequential arbiter. The status of all the  $N^2$  VOQs of the system is represented in a  $N \times N$  request matrix R:  $R_{i,j} = 1$  if input *i* has a cell destined to output *j*, 0 otherwise. Sets of VOQs that are positioned on a diagonal of the matrix are conflict-free, because

they correspond to cells enqueued at different inputs and destined to different outputs. Hence it is possible to produce a matching by sequentially "sweeping" all the diagonals of the request matrix, excluding input and outputs that have already been matched. WFA is fast, simple and offers good performance; however, it suffers from some minor fairness and implementation issues [7].

### 2.5 Scheduling Multicast Traffic in IQ Switches

In an IQ switch replication can be achieved simply by transmitting cells through the switching fabric multiple times, one for every egress adapter that must be reached. However, the crossbar has intrinsic multicasting capabilities and can replicate a cell to multiple outputs in a single timeslot. A scheduler that takes advantage of this feature can reduce the latency experienced by cells and the load on the fabric input ports, which are occupied for only one timeslot.

In this section we briefly introduce the problem of scheduling multicast traffic and present some of the most popular scheduling algorithms.

### 2.5.1 Queueing

A multicast cell can be destined to any subset of the N outputs, so the number of possible fanout sets is  $2^N - 1$ . Even for moderate values of N it is not practically feasible to provide a dedicated queue to cells with the same fanout set, therefore HOL-blocking cannot be completely eliminated. Indeed, most architectures store cell arriving on an ingress adapter in a single queue and serve them in FIFO order.

To alleviate HOL-blocking, in [27] the authors propose a windowing scheme that allows the scheduler to access any cell in the first L positions of the queue. This scheme offers throughput improvements, but requires randomaccess queues, which are complex to implement. Moreover, it is clearly not effective under bursty traffic.

In [28] and [29] the benefits that can be gained by using a small number of FIFO queues at each ingress adapter are investigated. When multiple queues are present, it is necessary to define a queueing policy. Static queueing policies always enqueue cells with a given fanout in the same queue, whereas dynamic policies may enqueue them in different ones, depending on status parameters such as queue occupancy. Static policies lose effectiveness when few flows are active, because most of the available queues may remain empty, whereas dynamic policies lead to out-of-order delivery.

In [32] maximum switch performance is analyzed, under the hypothesis that a queue is provided for every possible fanout set. The results of this work have great theoretical interest, because they show that an IQ switch is not able to achieve 100% throughput under arbitrary traffic patterns, even if it employs this ideal queueing architecture and the optimal scheduling discipline.

#### 2.5.2 Scheduling

The problem of scheduling multicast traffic in an input-queued switch has been addressed by a number of theoretical studies. In [33] and [34] the performance of various scheduling disciplines (such as random or oldest-cell-first) is analyzed under different assumptions. Work in [35] studies the optimal scheduling policy, obtaining it for switches of limited size (up to three inputs) and deriving some of its properties in the general case.

In [36] the authors take a more practical approach: they specifically target the design of efficient and implementable scheduling algorithms when FIFO queueing is used and fanout splitting allowed. They provide important insight on the problem and propose various solutions with different degrees of performance and complexity. An important observation is that at any timeslot, given a set of requests, all *non-idling* policies (those that serve as many outputs as possible) transmits cells to the same outputs and leave the same residue. What differentiates one policy from the other is residue distribution, i.e. the criteria with which the set of output cells that have lost contention is partitioned among the inputs. A *concentrating* policy assigns the residue to as few inputs as possible. Policies exhibiting this property serve in each timeslot as many HOL cells as possible, helping new cells to advance to the head of the queue. As new cells may be destined to idle outputs, throughput is increased. Actually a proof is given that for a  $2 \times N$  switch a concentrating policy is optimal, but it cannot be extended to switches of arbitrary size.

The first proposed algorithm, called "Concentrate" implements a purely concentrating policy. However, the authors note that the algorithm suffers from fairness issues, as it can permanently starve queues, so they proceed with the design of TATRA, a concentrating algorithm with fairness guarantees. As TATRA is difficult to implement in hardware, they further propose the Weight Based Algorithm (WBA). WBA is a heuristic algorithm that approximates concentrating behavior by favoring cells with small fanout and guarantees fairness by giving priority to older cells. The algorithm works as follows:

- 1. At the beginning of every cell time each input calculates the *weight* of the cell at the head of its queue, based on the age of the cell (the older, the heavier) and the fanout (the larger, the lighter).

- 2. Each input submits a weighted request to all the outputs that it wishes to access.

- 3. Each output independently grants the input with the highest weight; ties are broken randomly.

In the specific implementation shown in the paper, the weight is calculated ad  $W = \alpha A - \phi F$ , where A is the age (expressed in number of timeslots), F is the fanout and  $\alpha$  and  $\phi$  are multiplication factors that allow tuning of the scheduler for performance or fairness. Large  $\alpha$  implies that older cells are strongly favored, improving fairness, while large  $\phi$  penalizes cells with large fanout, exalting the concentrating property and thus improving performance.

Calculations show that a cell has to wait at the head of the queue for no longer than  $(N(\phi/\alpha + 1) - 1)$  timeslots. WBA can be easily implemented in hardware, as reported in the paper.

# A Switching Architecture for Synchronous IQ Switch

# Distributed Implementation of Crossbar Schedulers

# 3.1 Introduction

IQ switches are suited for several application domains, such as traditional routers/switches, SANs (Storage Area Networks), and HPC (High-Performance Computing) interconnects; in most of these application domains, a large number of ports and high line rates are dominant and exceed single-chip implementation limits. Multichip implementation is limited by power density, gate count, pin count, I/O bandwidth and wiring, due to the high degree of connectivity between the input and output selectors [14]. In this thesis we present new scheduling algorithms enabling the construction of schedulers for large switches, while achieving a level of performance that is close to that of a single-chip implementation.

## 3.2 Two- vs. three-phase algorithms

A very popular solution to determine a heuristic matching is to devise parallel, iterative matching algorithms based on a three-phase (request-grant-accept) [19, 21] or two-phase (request-grant) [44, 36, 20] scheme. Iterative matching algorithms can be classified into two- and three-phase algorithms according to the number of steps per iteration. In three-phase algorithms, there are *request*, *grant*, and *accept* steps in every iteration. In the request phase, every input sends a request to *every* output it has at least one cell for. In the grant phase, every output independently selects one request to grant. As these decisions are independent, multiple outputs may grant the same input. Therefore, in the third phase, every input selects one grant to accept. Two-phase algorithms, on the other hand, comprise only a request and a grant phase. In the request phase, every input sends a request to *one* output for which it has at least one cell. In the grant phase, every output independently selects a request to grant. Because every input can receive one grant at maximum, there is no need for an accept phase, i.e., every grant is automatically accepted.

#### 32 3 Distributed Implementation of Crossbar Schedulers

Input and output selection is based on a prioritized round-robin mechanism, i.e., the input (output) selector chooses the first eligible output (input) starting from the position indicated by a *pointer*. The pointer update policy is a crucial characteristic of each algorithm and must be chosen carefully to guarantee performance and fairness. The update policies employed by these algorithms share a common trait: once a connection (corresponding to a VOQ) becomes highest priority, it will be given precedence over the other competing ones until it is established. In i-SLIP this is achieved by having an output grant the same input (in the first iteration) until the grant is accepted. In DRRM, on the contrary, an input will keep requesting the same output (in the first iteration) until it receives a grant. This feature guarantees fairness and leads to *pointer desynchronization* [18], i.e., it assures that under heavy traffic (when all the VOQs are nonempty) each output grants a different input (i-SLIP) or each input requests a different output (DRRM). When this happens, there are no conflicts and a maximum-size matching is produced in every timeslot, leading to 100% throughput.

## 3.3 Round Trip Time Latencies

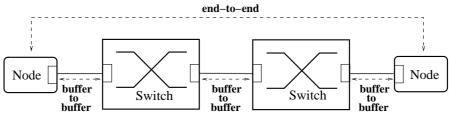

Recently, several researchers have addressed the problem of scheduling algorithms in input queued switches when considering round trip time latencies in the scheduling process. In [38] round trip latencies are introduced by the need of addressing multi-rack implementation in very large switches. Multirack implementation implies that the physical distance between line-cards and the switching fabric is non negligible with respect to the time slot. As such, performance of a centralized scheduler based on the classical iterative threephase (request-grant-accept) scheme are shown to degrade for large physical distances; a solution to cope with this problem is proposed, being based on a differential signalling scheme and on a slight increase of the scheduler complexity, which is assumed to keep track of VOQs state.

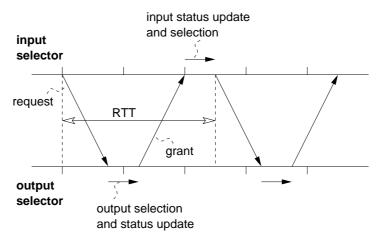

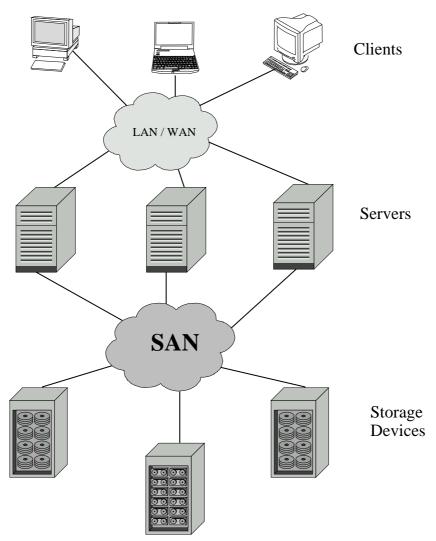

The centralized single-chip implementation of scheduling algorithms is largely dominant; however, scalability problems may arise for very large highspeed switches [39]. When looking at multi-chip implementations, device separation implies that decision taken by input/output selectors belonging to different devices are known only after an inter-chip latency, named RTT (Round Trip Time). As such, as shown in Fig. 3.1, information critical i) to determine the matching, ii) to update the pointers and iii) to issue new requests, is delayed by the inter-chip latency, causing performance degradation. RTTs may be significant with respect to the time slot. Indeed, at high speed the time slot is rather short (13ns at 40Gbit/s for a 64bytes packet) if compared with inter-chip communication latencies which include propagation delays, data serialization and pin sharing which may be required to overcome the I/O pin count limit.

Figura 3.1. Round trip time between input and output selectors.

#### 3.4 Multi-chip implementation

Let us focus on iterative schedulers, based on three-phase or two-phase information exchange among inputs and outputs. These schedulers adopt OSs (Output Selectors) to choose among multiple requests received by inputs and ISs (Input Selectors) to select a proper request to issue in a given time slot and to choose among multiple grants received by OSs. Scheduler distribution over several chips entails partitioning the selectors used to determine a heuristic matching over physically separated devices. In a single-chip implementation, all selectors are tightly coupled and decisions taken at inputs (outputs) are immediately available to outputs (inputs). When dealing with multi-chip implementations, the communication latency between devices implies that algorithms devised to run under the hypothesis of having all the scheduling state information available may not be optimal. Indeed, information needed to update the pointer status or to issue new requests may be known with a delay of some tens of cell time. Performance degradation and loss of fairness were already shown to be a possible problem in this multi-chip scenario.

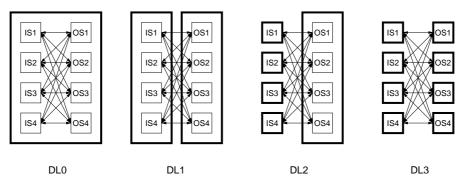

Different levels of selectors distribution could be envisioned, which yield to a different number of physically separated devices, as shown in Fig. 3.2. The first obvious solution to reduce the scheduler complexity, labeled distribution level DL1, is to implement the scheduler in two separate devices, each containing respectively N input and N output selectors. This allows to roughly divide by two the scheduler hardware complexity. Another extreme, labeled distribution level DL3, is to distribute the selectors over 2N separate devices, each device implementing one selector. This is referred to as fully distributed solution, which permits a hardware complexity reduction by a factor of N.

34 3 Distributed Implementation of Crossbar Schedulers

Figura 3.2. Distribution levels of a centralized multi-chip scheduler: DL0 is a monolithic, single-chip implementation, DL3 is a fully distributed multi-chip implementation.

As an intermediate step, in [39] a further possible solution is proposed: the N input selectors are physically separated in N devices, whereas all N output selectors are implemented in a single device. This solution has a major drawback: it reduces the hardware complexity by a factor of two only. However, having the output selectors in a single device permits coordination among output selectors with no delay. This permits to implement schedulers with more iterations in a single cell time, thus preserving good performance for increasing RTTs; however, this limits scheduler scalability. As such, we focus on schedulers suited to a fully distributed multi-chip scenario (distribution level DL3).

## Distributed Scheduler under Unicast Traffic Conditions

#### 4.1 Scheduling algorithms with RTT latencies

Dealing with RTTs among devices has a profound impact on scheduler design. In [39], the proposed two-phase scheduler is a direct extension of the DRRM (Dual Round Robin Matching) scheduler[20], originally conceived for a monolithic implementation, to a distributed environment.

Let us briefly summarize DRRM behavior, focusing on an enhanced version of DRRM which achieves lower delays, thanks to a modified pointer update rule similar to that used in FIRM (Fcfs in Round robin Matching) [21]. In every iteration, first a request is sent by any unmatched input to the first unmatched backlogged output in the round-robin order starting from the current request pointer position. If an output receives more than one request, it grants the one that appears first in the round-robin order starting from the current position of the grant pointer. Request pointers are updated, in the first iteration to point to the output selected in the request phase, and further to one position (modulo N) beyond the output selected if and only if the request is granted in the first iteration. Grant pointers are updated to one position (modulo N) beyond the input granted in the first iteration.

In a monolithic implementation, all decisions are taken, and known, in a single time slot, and pointers are updated accordingly. In a distributed implementation, first, request information is delayed by RTT/2 (assuming symmetric RTTs) and the request pointer update cannot be performed immediately, since grants will be available RTT/2 slots later. A straightforward extension of DRRM to a distributed scenario would imply that requests to be issued in the next time slot are based on pointer positions not updated, thus breaking the round-robin de-synchronization mechanism and leading to throughput degradation. Moreover, request selectors would not be able to accurately know the number of underway grants, thus negatively affecting request decisions.

The distributed extension of DRRM proposed in [39] is based on the following ideas. Let us focus on a single iteration case. The key idea to keep the pointer de-synchronization is to ensure that every pointer is updated at most

#### 36 4 Distributed Scheduler under Unicast Traffic Conditions

once every RTT slots. As such, each input and output selector keeps a distinct (request and grant) pointer for every RTT slots. Traditional pointer update rules are used: Request pointers are only updated when the corresponding grant arrives, one RTT after issuing the corresponding request, whereas grant pointers are updated immediately after issuing a grant, since issued grants are accepted by definition. In other words, with respect to a monolithic implementation, RTT staggered schedulers are running in pipeline dealing with requests and grants.

This implies that the scheduler complexity (in terms of required pointers) increases linearly with RTT, since RTT pointer registers are required per selector. An additional counter (modulo RTT) is needed to indicate the current pointer to be used, whereas the combinatorial selection logic does not need to be duplicated, since a multiplexer to select the proper register among the RTT registers is enough to permit a correct behavior.

Another issue is related to pending requests. Indeed, only after RTT slots it is possible to know whether an issued request was granted. In the meantime, input selectors should issue further requests. If the number of submitted requests exceeds the number of enqueued cells, it may happen that a slot is reserved for a VOQ that will become empty by the time the grant is received at the input selector, thus wasting system resources. To solve this problem, a PRC (Pending Request Counter) per VOQ plus a request history per input selector are introduced [39]. Basically, new requests are issued only if the number of pending requests is smaller than the number of cells currently stored in the corresponding VOQ. This choice, which further complicates the selector design, is fundamental to obtain good performance at low loads or under heavily unbalanced traffic.

Further problems are related to the issue of dealing with more iterations in a single time slot (see [39] for details). We disregard issues related to iterations, which can be reasonably used only if all output selectors share the same physical device. Indeed, iterations are based on the knowledge of the results of previous iterations in the same time slot; in a fully distributed scheduler with RTTs, knowledge of results of previous iterations requires RTT time slots, thus basically preventing the possibility of iterating in this scenario.

#### 4.2 Synchronous Round Robin

Let us now describe the SRR scheduler, initially disregarding issues related to RTT for simplicity. The SRR scheme is based on a cyclic, TDMA-like, preferential scheduling of VOQs. This preferential scheduling is obtained by logically numbering the slots with an incremental counter s, ranging from 0 to N - 1, i.e., a modulo N counter. Slots are logically organized in frames, named SRR frames; each frame comprises N slots.

Let us describe the input and output selectors behavior at time slot s:

- 1. the input scheduler associated to input *i* preferentially selects for a transmission the VOQ with destination output  $|i + s|_N$ . In other words, a preferential request is issued for output  $|i + s|_N$ .

- 2. if the preferential VOQ is empty, a request for the longest VOQ is attempted; ties among VOQs are broken according to a round-robin scheme.

Output schedulers grant the preferential request, if issued; otherwise, a randomly chosen request is granted among non-preferential conflicting requests.

Other possible solutions exist to break ties among VOQs at input selectors, such as random or round-robin choice among non-preferential VOQs; however, the longest VOQ choice provides the best compromise between complexity and performance, as discussed later. Note that the random choice among conflicting non-preferential requests at output selectors may be not the most natural choice. Indeed, given that input selectors choose non preferential requests exploiting a longest queue first algorithm, output selectors could select the request corresponding to the longest VOQ among conflicting requests. However, this would require an increase in signalling complexity, since VOQ lengths should be sent to output selectors, and also a complexity increase at output selectors, since conflicting request should be compared according to their length. Selecting longest queues at inputs is easier, since queues could be kept simply ordered by length; indeed, in a given time slot, at each input at most one departure and one arrival can occur. Moreover, performance results show that the benefit of the longest queue selection at outputs is marginal for both balanced and unbalanced traffic.

Regardless of the fact that the request is granted or not, a new selection is made in the next time slot, according to the above described algorithm. In summary, for low switch loads SRR behaves similarly to a single-queue FIFO strategy. At high loads, when all queues are always non-empty, the SRR preferential scheduling deterministically orthogonalizes input request attempts, so that a single preferential request is received by any output in a given time slot. More precisely, for network loads larger than or equal to the channel capacity, input selectors behave exactly like in a Time Division Multiple Access (TD-MA) scheme: during a SRR frame, whose length is equal to N slots, all inputs have exactly one access opportunity for transmissions toward each output, and they exploit this access opportunity deterministically, thereby avoiding potential conflicts at outputs. In this sense, SRR is throughput optimal under overloaded uniform traffic conditions.

A nice property of SRR is that it can be used without any modification i.e., with no complexity increase, to deal with RTTs. The only difference is that grants will be received one RTT later with respect to request issue, thus negatively affecting delays. However, we will show that even without exploiting any pending request counter, performance at low loads are comparable with those of iterative algorithms exploiting pending request counters. 38 4 Distributed Scheduler under Unicast Traffic Conditions

#### 4.3 Performance results

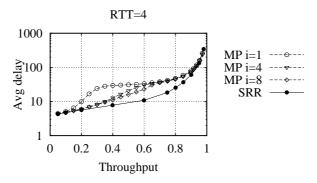

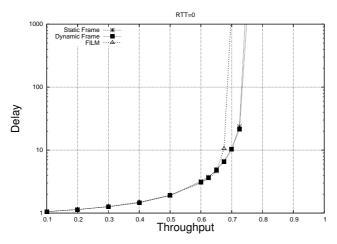

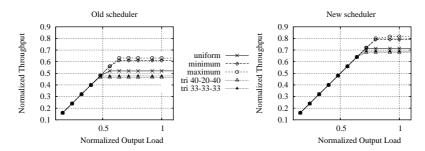

We show performance results based on simulation runs exploiting a proprietary simulation environment developed in C language. Statistical significance of the results are assessed by running experiments with an accuracy of 1% under a confidence interval of 95%. We compare SRR with the distributed extension of DRRM presented in [39]. The switch has N = 16 inputs and outputs running at the same speed, and is loaded with either Bernoulli or Bursty traffic with geometrically distributed burst sizes with an average burst size of 10 cells; cells in the burst are all directed to the same output. Performance indices are either average delays vs normalized switch throughput or maximum achievable normalized throughput in overload. SRR performance are reported as solid lines with black dots, the modified version of DRRM, which accounts for multiple pointers to deal with RTTs, is labeled MP (Multi Pointer) and plotted using dashed lines; different symbols refer to a variable number of iterations.

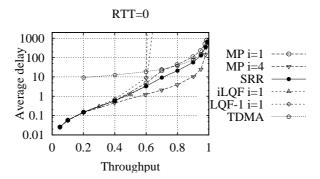

**Figura 4.1.** Performance comparison between SRR, MP, iLQF and TDMA under uniform Bernoulli traffic in a monolithic scheduler implementation (RTT=0).

Let us first examine, in Fig.4.1, a scenario in which RTT=0, which corresponds to the traditional single-chip implementation of schedulers, under uniform Bernoulli traffic. Besides DRRM and SRR, we plot also a TDMA scheme, iLQF (Longest Queue First) [10] with one iteration, and LQF-1, a simplified version of iLQF with one iteration where inputs send a single request only (for the longest queue) per time-slot to outputs. Note that the TDMA scheme corresponds to SRR using the preferential scheduling only whereas LQF-1 corresponds to SRR using the non-preferential scheduling only. Clearly, the preferential scheduling scheme of SRR is fundamental to obtain good performance results at high loads: indeed, iLQF with i = 1 iteration saturates at 0.65, whereas LQF-1 saturates at 0.61. At low loads the non-preferential

Figura 4.2. Performance comparison between SRR and MP under uniform Bernoulli traffic for variable RTTs.

scheme of SRR becomes dominant, so that performance are close to those of modified DRRM and much better than those of a pure TDMA.

In Fig.5.1 we report delays as a function of the switch throughput for variable RTTs under uniform Bernoulli traffic. No throughput limitations are observed for both SRR and modified DRRM; SRR shows remarkably low delays, improving performance as RTT increases. Only a slight delay impairment can be noticed for low-medium loads and small RTTs; this is due to the missing pending request counters, which are instead used in the modified DRMM. Recall that pending request counters are fundamental to avoid issuing too many request for the same VOQ; indeed, if the number of requests issued exceeds the number of enqueued cells, which may happen at low-medium loads and for large RTTs, it may happen that the VOQ becomes empty by the time the grant is received, thus wasting system resources. Indeed, modified DRRM without pending request counters performs much worse, as shown in Fig.4.3, where SRR clearly outperforms the modified DRRM. Moreover, recall that SRR, besides not exploiting any additional counter, does not require any iteration, thus allowing a fully distributed implementation; nevertheless, delay performance are comparable with those of modified DRRM with  $\log N = 4$ iterations, and improve with increasing RTTs. Minor differences exist in this scenario if the non-preferential VOQ choice at inputs in SRR is done on a

Figura 4.3. Performance comparison between SRR and MP under uniform Bernoulli traffic when MP is not using the PRC counters.

**Figura 4.4.** Performance comparison between SRR and MP under uniform Bursty traffic for variable RTTs.

round-robin basis instead of using a longest queue choice.

Similar performance are shown by SRR for Bursty traffic, as reported in Fig.4.4. Delay properties are remarkable, since SRR shows much better performance than modified DRRM with i = 1 iteration also under correlated traffic. Note that SRR with the random choice of non-preferential VOQs at input selectors, labelled SRR-RND in the plot, show much worse performance than SRR for medium loads, thus justifying the choice of the longest VOQ when the preferential queue is empty.

## Distributed Scheduler under Multicast Traffic Conditions

#### 5.1 Multicast scheduling algorithms

We define the fanout set of a multicast cell as the set of outputs to which the cell should be transferred. The cell fanout is the number of outputs in the fanout set. A multicast scheduler may not be able to transfer a multicast cell in a given time slot to all outputs in the cell fanout set, since some outputs may be matched to other inputs by the scheduler. In this case, to enhance performance, most multicast schedulers try to send a copy of the multicast cell to the largest available set of outputs; this is often named fanout splitting discipline. Fanout splitting disciplines may leave a residue, i.e., a copy of the multicast cell that must reach the subset of output ports that were not matched to the given input port in previous time slots.

We focus on two previously proposed multicast scheduling algorithms, selected due to their ease of implementation and good performance: WBA (Weight-Based Algorithm) [36] and mRRM [44]. Both rely on a single FIFO queue at each input for multicast. We briefly remind the WBA and mRRM scheduler behavior referring to a scenario where RTT=0 for simplicity. Both schedulers are based on a two-phase request-grant algorithm.

WBA assigns weights to input cells based on their age and fanout at the beginning of every cell time. Once weights are assigned, each OS chooses the heaviest input among those subscribing to it. More precisely, at the beginning of every cell time, each IS computes the weight of the new multicast cell/residue at its HOL based on the age of the cell (the older, the heavier), and the fanout of the cell (the larger, the lighter). Then, each IS sends this weight to all outputs that the cell/residue at its HOL wishes to reach. Each OS grants to the input with the highest weight, independently of other outputs, breaking ties with a random choice. Note that a positive weight should be given to age to avoid input starvation. However, to maximize throughput, fan-out are weighted negatively. Several weight assignments algorithm can be adopted (see [36] for details). We use the weight definition chosen in the simulator available on the Web site at http://klamath.stanford.edu/tools/SIM/:

42 5 Distributed Scheduler under Multicast Traffic Conditions

The cell weight is equal to the number of inputs minus the cell fanout plus the cell age.

Multicast Round Robin (mRRM) was designed to be simple to implement in hardware. A single pointer to inputs is collectively maintained by all outputs. Each output selects the next input that requests it at, or after, the pointer, following a round robin order. At the end of the cell time, the single pointer is moved to one position beyond the first input that is served. However, the single pointer update rule at OSs of mRRM does not permit a fully distributed multi-chip implementation, since output selectors need to be aware of other output selector choice to update the pointer value and this would imply a delay equal to the RTT for pointer update rule that would break the mechanism.

#### 5.2 Improved Multicast Round Robin

Direct extensions of WBA and mRRM can be envisioned to deal with RTTs among input/output selectors induced by multi-chip implementation. Since grants are received at IS with a delay of RTT slots, a multicast cell is at the head-of-the-line for at least RTT slots. To avoid issuing multiple requests for the same cell, thus wasting resources, a number of queues equal to RTT+1 is needed. ISs choose the queue from which the request is issued according to a round-robin fixed scheme among input queues. As such, at most one request per input queue is issued in each RTT. OSs keep working as in the basic WBA and mRRM scheme.

Further extensions can be envisioned and are studied later when presenting simulation results. Indeed, the single FIFO scheme when RTT=0 and its direct extension to RTT+1 FIFO queues when RTT > 0 does not solve the issue of HoL blocking for multicast flows. As such, in some experiments, we introduce a limited number of k = 2 FIFO queues at each input and  $k = 2 \times (\text{RTT} + 1)$  for RTT> 0. In this case, whereas output selectors operate as in the basic scheme, input selectors choose one among the k queues according to queue weights for WBA and to a round-robin scheme for mRRM.

The introduction of more queues at inputs, either to deal with RTTs or to reduce the HoL blocking, introduces the issue of multicast flow assignment to queues. Although several possible assignment strategies were studied in the past [29, 30], in this paper we simply adopt a packet-by-packet load balancing scheme among available queues. We are aware that this may introduce out-ofsequence delivery, but we prefer to avoid studying assignment scheme in this initial work and concentrate on the issue related to dealing with RTTs.

Let us now describe the IMRR (Improved Multicast Round Robin) scheduler, initially disregarding issues related to RTT for simplicity when a single FIFO queue is available. The same concept of preferential input is kept as in the mRRM algorithm: at each time slot, all output selectors keep a single pointer to a preferential input. However, the pointer update rule is stateless;

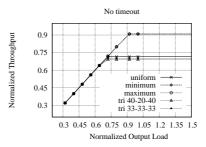

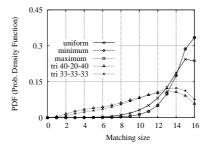

Figura 5.1. Performance comparison under uniform Bernoulli cell arrivals.

regardless of the granted cell, at each time slot, the pointer is increased (modulo N) according to a round robin scheme. This is fundamental to guarantee that the scheduler can run in the fully distributed case, since no coordination among output scheduler is required. Input selectors issue a request containing a weight equal to the fanout of the selected cell. Output selectors choose the request from the preferential input, if any, otherwise they grant the request corresponding to the smallest fanout.

When more than one queue is present at inputs to avoid HoL (i.e., k = 2 queues for RTT=0 and  $k = 2 \times (\text{RTT}+1)$  queues for RTT>0), input selectors issue a request for the cell with largest weight, the weight being queue length plus cell fanout.

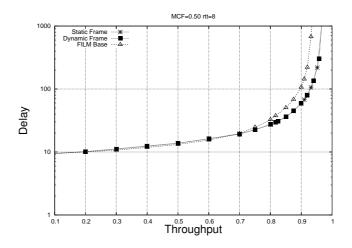

#### 5.3 Performance results

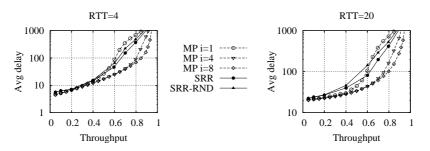

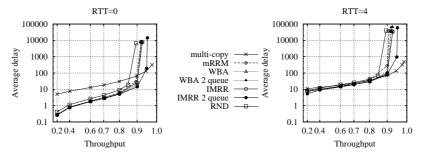

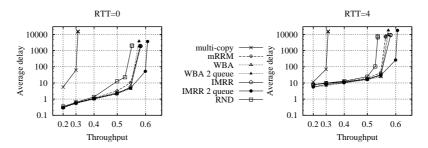

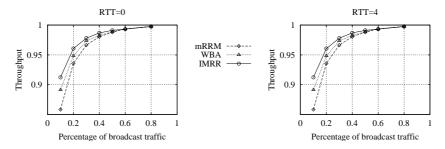

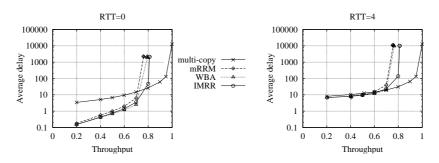

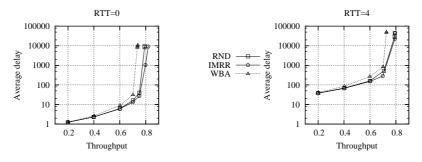

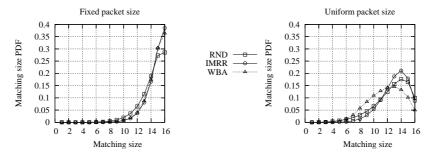

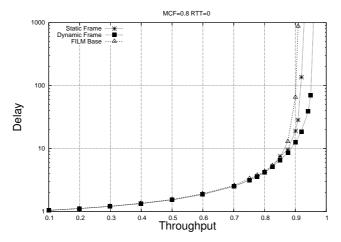

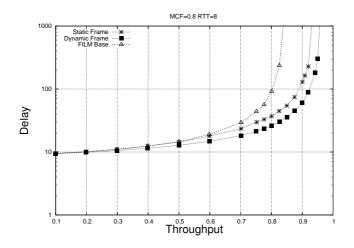

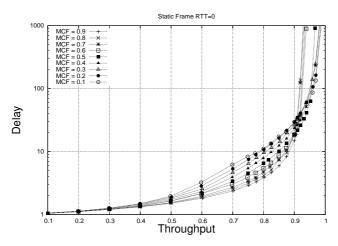

We show performance results based on simulation runs exploiting a proprietary simulation environment developed in C language. Statistical significance of the results are assessed by running experiments with an accuracy of 1% under a confidence interval of 95%. We compare IMRR with the previously presented extensions of mRRM and WBA, with a random (RND) scheduler, and with the multi-copy approach, where multicast cells are replicated at inputs and treated as unicast cells. In the multi-copy approach, the unicast SRR scheduler [31] is run, given its good performance and adaptability to the fully distributed multi-chip scenario.

The switch has N = 16 inputs and outputs running at the same speed; cells are generated according to an i.i.d. Bernoulli process, i.e., at each time slot, an input port receives a cell with probability  $\rho$ ,  $0 \le \rho \le 1$ , equal to the input load. Later, we also consider packet arrivals, i.e., trains of cells willing to reach the same output, the number of cells being drawn from a uniform distribution ranging from 1 to 16 cells. Performance indices are either average delays vs normalized switch throughput or maximum achievable normalized throughput in overload.

Figura 5.2. Performance comparison under gathered traffic with cell arrivals.

In terms of traffic distribution among input and output ports, we initially consider both i) a uniform scenario, in which all input (and output) ports are equally loaded and the fanout set of a new cell is generated randomly, according to a uniform distribution, ii) a gathered scenario, where the traffic is gathered over few (M = 5) active input ports and equally distributed over all N = 16 output port. In the gathered scenario, the fanout set is chosen according to a non-uniform binomial distribution, with mean fanout  $h_m = 3.66$ . More precisely, the probability  $P_f$  of choosing a fanout set of size f is  $P_f = N/h_m {N \choose f} (h_m/N)^f (1 - h_m/N)^{N-f}$ . This is a traffic pattern well known to be hard to schedule [29]. Indeed, when all inputs are equally loaded, the maximum sustainable traffic leads to a normalized input load which is at most 1/E[f], E[f] being the average cell fanout size. If instead the traffic is gathered among few inputs, the normalized input load for sustainable traffic can approach 1, so that the efficiency in serving cells queued at the inputs becomes important on performance. Note that the considered gathered traffic scenario is far from being unrealistic. Multicast applications often generate sustained and long-lasting flows, that may only engage few inputs and several outputs at a given router or switch.

In both uniform and gathered traffic scenarios, unicast traffic is not given any special attention and is treated as a special case of multicast traffic with fanout set equal to one. To analyze switch behavior in a more realistic environment which includes a significant percentage of unicast traffic, we also examine two mixed traffic scenarios, the first one comprising a variable mix of unicast and broadcast traffic only, the second one in 50% of unicast and 50% of multicast traffic load the switch.

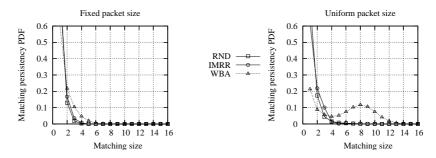

IMRR performance are reported as solid lines with circles, the modified version of WBA is plotted using dotted lines with triangles, whereas the modified version of mRRM is identified by dashed lines with diamonds; the multicopy approach is plotted with a solid line with crosses, and the random scheduler with squares. White symbols refer to the case of a single FIFO for RTT=0 and RTT+1 queues for RTT> 0, whereas black symbols are used for k = 2 FIFOs for RTT+0 and  $k = 2 \times (\text{RTT+1})$  FIFOs for RTT> 0.

Figura 5.3. Performance comparison for uniform traffic and a variable percentage of unicast and broadcast traffic only.

Figura 5.4. Performance comparison for uniform traffic: 50% unicast and 50% multicast traffic.

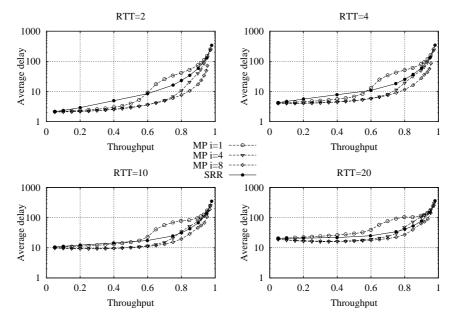

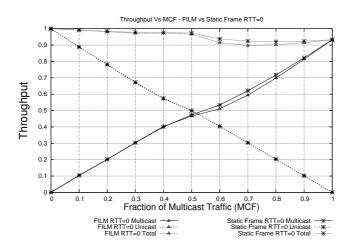

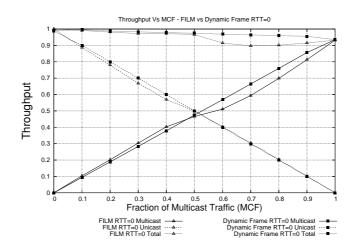

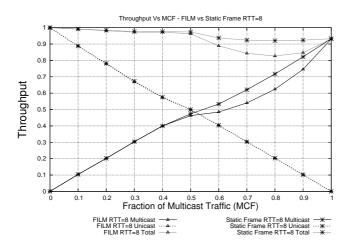

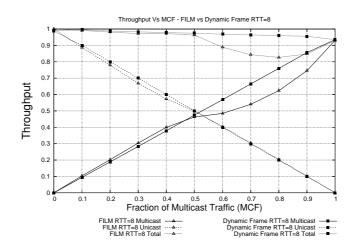

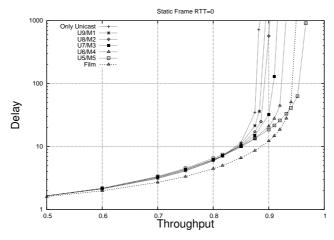

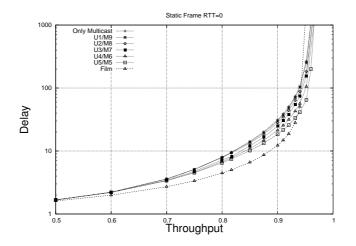

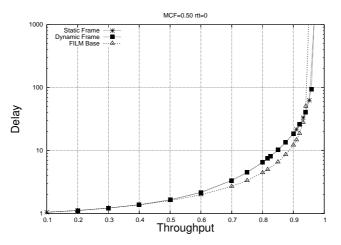

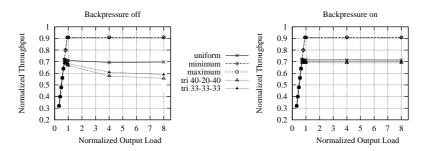

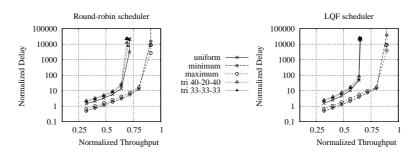

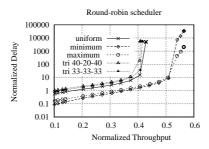

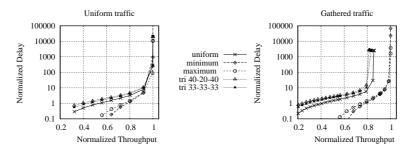

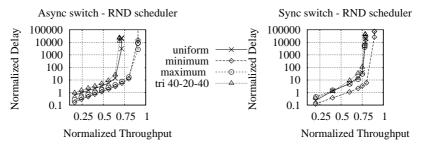

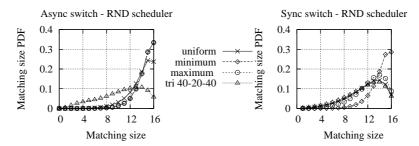

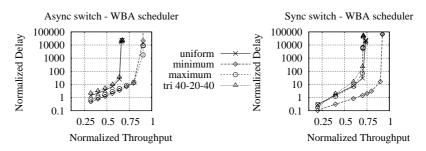

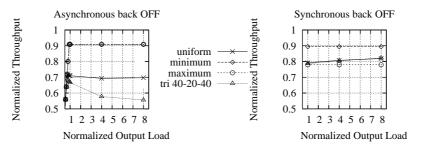

In Fig.5.1 we report delays as a function of the switch throughput for variable RTTs under uniform multicast Bernoulli traffic with cell arrivals. Only the multi-copy approach permits to obtain 100% throughput; however, the price to be paid is a significant increase in the average delay at low-medium loads when RTT=0. When increasing RTT to 4 time slots, all algorithms show similar delay performance. No major differences are evident among multicast schedulers, apart from a slight throughput increased obtained by the proposed IMRR when using k FIFO queues per RTT. The RND scheduler performs worse, as expected.