### UNIVERSITÀ DELLA CALABRIA

Dipartimento di Ingegneria Informatica, Modellistica, Elettronica e Sistemistica

#### Dottorato di Ricerca in

Tecnologie dell'informazione e della comunicazione

CICLO XXXI

TITOLO TESI

### Reliability of GaN-based devices for Energy Efficient Power Applications

Settore Scientifico Disciplinare ING-INF/01 Elettronica

**Coordinatore:**

Ch.mo Prof. Felice Crupi

Firma: Jeliee Cupi

Supervisore/Tutor: Ch.mo Prof. Felice Crupi

Firma: Jeliee Crupi

**Co-tutor:**

Ch.mo Prof. Lionel Trojman

Firma:

Dottoranda:

Eliana Maribel Acurio Méndez

Firma:

### **Declaration of Authorship**

I, Eliana Maribel Acurio Méndez, declare that this thesis titled, "Reliability of GaNbased devices for Energy Efficient Power Applications " and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date: 14.01.2019

"A dream you dream alone is only a DREAM. A dream you dream TOGETHER is reality."

Yoko Ono

### Abstract

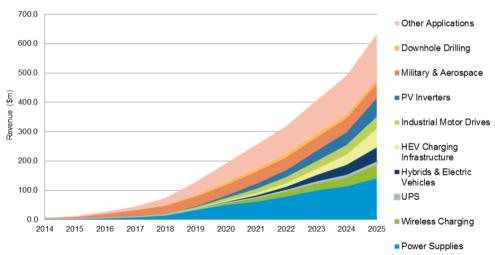

The wide spectrum of power electronics applications, including their role in renewable energy conversion and energy saving, require the innovation from conventional Silicon (Si) technology into new materials and architectures that allow the fabrication of increasingly lightweight, compact, efficient and reliable devices. However, the trade-off between long lifetime, high performance and low cost in the emerging technologies represents a huge limitation that has gained the attention of different research groups in the last years.

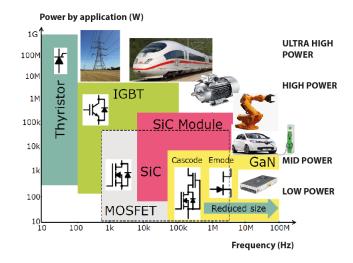

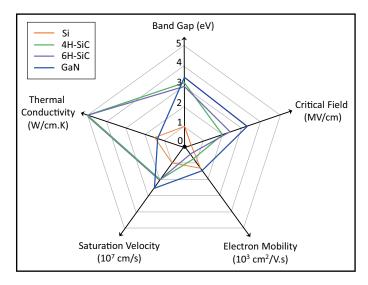

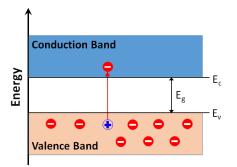

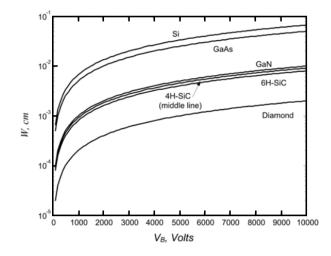

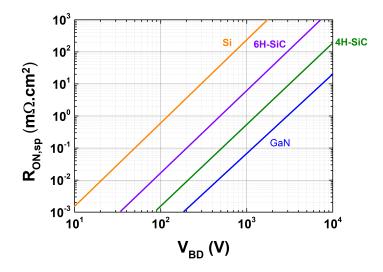

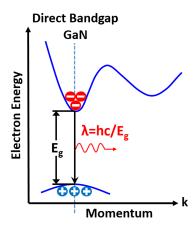

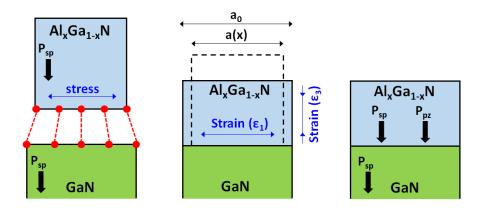

Gallium Nitride (GaN) is a wide-bandgap semiconductor (WBGS) that constitutes an excellent candidate for high-power and high-frequency applications due to its remarkable features such as high operating temperature, high dielectric strength, high current density, high switching speed, and low on-resistance. Compared with its Silicon counterpart, GaN is superior in terms of high breakdown field (3 MV/cm), exceptional carrier mobility, and power dissipation. By taking into account other WBG materials such as SiC, GaN grown on Si substrates promises similar performance but at a much lower cost in the low to mid power and high-frequency range.

Since GaN allows size and weight device reduction due to a better relationship between on-resistance and breakdown voltage, it is suitable for a variety of applications such as RF power amplifiers, power switching systems, sensors, detectors, etc. Especially, in the field of energy efficiency, GaN technology appears as a future successor of Si in power conversion circuits. However, some drawbacks related to technology cost, integration, and long-term reliability have to be overcome for its wide adoption in the power applications market.

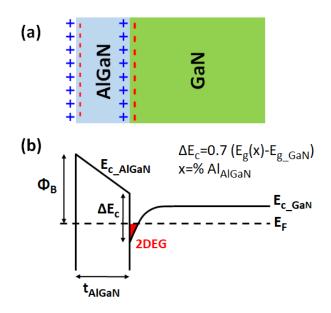

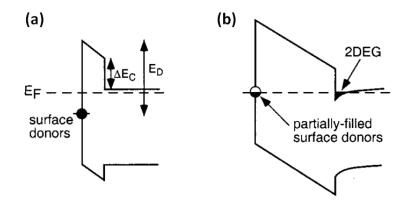

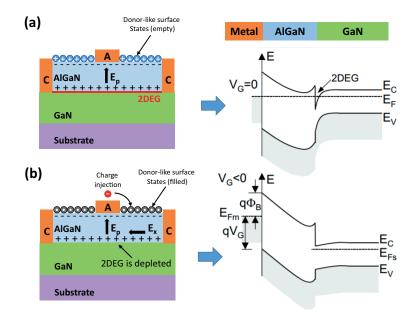

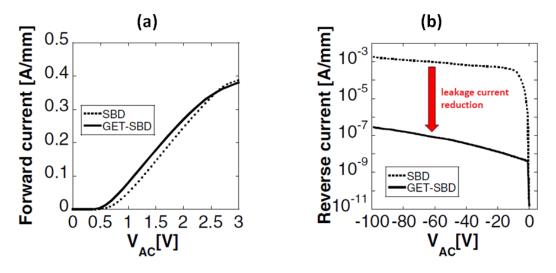

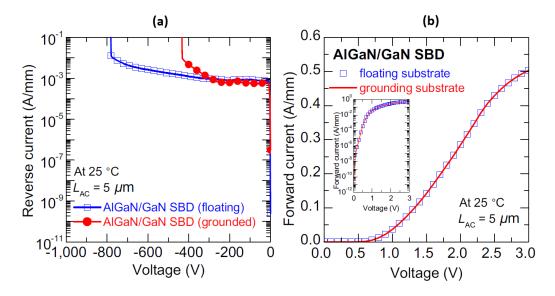

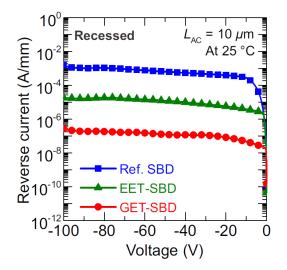

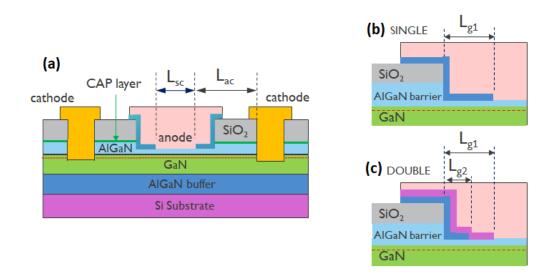

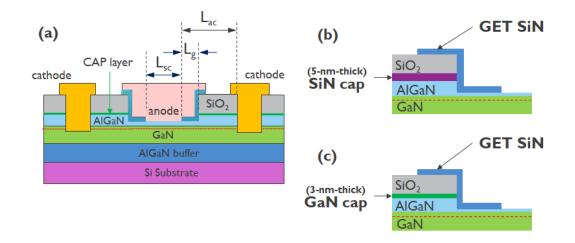

One of the worst inconveniences of AlGaN/GaN High Electron Mobility Transistors (HEMTs) is the normally-ON operation. Since a two-dimensional electron gas (2DEG) channel is formed at the AlGaN/GaN interface due to inherent material properties, a negative bias has to be applied at the gate to switch the device off. Among the proposed solutions to fabricate normally-OFF devices, the metaloxide/insulator-semiconductor (MOS/MIS) structure with different insulators has shown remarkable improvements in gate leakage reduction and drain current increase. Also in AlGaN/GaN Schottky Barrier Diodes (SBDs), the introduction of a MOS structure to create a gated edge termination (GET) at the anode area has resulted in significant improvements in reverse diode leakage and forward diode voltage. Nevertheless, the improvement in the device performance by the introduction of a dielectric could seriously affect the device long-term reliability since additional degradation in this layer and at its interfaces with AlGaN or GaN occurs.

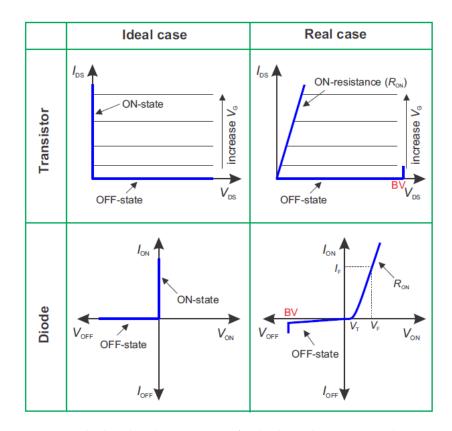

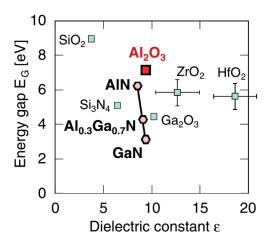

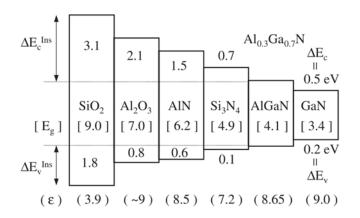

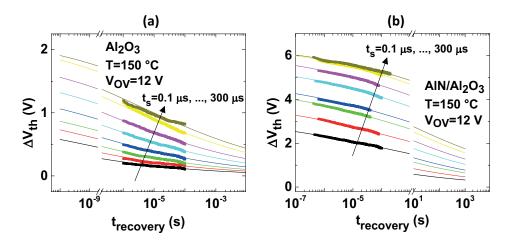

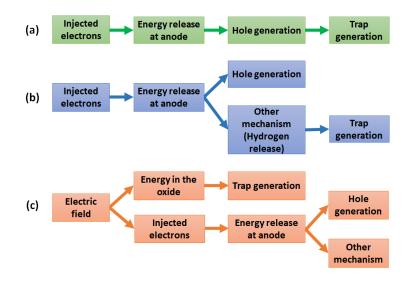

In the case of conversion systems, power devices are continuously switched from an OFF-state condition at high drain bias to an ON-state condition at large drain current. Therefore, the reliability of GaN-based devices has to be proven for the complete ON/OFF operation. This dissertation focuses on providing a more comprehensive analysis of two main reliability issues related to the dielectric insertion under the gate/anode stacks by analyzing the use of different dielectric materials and device architectures. The first issue is the positive bias temperature instability (PBTI), which is related to the degradation of electrical parameters when high gate voltages and temperatures are applied and is especially observed during the ON-state operation of the transistor. By using MOS-HEMT structures with different gate dielectrics (SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and AlN/Al<sub>2</sub>O<sub>3</sub>), the impact of the stress voltage, recovery voltage and temperature on the device reliability is analyzed including the role of oxide traps and the interface states to provide physical insights into this mechanism.

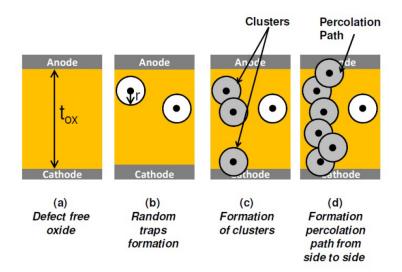

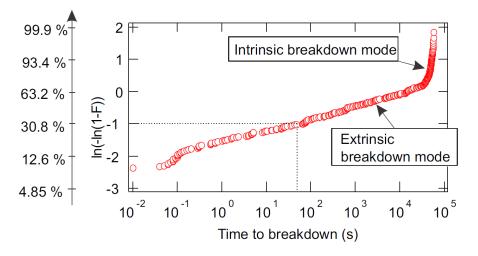

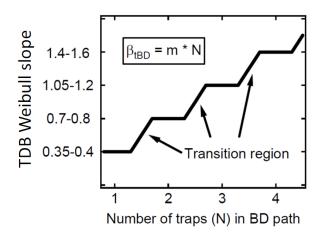

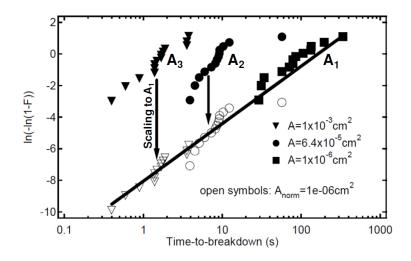

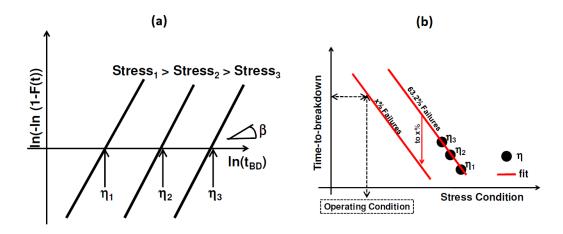

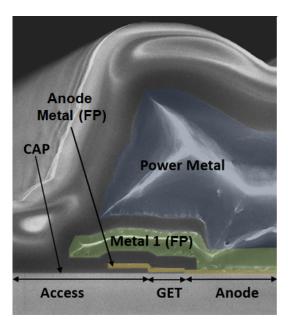

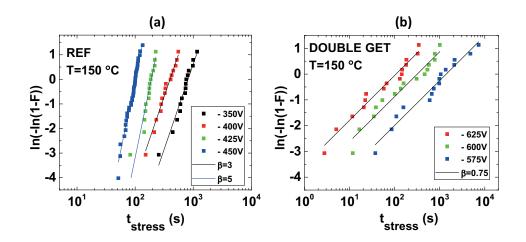

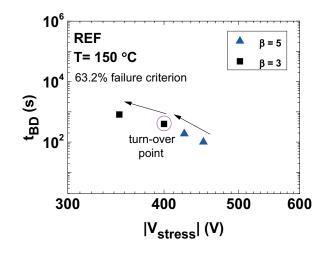

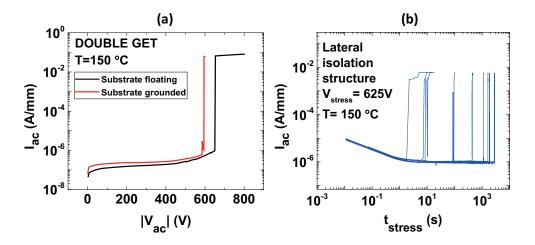

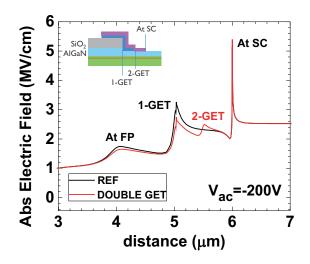

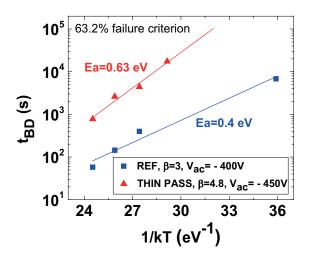

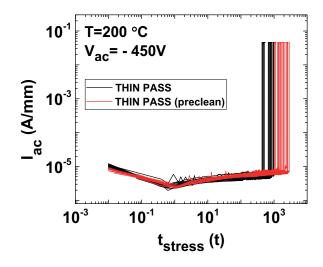

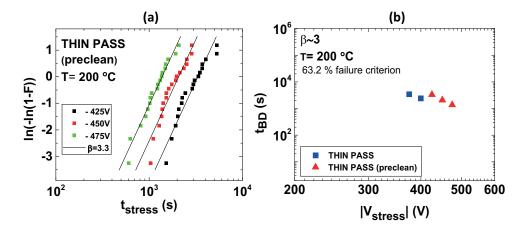

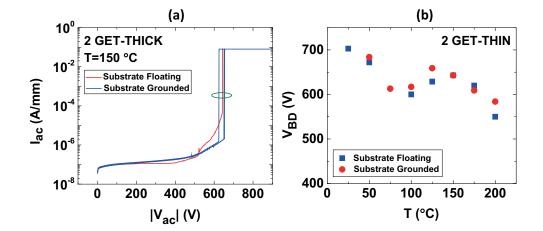

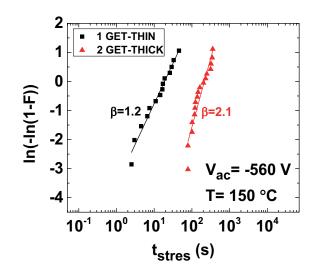

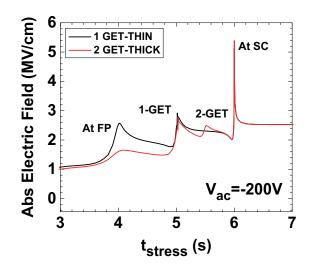

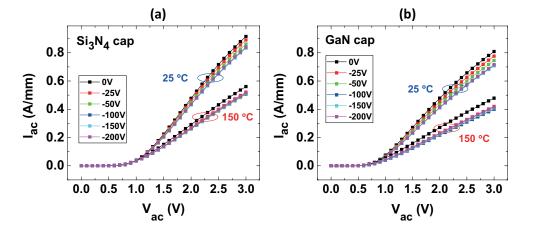

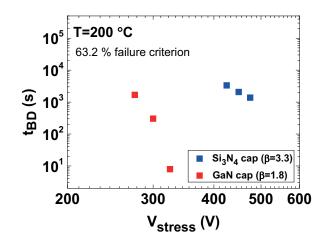

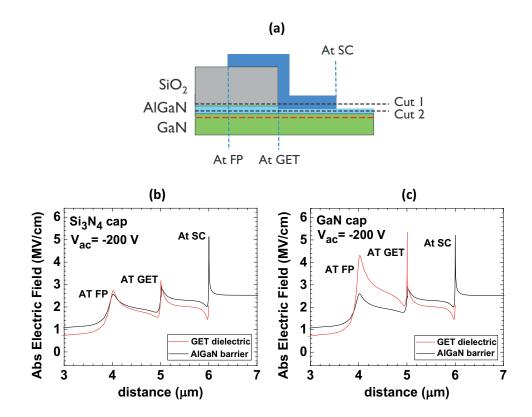

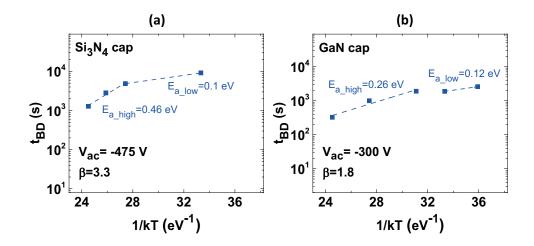

The second phenomenon discussed in this thesis is the time-dependent dielectric breakdown (TDDB) observed on GET-SBDs during its OFF-operation. The percolation model and Weibull distribution are used to understand this degradation mechanism. As a result, it has been demonstrated that the time to breakdown  $t_{BD}$ is influenced by the GET structure (single vs. double), the passivation thickness, the preclean process at the anode region before the GET dielectric deposition and the capping layer. Finally, by using 2D TCAD simulations, the long-term reliability improvement has been related to the reduction of the electric field peaks at critical areas such as the GET corner and beneath the anode field plate.

### Sommario

Il nitruro di gallio (GaN) è un semiconduttore ad ampia banda proibita (WBGS) che costituisce un candidato eccellente per applicazioni ad alta potenza e ad alta frequenza grazie alle sue notevoli caratteristiche come alta temperatura operativa, elevata rigidità dielettrica, alta densità di corrente, elevata velocità di commutazione e bassa resistenza.

Poiché GaN consente riduzioni di dimensioni e peso del dispositivo grazie a una migliore relazione tra tensione on e resistenza, è adatto per una varietà di applicazioni come amplificatori di potenza RF, sistemi di commutazione dell'alimentazione, sensori, rivelatori, ecc. Soprattutto nel campo di efficienza energetica, la tecnologia GaN appare come un futuro successore di Si nei circuiti di conversione di potenza. Tuttavia, alcuni inconvenienti legati al costo, all'integrazione e all'affidabilità a lungo termine della tecnologia devono essere superati per la sua ampia adozione nel mercato delle applicazioni di potenza.

Uno dei peggiori inconvenienti dei transistor ad alta mobilità di elettroni Al-GaN/GaN (HEMT) è l'operazione normalmente attivata. Poiché un canale bidimensionale a gas di elettroni (2DEG) è formato all'interfaccia AlGaN/GaN a causa delle proprietà intrinseche del materiale, è necessario applicare una polarizzazione negativa al gate per spegnere il dispositivo. Tra le soluzioni proposte per fabbricare dispositivi normalmente OFF, la struttura di ossido di metallo/isolante-semiconduttore (MOS/MIS) con diversi isolanti ha mostrato notevoli miglioramenti nella riduzione della perdita di gate e nell'aumento della corrente di drain. Anche nei diodi a barriera Schottky (SBD) AlGaN/GaN, l'introduzione di una struttura MOS per creare una terminazione del bordo gated (GET) nell'area dell'anodo ha portato a miglioramenti significativi nella perdita di diodo inversa e nella tensione di diodo diretta. Tuttavia, il miglioramento delle prestazioni del dispositivo mediante l'introduzione di un dielettrico potrebbe seriamente compromettere l'affidabilità a lungo termine del dispositivo poiché si verifica un ulteriore degrado in questo strato e nelle sue interfacce con AlGaN o GaN.

Questa dissertazione si concentra sulla fornitura di un'analisi più completa di due principali problemi di affidabilità relativi all'inserzione dielettrica sotto le pile di gate/anodi analizzando l'uso di diversi materiali dielettrici e architetture di dispositivi. Il primo problema è l'instabilità positiva della temperatura di polarizzazione (PBTI), che è correlata alla degradazione dei parametri elettrici quando vengono applicate alte tensioni di gate e temperature e viene particolarmente osservato durante il funzionamento a stato ON del transistor. Utilizzando strutture MOS-HEMT con diversi dielettrici di gate (SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, e AlN/Al<sub>2</sub>O<sub>3</sub>), l'impatto della tensione di tensione, della tensione di recupero e della temperatura sull'affidabilità del dispositivo viene analizzato includendo il ruolo delle trappole di ossido e gli stati dell'interfaccia per fornire intuizioni fisiche in questo meccanismo.

Il secondo fenomeno discusso in questa tesi è la ripartizione dielettrica dipendente dal tempo (TDDB) osservata su GET-SBD durante la sua operazione OFF. Il modello di percolazione e la distribuzione di Weibull sono utilizzati per comprendere questo meccanismo di degrado. Di conseguenza, è stato dimostrato che il tempo di rottura del  $t_{BD}$  è influenzato dalla struttura GET (singola contro doppia), dallo spessore di passivazione, dal processo precluso nella regione dell'anodo prima della deposizione dielettrica GET e dallo strato di capping. Infine, utilizzando simulazioni 2D TCAD, il miglioramento dell'affidabilità a lungo termine è stato correlato alla riduzione dei picchi del campo elettrico in aree critiche come l'angolo GET e sotto la piastra del campo anodico.

### Acknowledgements

First and foremost, I thank God Almighty for blessing and giving me the strength and courage that I needed to achieve this dream. During the inconveniences and difficulties, He was my light of hope and my refuge. This Ph.D. meant more than scientific work to me, it also represented a journey towards self-awareness of my strengths and weaknesses, which has become an invaluable treasure for my life. The summarized work in this thesis would not have been possible without the guidance and support from many people around me. Therefore, I would like to take this great opportunity to express my gratitude to all of them because they made this experience unforgettable.

I would like to express my sincere gratitude to the most wonderful research advisor Prof. Felice Crupi, who gave me the opportunity to start this Ph.D. and encouraged me through many research obstacles for the past three years with the patience that characterizes him. I really appreciate his guidance, expertise and significant feedback because his extensive knowledge and considerable background in semiconductor and reliability fields greatly improved my research work.

Prof. Lionel Trojman, as my local supervisor at Universidad San Francisco de Quito (Ecuador), deserves special thanks for taking the time to give me personalized semiconductor lectures before I started this Ph.D. and for his continuous advice, support, confidence, and motivation during this adventure.

I would also like to thank Escuela Politecnica Nacional (Ecuador) for financially supporting my research activities and my stay in Italy, Belgium, and Ecuador. I want to express my sincere thanks to all the professors and staff of the Physics Department for their support and cooperation during the period of this work. In special, I extend my heartfelt gratitude to Dr. Marco Bayas and Dr. César Costa for approving and promoting this Ph.D. as department heads.

In 2017, I had the opportunity to perform research at the Interuniversity Microelectronics Centre (imec) in Leuven (Belgium) to expand my learning in GaN technology and I would like to deeply appreciate the opportunity from Dr. Stefaan Decoutere. Working with him and his expert GaN team members was doubtless an important experience because not only deepened my knowledge in GaN device characterization and reliability tests but also expands my education in advanced fabrication process steps in this technology.

As the characterization engineer in the group and my daily supervisor at imec, Dr. Nicolò Ronch deserves my undying gratitude. I enjoyed working with him in the lab and learned a lot from our weekly meetings to evaluate my progress, and define future works. It was wonderful to have a researcher like him as my supervisor and my good friend at the same time. I would like to also thank the following GaN team members: Brice De Jaeger, Prof. Benoit Bakeroot, Dr. Steve Stoffels, Dr. Shuzhen You, Karen Geens, Dr. Niels Posthuma, Dr. Marleen Van Hove, Dr. Dirk Wellekens and the rest of the members of the Epi-GaN section.

Many thanks to Prof. Paolo Magnone (University of Padua) and Dr. Ferdinando Iucolano (STMicroelectronics) for their scientific criticism, their involvement in this research, and their knowledge sharing during our fruitful discussions. It was definitely my pleasure and valuable experience to work with them. Without doubts, their feedback highly enriched this work.

Friends are the family that one can choose and I have the best. Part of this adventure was to meet new people and make new friends. Therefore, I want to thank all the new friends that I made from Ecuador, Italy, Belgium and from around the world for encouraging me and lending me their helping hand during my studies. I am also very grateful to my longtime friends for cheering me up and for their support to overcome personal difficulties even when an ocean separates us.

The words are insufficient to thank my family, which is a great pillar of wholehearted support in my life. God blessed me with my caring and loving parents, Pablo and Lourdes, my beautiful sisters, Sheylla, Liseth, and Britanie, my adorable niece Emily, and my tender grandmother Blanca. This Ph.D. started just like a dream in my head, but all of you taught me that with effort and determination any dream can become true. My mom merits special mention because she is my role model. Her unlimited strength, sacrifice, perseverance, and willpower motivated me to explore my potentials and helped me to believe in myself since I was a child. Her unconditional love shows me that does not matter how difficult the situations are, giving up is not an option and now I am so grateful for that lesson that allowed me to finish this Ph.D. journey.

Finally, these words are for you my dear Cristian: Thank you so much for your deepest love, for your support through the distance, for encouraging me to pursue my dreams and for holding my hands in my ups and downs. I still cannot believe how lucky I am to be your wife. I am eternally in debt to God for having you in my life. Your love was and is my greatest inspiration every day and makes me a better version of myself. I love you.

Thank you all, Eliana

## Contents

| De | Declaration of Authorship iii |        |                                                          |    |

|----|-------------------------------|--------|----------------------------------------------------------|----|

| AŁ | Abstract vii                  |        |                                                          |    |

| So | mma                           | rio    |                                                          | ix |

| Ac | know                          | ledger | nents                                                    | xi |

| 1  | Intro                         | ductio | n                                                        | 1  |

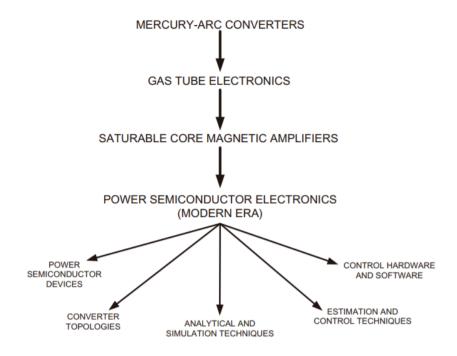

|    | 1.1                           | Moder  | n Power Electronics                                      | 1  |

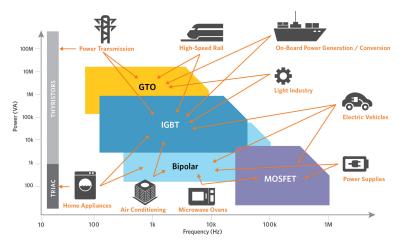

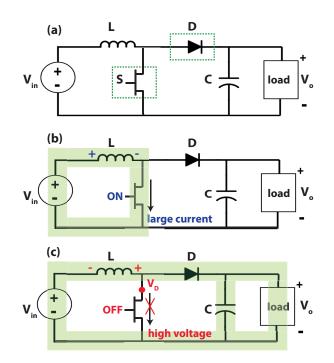

|    | 1.2                           | Switch | ing devices in power conversion systems                  | 3  |

|    | 1.3                           |        | arison of semiconductor materials for power applications |    |

|    |                               | 1.3.1  | Bandgap $(E_g)$                                          |    |

|    |                               | 1.3.2  | Critical Electric Field ( $E_{critical}$ )               |    |

|    |                               | 1.3.3  | Electron Mobility $(\mu_n)$                              |    |

|    |                               | 1.3.4  | Saturated electron drift velocity $(V_{sat})$ .          |    |

|    |                               | 1.3.5  | Thermal Conductivity $(\lambda)$                         |    |

|    | 1.4                           |        | ginning of GaN in power electronics                      |    |

|    | 1.5                           |        | al limitations for a wide GaN-technology adoption        |    |

|    | 1.6                           |        | content overview                                         |    |

|    | 1.0                           | 1.6.1  | Thesis objective                                         |    |

|    |                               | 1.6.2  | Thesis objective                                         |    |

|    |                               | 1.0.2  | Chapter 2: GaN technology                                |    |

|    |                               |        | Chapter 3: Reliability study of MOS-HEMTs                |    |

|    |                               |        |                                                          |    |

|    |                               |        | Chapter 4: Reliability study of GaN-based SBDs           |    |

|    |                               |        | Chapter 5: Conclusion and outlook                        | 12 |

| 2  |                               | Techn  |                                                          | 13 |

|    | 2.1                           |        | al Properties                                            |    |

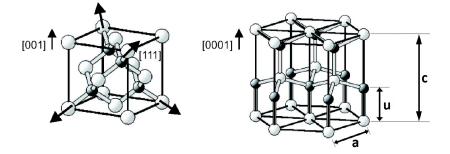

|    |                               | 2.1.1  | Crystal structure                                        |    |

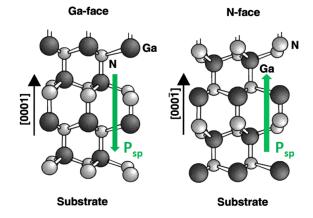

|    |                               | 2.1.2  | AlGaN/GaN heterojunction                                 |    |

|    |                               | 2.1.3  | Substrates                                               |    |

|    |                               |        | SiC                                                      | 19 |

|    |                               |        | Sapphire $(Al_2O_3)$                                     |    |

|    |                               |        | Si                                                       |    |

|    | 2.2                           | GaN-b  | ased devices architectures                               | 20 |

|    |                               | 2.2.1  | AlGaN/GaN High Electron Mobility Transistors (HEMTs)     | 20 |

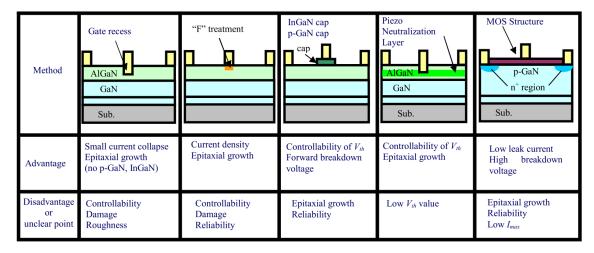

|    |                               |        | Enhancement mode GaN-based devices                       | 21 |

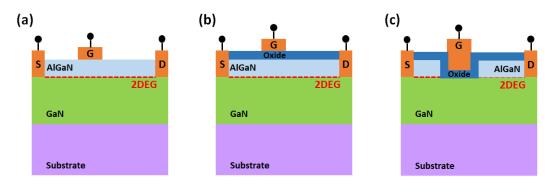

|    |                               | 2.2.2  | AlGaN/GaN Metal-Oxide-Semiconductor (MOS) and Metal-     |    |

|    |                               |        | Insulator-Semiconductor (MIS) HEMTs                      | 22 |

|    |                               | 2.2.3  | AlGaN/GaN lateral Schottky Barrier Diodes (SBDs)         |    |

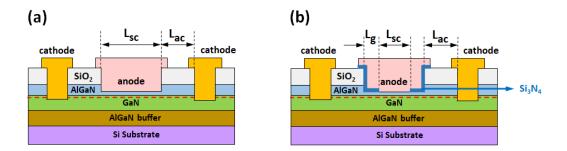

|    |                               |        | Au-free Gated edge termination (GET) SBDs                | 23 |

|    | 2.3                           | Issues | and failure mechanisms in GaN-based devices              |    |

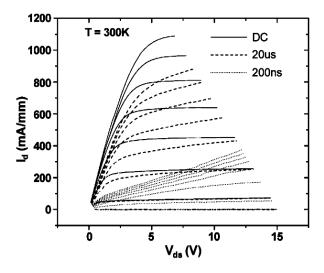

|   |      | 2.3.1                                   | Self-Heating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25       |

|---|------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

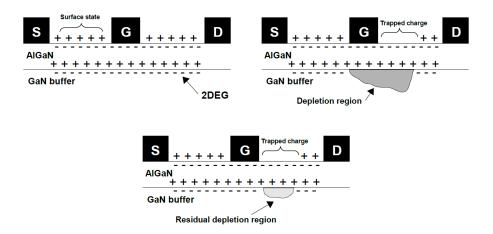

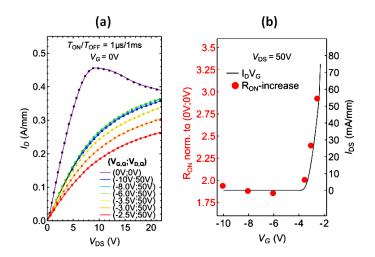

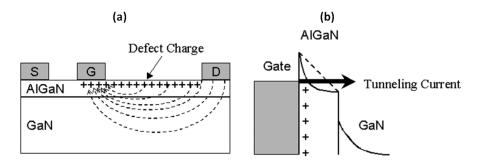

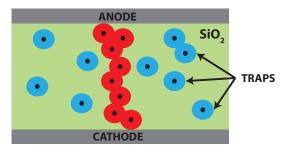

|   |      | 2.3.2                                   | Trapping Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25       |

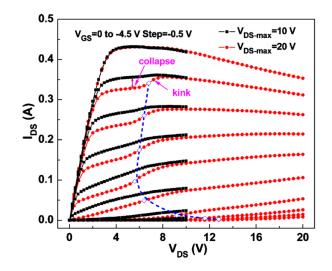

|   |      |                                         | The kink effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26       |

|   |      |                                         | Current collapse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27       |

|   |      | 2.3.3                                   | Reliability-related issues in GaN-based power switching devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29       |

|   |      |                                         | OFF-state related reliability issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29       |

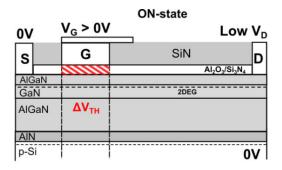

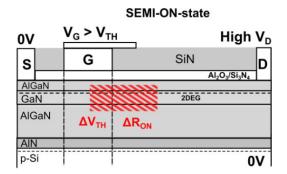

|   |      |                                         | ON-state related reliability issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31       |

|   |      |                                         | SEMI-ON state related reliability issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32       |

|   | 2.4  | Summ                                    | ary of this chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32       |

| 3 | Rali | ability                                 | study of MOS-HEMTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35       |

| 3 | 3.1  |                                         | e recoverable behavior of PBTI in AlGaN/GaN MOS-HEMT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35       |

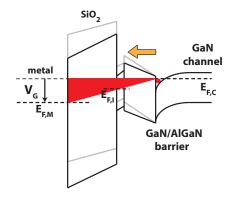

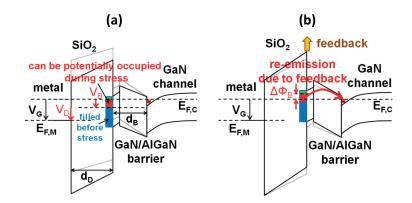

|   | 0.1  | 3.1.1                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35       |

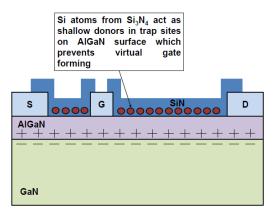

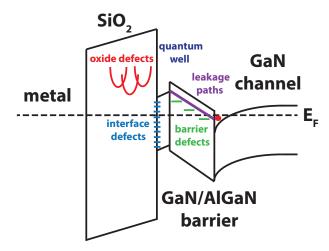

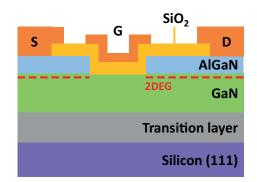

|   |      | 3.1.2                                   | Device structure and experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37       |

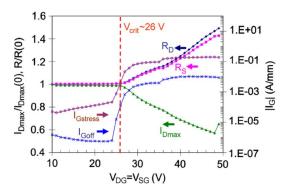

|   |      | 0.1.2                                   | Initial stabilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37       |

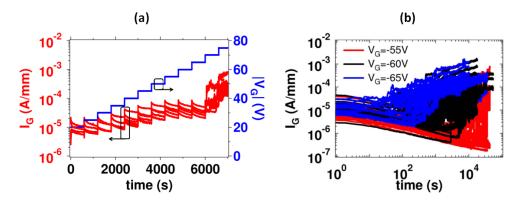

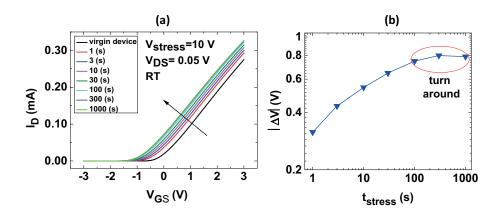

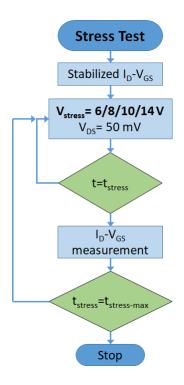

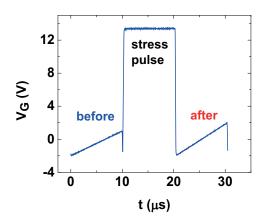

|   |      |                                         | Stress test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39       |

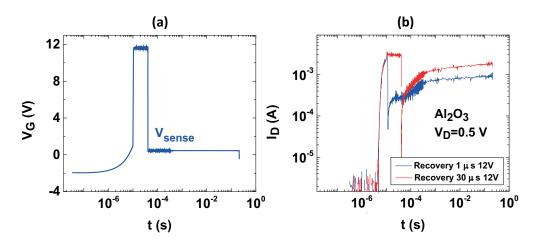

|   |      |                                         | Recovery test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39       |

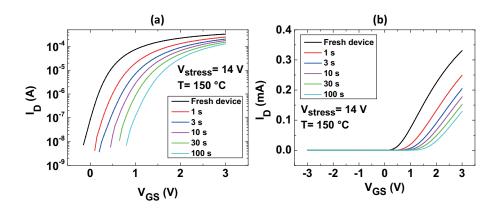

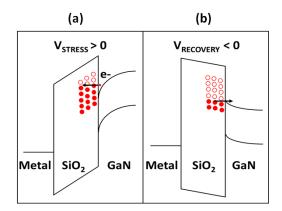

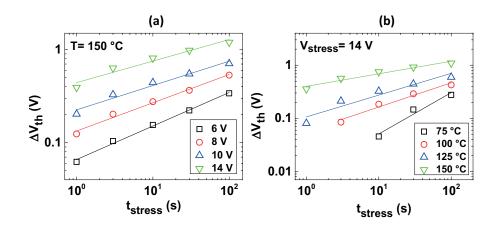

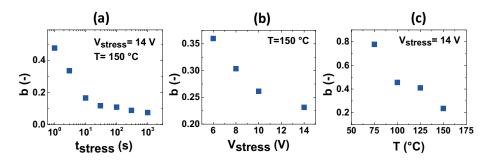

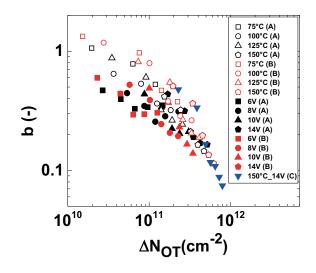

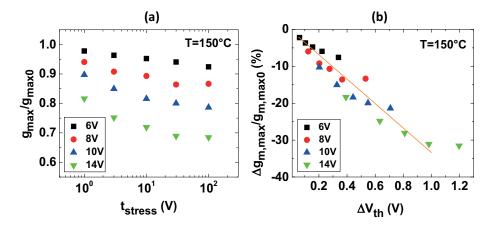

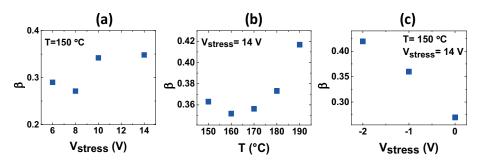

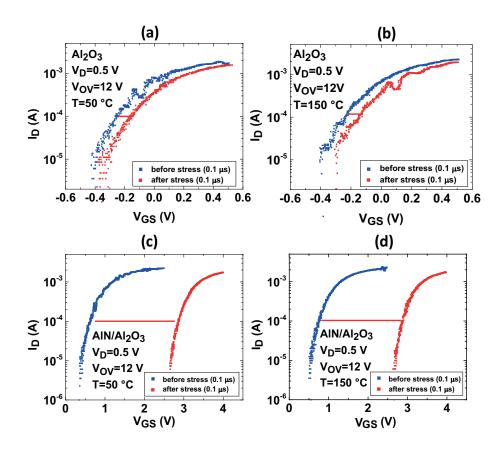

|   |      | 3.1.3                                   | Stress phase results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40       |

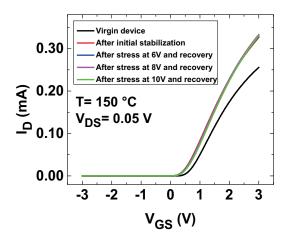

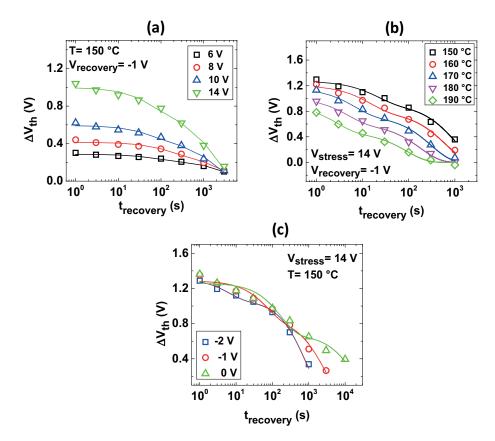

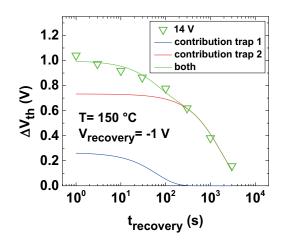

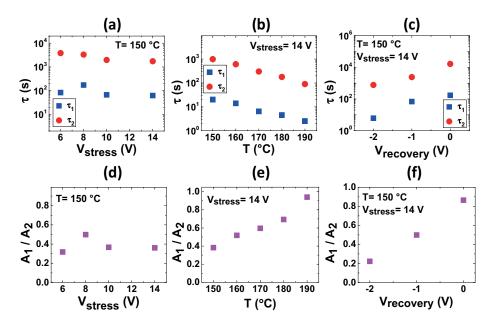

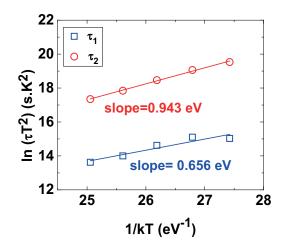

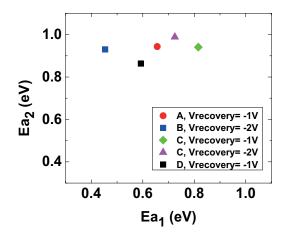

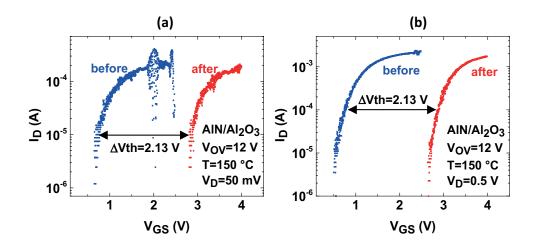

|   |      | 3.1.3<br>3.1.4                          | Recovery phase results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40<br>43 |

|   |      | 3.1.4                                   | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43<br>47 |

|   | 3.2  |                                         | ility impact of AlN layer sandwiched between the GaN and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47       |

|   | 5.2  |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48       |

|   |      | Al <sub>2</sub> O <sub>3</sub><br>3.2.1 | layers in recessed AlGaN/GaN MOS-HEMTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40<br>48 |

|   |      | 3.2.1                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40<br>50 |

|   |      | 3.2.2                                   | Experimental setup for the stress phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50<br>51 |

|   |      |                                         | Experimental setup for the recovery phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51       |

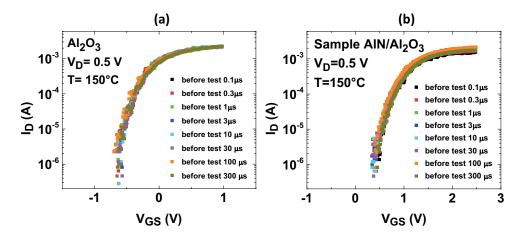

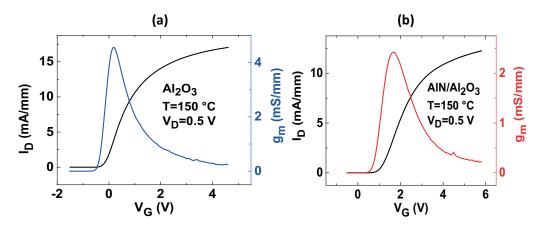

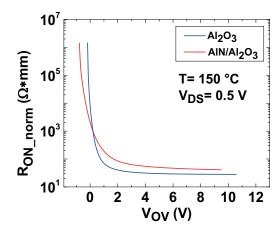

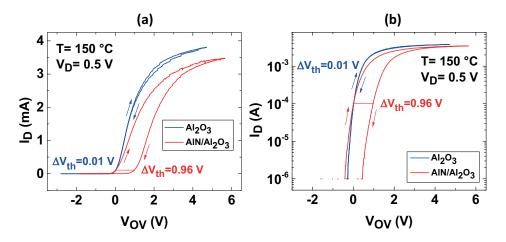

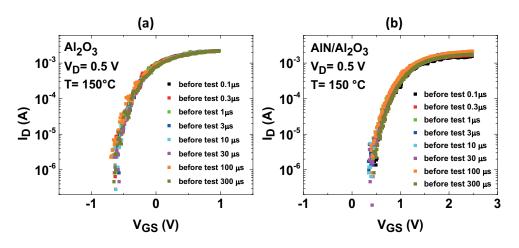

|   |      | 3.2.4                                   | General characteristics comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53<br>54 |

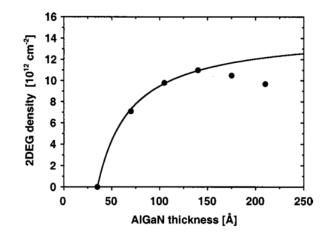

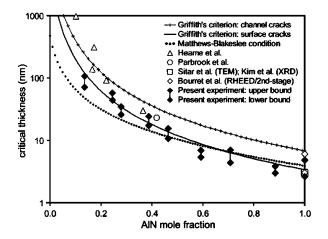

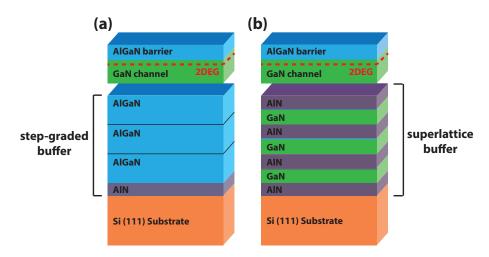

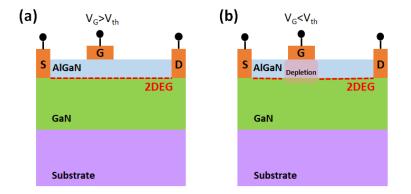

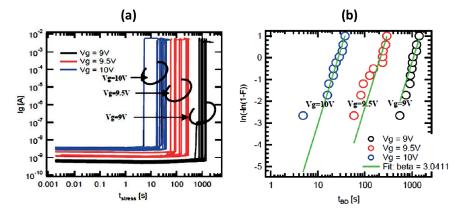

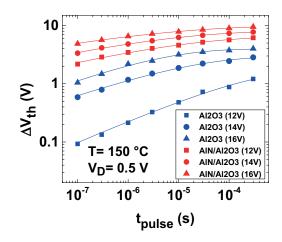

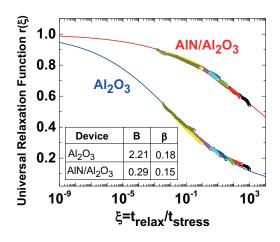

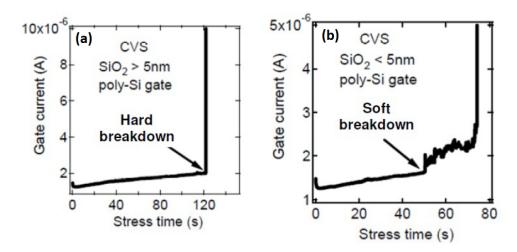

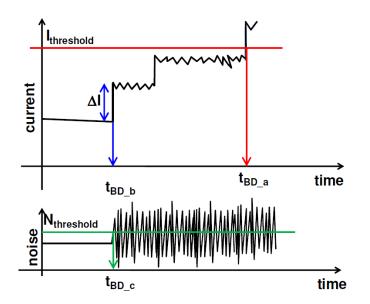

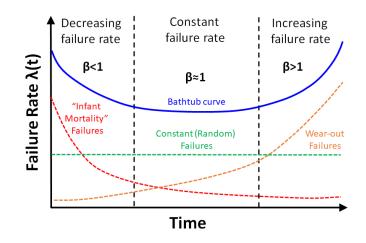

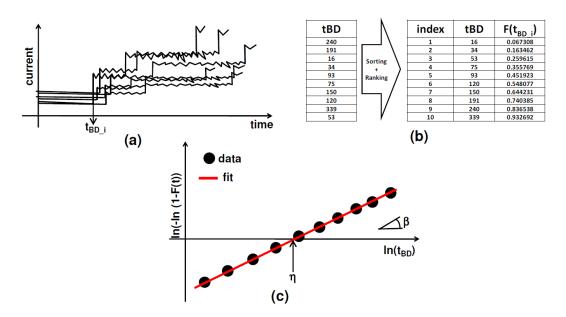

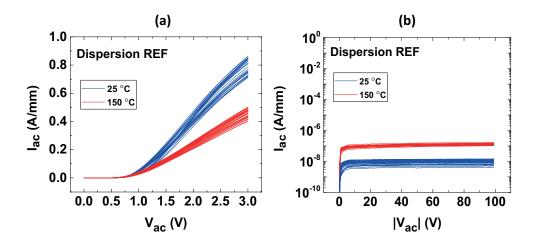

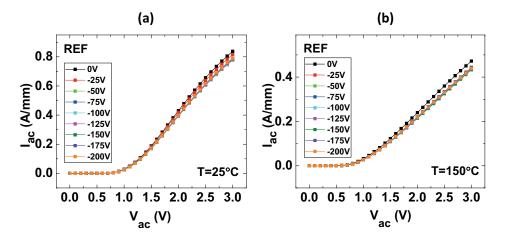

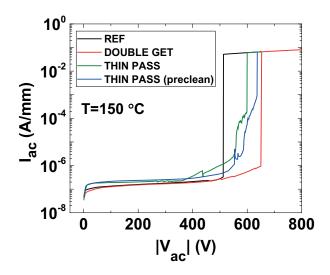

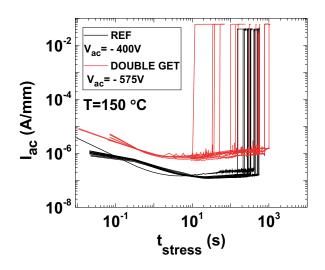

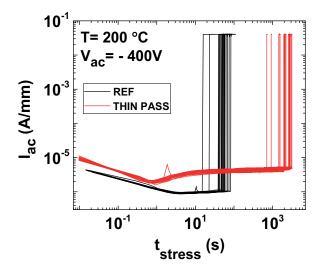

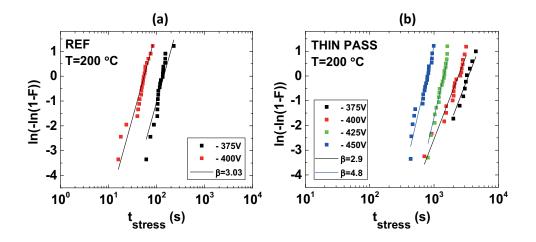

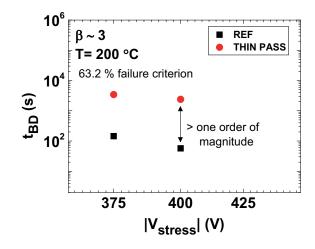

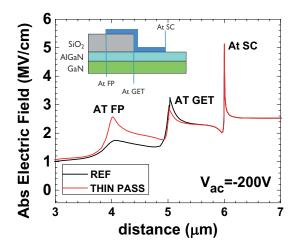

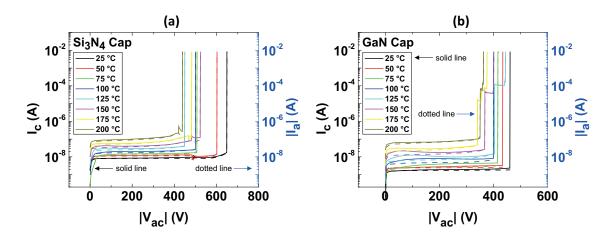

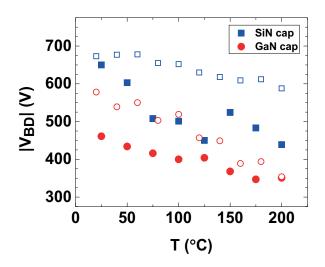

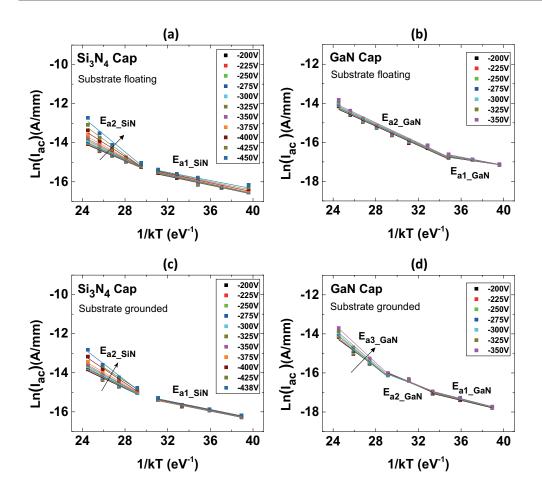

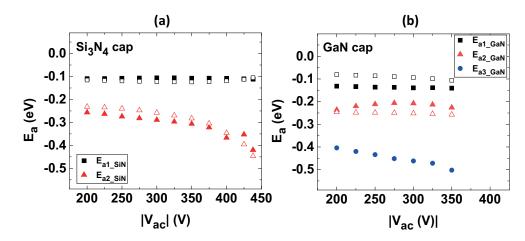

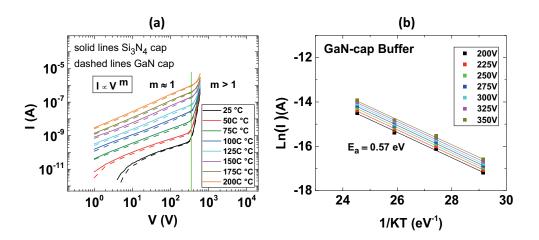

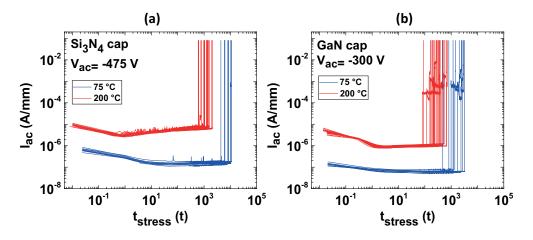

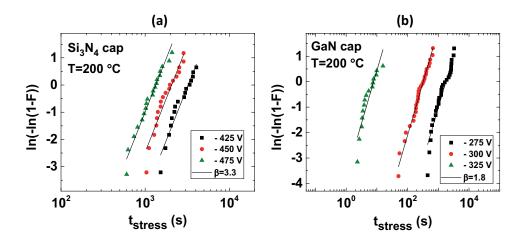

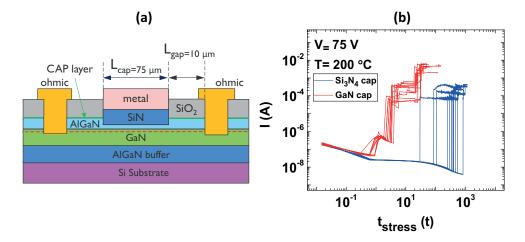

|   |      | 3.2.5                                   | Stress phase results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |