#### UNIVERSITA' DELLA CALABRIA

Dipartimento di Ingegneria Informatica, Modellistica, Elettronica e Sistemistica

#### Scuola di Dottorato

Archimede in Scienze, Comunicazione e Tecnologie

#### Indirizzo

Scienze e Tecnologie dei Sistemi Complessi

#### CICLO

XXVIII

#### TITOLO TESI

## Circuit and architecture solutions for the low-voltage, low-power domain

Coordinatore: Prof. Pietro Pantano Firma Sieto Sa AD

Supervisore/Tutor: Prof. Felice Crupi Firma

Dottorand ... Dott. Domenico Albano Firma

# **ABOUT THE AUTHOR**

Domenico Albano was born in Soriano Calabro (VV), Italy, on October 15<sup>th</sup>, 1986.

He received the "diploma di geometra" with full grade (100/100) from Istituto Tecnico per Geometri, L. Einaudi, Serra San Bruno (VV), Italy.

He received the Bachelor of Science degree in Electronic Engineering cum laude from University of Calabria, Rende (CS), Italy, in 2009. The title of the thesis was: Optimization of VLSI systems. The advisor was Prof. Manlio Gaudioso.

In 2012 he received the Master of Science degree in Electronic Engineering cum laude from University of Calabria, Rende (CS), Italy. The title of the thesis was: Design of an ultra-low power temperature compensated voltage reference. The advisors were Prof. Felice Crupi and Prof. Giuseppe Iannaccone.

In 2012 he started to work toward the Ph.D. degree in Electronic Engineering at University of Calabria. During the Ph.D. he worked with different research groups and universities as University of Pisa, University of Pavia, University of Singapore and Holst Centre, Eindhoven, The Netherlands.

In April 2012 he was visiting student at the University of Pisa where he designed an ultra-low voltage, low-power voltage reference.

From October 2013 to November 2014 he was a visiting Ph.D. student at the Department of Electrical, Computer, and Biomedical Engineering of the University of Pavia where he worked on the design of a low-power successive approximation register analog to digital converter.

From April 2015 to October 2015 he was a visiting Ph.D. student at the Holst Centre (IMEC), Eindhoven, The Netherlands, where he worked on the design of a new silicon Physical Unclonable Function for security applications.

His main research interests include the design of ultra-low voltage, low-power voltage references, current references, ADCs and Physical Unclonable Functions.

# **LIST OF PUBLICATIONS**

- [1] F. Crupi, D. Albano, M. Alioto, J. Franco, L. Selmi, J. Mitard, G. Groeseneken, "Impact of High-Mobility Materials on the Performance of Near- and Sub-Threshold CMOS Logic Circuits," *IEEE Transactions on Electron Devices*, vol. 60, n. 3, pp. 972-977, 2013.

- [2] **D. Albano**, F. Crupi, F.Cucchi and G. Iannaccone, "A Picopower Temperature-Compensated Subthreshold CMOS voltage reference", *International Journal of Circuit Theory and Applications*, 2013. DOI: 10.1002/cta.1925.

- [3] M. Lanuzza, R.Taco and **D. Albano**, "Dynamic Gate-level Body Biasing for Subthreshold Digital Design," in *IEEE 5th Latin American Symposium on Circuits and Systems* (LASCAS), Feb. 2014, pp. 25-28.

- [4] D. Albano, F. Crupi, F.Cucchi and G. Iannaccone, "A sub kT/q voltage reference operating at 150 mV", *IEEE Transactions on Very Large Scale Integrated Systems* (VLSI), pp. 1547 – 1551, Aug. 2015.

- [5] D. Albano, M.Lanuzza, R.Taco, F. Crupi, "Gate-Level Body Biasing for Subthreshold Logic Circuits: Analytical Modeling and Design Guidelines", *International Journal of Circuit Theory and Applications*, vol. 43, no 11, pp. 1523-1540, Nov. 2015.

- [6] D. Albano, M. Grassi and P. Malcovati, "A Low Power 12-Bit ENOB SAR ADC for Silicon Drift X and Gamma Ray Detector Read-Out", in *IEEE International Symposium on Circuits and Systems* (ISCAS), May 2015, pp. 297 – 300.

- [7] R. Taco, M. Lanuzza, **D. Albano**, "Ultra-Low-Voltage Self-Body Biasing Scheme and Its Application to Basic Arithmetic Circuits," *VLSI Design, Hindawi Publishing Corporation*, 2015.

# **INTRODUCTION TO THIS WORK**

As a consequence of the growing request for long lifetime portable, implantable and wearable electronic devices, low-power, low-voltage operation represents a mandatory requirement of the modern electronics. Applications like energy-harvesting systems, Body Area Network (BAN) systems, Radio Frequency Identification (RFID) systems and implantable medical devices, are requiring substantial improvements in term of energy-efficient operation to the circuit designers' community. In these systems complex mixed-signal electronics is used to pick up, process and transmit the signals coming from the environment or the human body. Among the different circuital blocks, bias circuits and signal processing modules like Analog to Digital Converters (ADCs), represent compulsory components of all these applications. Additionally, applications like wireless BAN and RFID systems, such as Near-Field-Communication (NFC) systems, have to deal with privacy-related issues. As an example in the case of the BAN systems the private information and the actions required to the actuators must be protected from possible attacks since any involuntary action can cause a risk for the patient. At the same time in the case of the NFC systems, commonly used for money transfer, the private information must be protected from potential frauds. For such a reason, in the majority of the energy-constrained applications, security is becoming a compulsory requirement as well as the energy efficiency operation.

In this work different circuits capable to satisfy to the requirements of the energy-constrained applications are presented.

In chapter 1 a brief introduction to some of the energy-constrained applications is reported. The main requirements are highlighted as well as the implications at design level.

In chapter 2 the behaviour of the MOSFET at device level is analysed. The main design considerations and issues of the MOSFET operating in the low-power, low-voltage regime are highlighted.

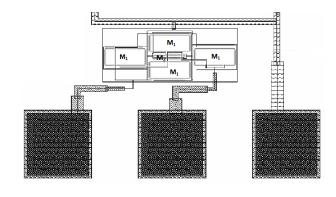

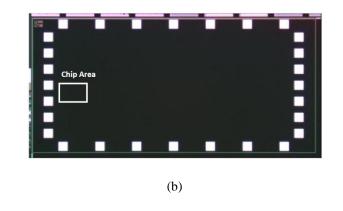

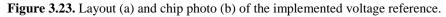

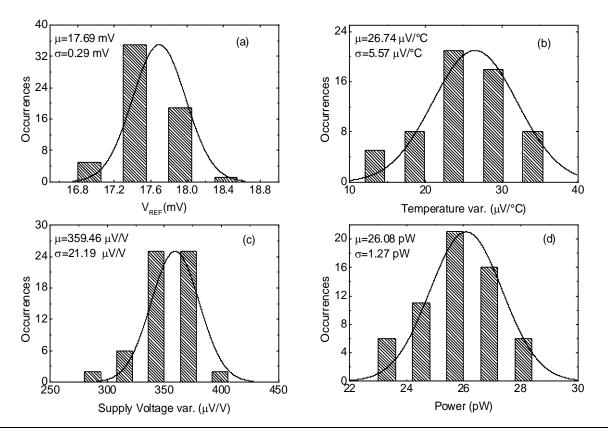

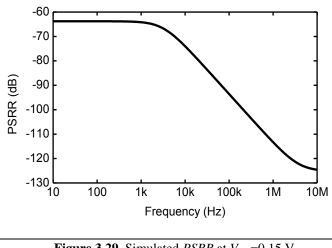

In chapter 3 two ultra-low voltage, low-power subthreshold voltage references are presented. First a brief overview of the different solutions proposed so far is reported. The two proposed solutions are then introduced. The first solution proposes a voltage reference capable of operating with a supply voltage of 0.45 V and with a power consumption of 40 pW while the second solution consists in the first kT/q voltage reference capable of operating with a supply voltage of only 150 mV while consuming 26.1 pW. For both solutions the main design considerations are explained in detail. Measurements results are analysed and compared with the state-of-the-art solutions.

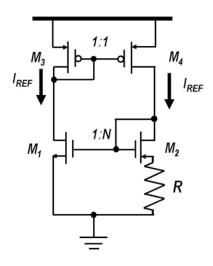

In chapter 4 the first subthreshold CMOS current reference operating at 0.5 V with a power consumption of only 40 nW is presented. Also here a brief overview on the main solutions proposed so far is reported. The operating principle of the proposed solution is analysed in detail. Measurements results are reported and compared with the other state-of-the-art solutions.

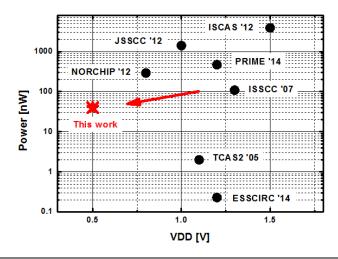

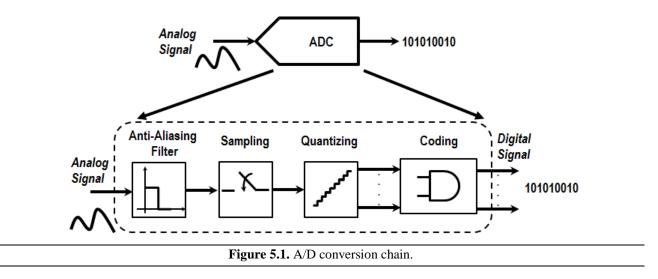

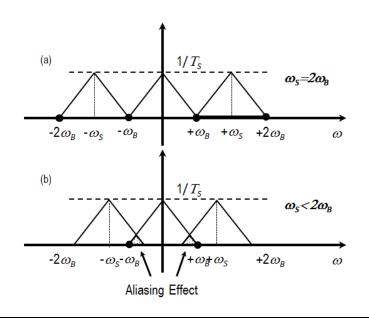

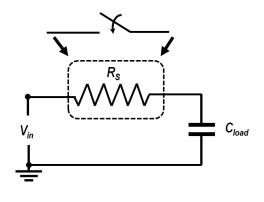

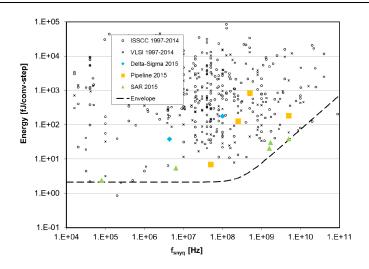

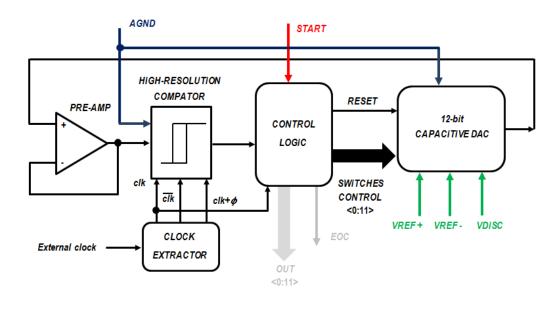

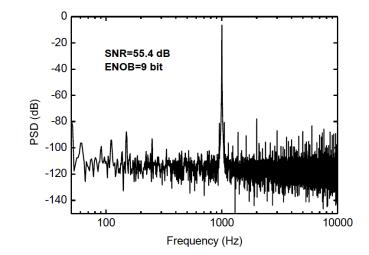

In chapter 5 a low-power Successive Approximation Register (SAR) Analog to Digital Converter (ADC) with an ENOB of 9 bits, a power consumption of only 0.27 mW and energy per conversion equal to 87 fJ/step, is reported. The architecture is explained in detail as well as the main design considerations. Measurement results are reported and compared with the other low-power SAR ADCs.

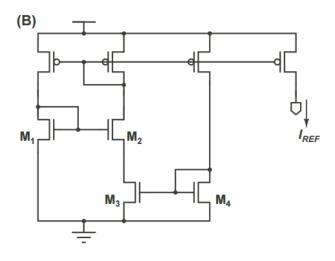

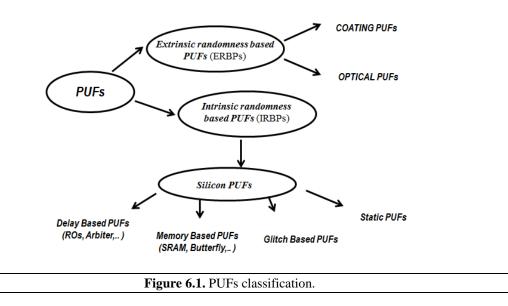

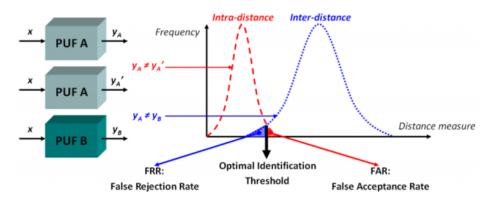

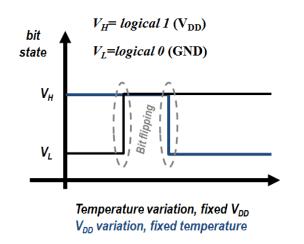

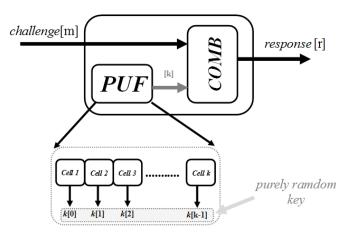

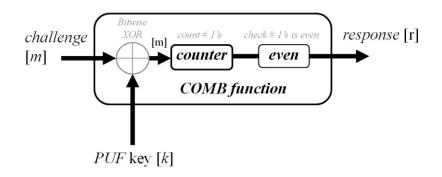

Finally in chapter 6 two innovative silicon Physical Unclonable Functions for data protection capable of operating at very low supply voltages are presented. In the first solution complementary current mirrors and an additional sense operational amplifier are employed to generate a random and robust secret key, while in the second solution a voltage divider consisting of two nMOS transistors is exploited to generate a secret key. For both solutions the main figures-of-merit in terms of uniqueness, randomness and reliability against malicious attacks are extracted. Simulation and measurement results are compared with the other state-of-the-art solutions.

# INDEX

| <b>CHAPTER 1. Low-Power, low-Voltage electron</b>        | ics   |

|----------------------------------------------------------|-------|

| 1.1. Introduction                                        |       |

| 1.2. Body Area Networks                                  |       |

| 1.3. Radio Frequency Identification (RFID) Systems       |       |

| 1.4. Energy Harvesting                                   |       |

| 1.5. Ultra-Low voltage VLSI design                       |       |

| 1.6. Low power, low-voltage analog design                |       |

| Bibliography                                             |       |

| <b>CHAPTER 2. CMOS Design in weak inversion</b>          |       |

| 2.1. Introduction                                        |       |

| 2.2. I-V MOSFET relationship                             |       |

| 2.2.1. Small signal behaviour                            |       |

| 2.2.2. Temperature effect                                |       |

| 2.2.3. Process stability                                 |       |

| Bibliography                                             |       |

| CHAPTER 3. Low -voltage, low-power subthree              | shold |

| voltage references                                       |       |

| 3.1. Introduction                                        |       |

| <b>3.2.</b> Voltage reference performance specifications |       |

| 3.2.1. Line sensitivity                                  |       |

| 3.2.2. Temperature coefficient                           |       |

| 3.2.3. Power-Supply-Rejection-Rate (PSRR)                |       |

| 3.2.4. Process stability                                 |       |

| 3.3. Voltage references                                  |       |

| 3.3.1. Low-voltage, low-power voltage references         |       |

| 3.3.2. Subthreshold voltage references                   |       |

| 3.3.3. Fully-subthreshold CMOS references                |       |

| 3.4. Proposed Voltage Reference 1                        |       |

| 3.4.1. Introduction                                      |       |

| 3.4.2. Operating principle                               |       |

| 3.4.3. Design considerations                                |    |

|-------------------------------------------------------------|----|

| 3.4.3.1. Subthreshold conduction and threshold voltage      |    |

| constraint                                                  |    |

| 3.4.3.2. Minimum supply voltage                             |    |

| 3.4.3.3. Supply voltage variations                          |    |

| 3.4.3.4. Voltage temperature parameter                      |    |

| 3.4.3.5. Process variations                                 |    |

| 3.4.3.6. Transistor sizing                                  |    |

| 3.4.3.7. Process stability improvement                      |    |

| 3.4.4. Experimental results                                 |    |

| 3.4.5. Conclusion                                           |    |

| 3.5. Proposed voltage reference 2                           |    |

| 3.5.1. Introduction                                         |    |

| <b>3.5.2.</b> Operating principle and design considerations |    |

| 3.5.3. Measurement results                                  |    |

| 3.5.4. Conclusion                                           |    |

| Bibliography                                                |    |

| <b>CHAPTER 4. Design of a low-power, low-voltage</b>        |    |

| subthreshold current reference                              |    |

| 4.1. Introduction                                           |    |

| 4.2.CMOS current references                                 |    |

| 4.3.Proposed current reference                              |    |

| 4.3.1. Introduction                                         |    |

| 4.3.2. Schematic and main design considerations             |    |

| 4.3.3. Experimental results                                 |    |

| 4.4.Conclusion                                              |    |

| Bibliography                                                |    |

| <b>CHAPTER 5. Design of a low-power SAR Analog</b>          | to |

| Digital Converter                                           |    |

| 5.1. Introduction                                           |    |

| 5.2. ADC specifications                                     |    |

| 5.2.1. Static performances                                  |    |

| 5.2.2. Dynamic performances                                 |    |

| 5.3. ADC architectures                                      |    |

| 5.3.1. Flash ADC                                            |    |

| 5.3.2. Pipeline ADC                                         |    |

| 5.3.3. Sigma-Delta ( $\Sigma\Delta$ ) ADC                   |    |

| 5.3.4. Successive Approximation Register (SAR) ADC          |    |

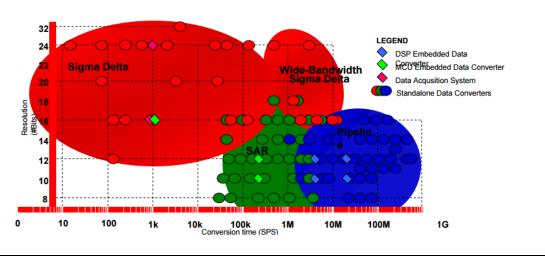

| 5.3.5. ADCs comparison                                               | 87  |

|----------------------------------------------------------------------|-----|

| 5.4. Proposed SAR ADC                                                | 91  |

| 5.4.1. Introduction                                                  | 91  |

| 5.4.2. Architecture and main design considerations                   | 91  |

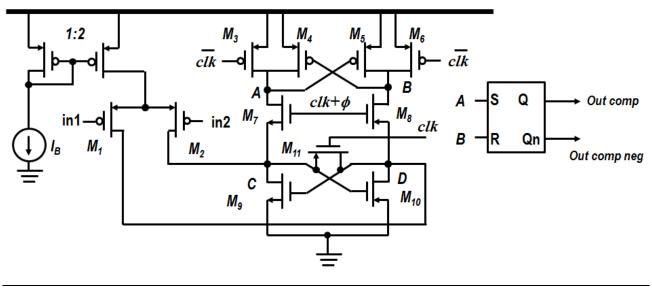

| 5.4.2.1. Comparator                                                  | 92  |

| 5.4.2.2. Pre-Amplifier                                               | 94  |

| 5.4.2.3. Clock generator                                             | 95  |

| 5.4.2.4. Capacitive DAC                                              | 95  |

| 5.4.2.5. Successive approximation register                           | 99  |

| 5.4.3. Layout                                                        | 100 |

| 5.4.4. Simulation and experimental results                           | 103 |

| 5.4.5. Conclusion                                                    | 106 |

| Bibliography                                                         | 108 |

| CHAPTER 6. A new class of low-voltage Analog                         |     |

| Physical Unclonable Functions                                        | 110 |

| 6.1. Introduction                                                    | 110 |

| 6.2. An overview on physical unclonable functions                    | 110 |

| 6.2.1. PUFs specifications                                           | 111 |

| 6.2.1.1. Uniqueness                                                  | 111 |

| 6.2.1.2. Randomness                                                  | 112 |

| 6.2.1.3. Reliability                                                 | 112 |

| 6.2.2. Main PUF solutions                                            | 113 |

| 6.2.2.1. Silicon PUFs                                                | 114 |

| 6.2.2.1.1. Delay- based PUFs                                         | 114 |

| 6.2.2.1.1.1. Arbiter PUFs                                            | 114 |

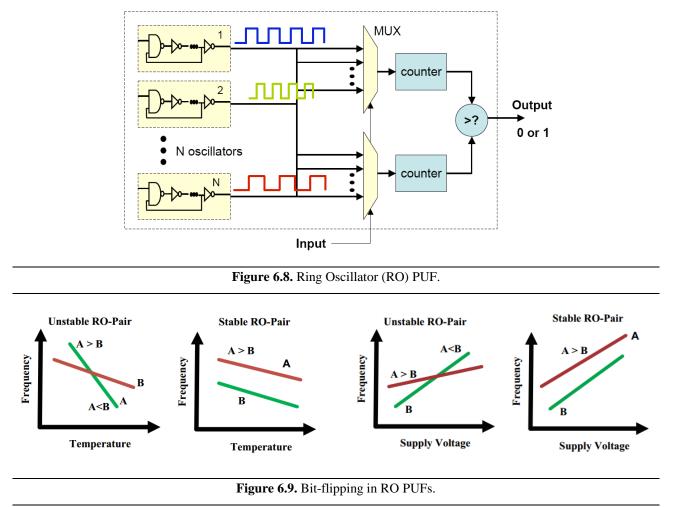

| 6.2.2.1.1.2. Ring oscillator PUFs                                    | 116 |

| 6.2.2.1.2. Memory-based PUFs                                         | 116 |

| 6.2.2.1.3. Considerations on delay-based and                         |     |

| memory-based PUFs                                                    | 117 |

| 6.3. Proposed solution 1: Complementary current mirrors<br>based PUF | 119 |

| 6.3.1. Introduction                                                  | 119 |

| 6.3.2. Architecture of the proposed PUF                              | 119 |

| 6.3.3. Basic solution: complementary current                         |     |

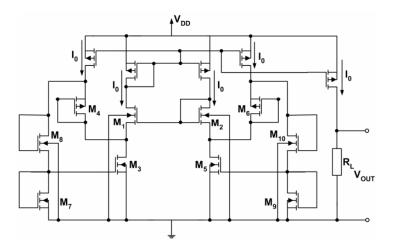

| current mirrors (CCMs)                                               | 121 |

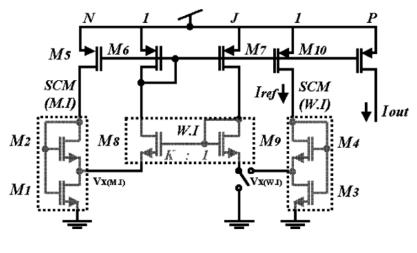

| 6.3.4. Complementary stacked current mirrors (k-CCMs)                | 122 |

| 6.3.5. Sense op-amp PUFs                                             | 123 |

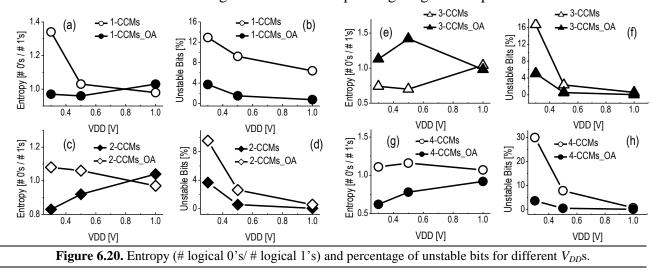

| 6.3.6. Simulated and measured results                                | 124 |

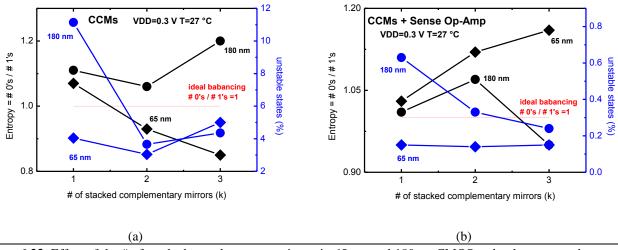

| 6.3.6.1. Impact of the stacking factor <i>k</i>                      | 124 |

| 6.3.6.2. Impact of the supply voltage and temperature  |     |

|--------------------------------------------------------|-----|

| variations                                             | 125 |

| 6.3.6.3. Inter-PUF and intra-PUF HD                    | 127 |

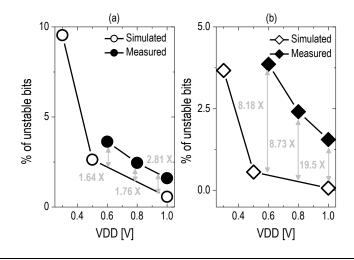

| 6.3.6.4. Comparison between measured and               |     |

| simulated results                                      | 129 |

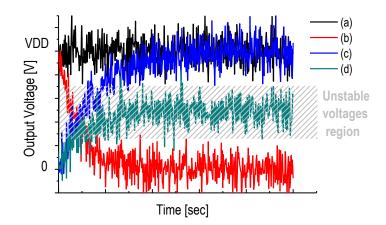

| 6.3.6.5. Stability against supply noise                | 130 |

| 6.3.6.6. Technology impact                             | 132 |

| 6.3.7. Conclusion                                      | 133 |

| 6.4. Proposed solution 2: A 2T voltage divider PUF     | 134 |

| 6.4.1. Introduction                                    | 134 |

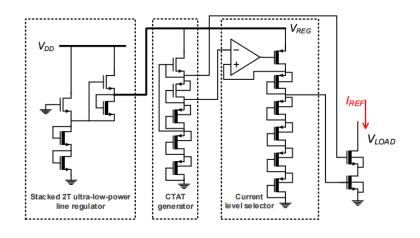

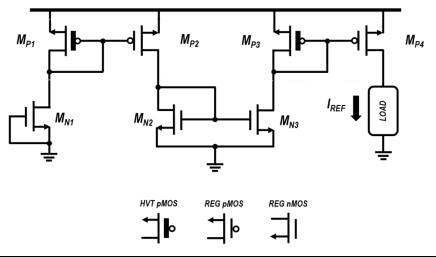

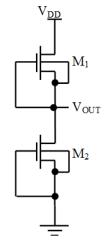

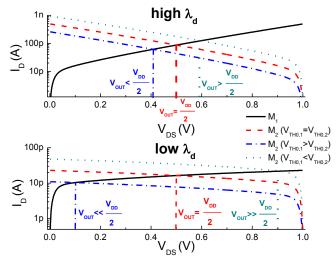

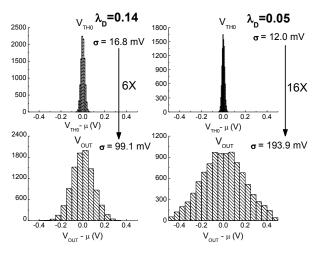

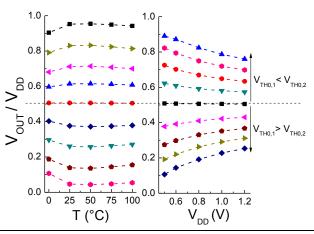

| 6.4.2. Proposed circuit solution                       | 134 |

| 6.4.3. Simulation setup and FOMs                       | 137 |

| 6.4.4. Simulation results                              | 138 |

| 6.4.4.1. Analysis and optimization of the voltage pair |     |

| divider pair                                           | 138 |

| 6.4.4.2. Impact of the output stage                    | 142 |

| 6.4.5. Conclusion                                      | 143 |

| Bibliography                                           | 144 |

| CONLUSIONS AND FUTURE DEVELOPEMENTS                    | 146 |

# **1. Low-Power, Low-Voltage Electronics**

# **1.1. Introduction**

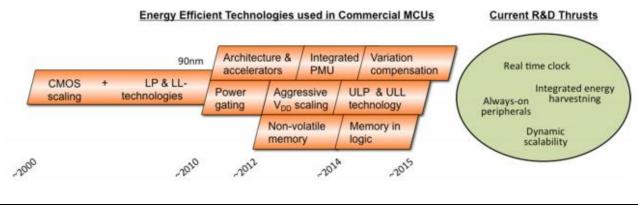

Energy efficiency represents the main technology driver of the modern electronics. Indeed, the progresses in every single branch of the integrated electronics, from RF systems to data converters, wireless sensor networks, Internet of Things (IoT), digital and analog systems, are measured in terms of power consumption or energy efficiency [1]. These requirements are becoming so critical that both manufacturers and designers have been introduced different methodologies to address this problem at different levels, from variations in the semiconductor manufacturing process to the implementation of design techniques for low-power consumption. As an example in Figure 1.1 the different energy efficiency techniques exploited in microcontroller design during the last 15 years are reported [1]. Since the simple technology scaling is not in able to ensure good performances anymore, other techniques like *aggressive voltage scaling*, *Ultra-Low Power* (ULP), *Ultra Low-Leakage* (ULL) technologies and *compensation for variability on CMOS process* have been exploited during the last years to achieve better results.

Nowadays the concepts of energy efficiency and minimum power consumption are becoming even more critical as a consequence of the explosion of applications like wearable, portable and handheld devices [2]-[5]. Indeed, in this kind of applications saving power is extremely important since the sizes of the devices are usually very small and only a limited space is available for the source of energy (i.e. battery). Because of this limited amount of energy, the complex electronics used to process and transmit the signals has to ensure the lowest possible amount of energy consumption both in idle and active mode. Additionally, in applications such as the implantable medical devices, saving energy is a mandatory requirement since battery replacement brings usually to an invasive procedure for the patient. With the main aim of understanding the different requirements of the low-power and low-energy electronics, in the following some of the main ultra-low power contexts are briefly introduced.

# 1.2. Body Area Networks

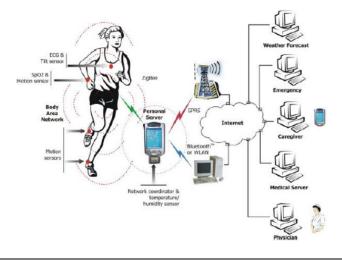

The extreme low-power, low-voltage operation is particular attractive in the Body Area Networks (BAN) scenario. BAN is an emerging technology that has the potential to revolutionize next-generation of healthcare, entertainment, and other personal applications [1]. This technology exploits wireless communications protocols that allow low-powered sensors to communicate with another one and transmit data to a local base station and to remote places like hospitals [3]. A particular kind of BAN is represented by the Body-Channel Communication (BCC) systems in

which the human body is used as transmission medium. Both WBANs and WBCCs allow monitoring the person's vital signs, as shown in Figure 1.2.

Thus both WBANs and WBCCs use sensors on and/or in the human body, which are responsible for sensing the main biological signals such as temperature, heart rate, movements, electrocardiogram, blood pressure, oxygen saturation, etc. These data sets are collected ensuring reliability, security, and accuracy since any possible mistake can compromise the quality of life of the patient.

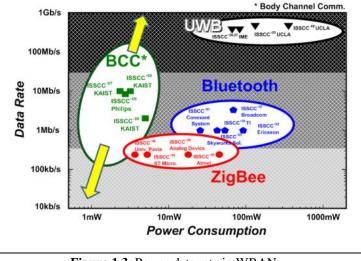

WBAN and WBCC systems can achieve high-speed communication with low energy consumption compared to other personal-area network (PAN) solutions such as ZigBee, Bluetooth, and UWB.

Figure 1.1. Energy efficiency techniques in microcontroller design.

From Figure 1.3 it is possible to note that BAN systems fall in a unique region of the power vs data rate trade-off that makes the concept of power consumption particular challenging. As explained before the key point of such systems is to continuously monitor a person's health status from a central station or hospital without impeding the person's mobility [3]. Depending on the application, some sensors will require a battery lifetime of months, years, or only a few hours [3].

#### Figure 1.2. BAN system.

To be less invasive as possible, a BAN system is very small in size, which means that only a limited amount of energy for the proper operation of the different blocks is available. For such a reason a very power-efficient protocol (IEEE802.15.6) has been introduced for this particular application. However the power efficient protocol alone is not in able to achieve the previous targets in terms of

lifetime. In fact the nodes (sensors) in a WBAN system are extremely energy constrained since they have to process the data in the fastest and most efficient way while consuming a very small amount of energy both in active and idle mode.

Figure 1.3. Power-data rate in WBANs.

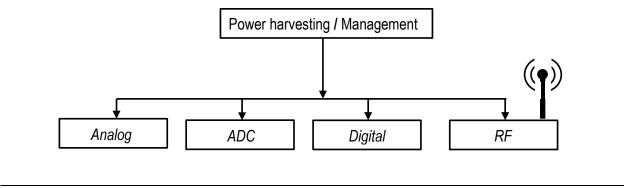

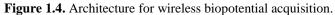

From the design point of view this means that every single circuit involved in the signal processing of the vital data should be designed in order to consume the lowest amount of energy without compromising the performance in terms of resolution, speed, stability and reliability. The sensors which are commonly used in the previous low-energy contexts consist of analog, digital and mixed-signal circuits. For better understanding the electronics behind this application, in Figure 1.4 the architecture for a wireless biopotential acquisition is reported. The system consists of an analog front-end, a digital signal processor, an ADC, an RF transmitter and a harvesting and management unit control. In addition to the previous requirements, as reported before, in the context of the WBAN systems the identification is a critical step as well as the performance from the energy point of view. The private information and eventually the actions required to the sensors / actuators in WBANs systems should be protected from possible attacks since any involuntary action can cause a risk for the patient [4]. Despite the great efforts both in designing energy efficient electronics and reliable authentication protocols a lot of efforts are still necessary in WBANs systems design [4].

# 1.3. Radio Frequency Identification (RFID) Systems

The term Radio Frequency IDentification (RFID) system is used to indicate a short range radiofrequency technology in which a reader and an electronic tag can exchange data with the main goal of identification and tracking [5]. The very first implementation of an RFID system was reported in [6] in 1948 in the article entitled "*Communication by means of reflected power*".

In 1950 Watson-Watt, the responsible of a secret project in UK, developed the first active Identify Friend or Foe (IFF) system. A transmitter was putted on each British plane. When the plain received signals from radar stations on the ground, it began broadcasting a signal back that identified the aircraft as friendly. All the modern RFIDs systems work on this same basic concept. A signal is sent to a transponder, which wakes up and either reflects back a signal (passive system) or broadcasts a signal (active system) [7].

In the 1960 two companies *Sensormatic* and *Checkpoint* were founded for developing Electronic Article Surveillance (*EAS*). They introduced the first commercial prototype. In this case, the transponder was characterized by a single-bit output, representing its presence or absence. In 1990 IBM introduced the first high frequency (UHF) RFID system. The range covered by the system was extended to about 6 meters in the best condition, moreover a faster transfer data rate was guarantee compared to the 125 KHz and 13.56 MHz applications. This project was developed by IBM in collaboration with Wal-Mart, an American multinational retail corporation that operates a chain of discount department stores and warehouse stores. Despite that the UHF RFID developed by IBM was never commercialized [8]. Only in 1999 the RFID technologies start to become popular. Uniform Code Council, EAN International, Procter & Gamble and Gillette put up funding to establish the Auto-ID Center at the Massachusetts Institute of Technology to do some research about the feasibility of putting low-cost RFID tags on all products made to track them through the supply chain. Their idea was to put only a simple microchip that stored very little information instead to put a more expensive complex chip with more memory [7]-[8].

The RFIDs can be classified in different categories. The main classification takes into account the transponder power supply. Based on this the RFID can be: *active, semi-passive* and *passive*.

Active RFIDs incorporate a battery to transmit a signal to a reader antenna. They allow very lowlevel signals to be received by the tag. Usually they are designed in order to stay in idle mode for saving power for most of the time emitting a signal at a predefined interval or transmitting only when addressed by a reader. As a result of the built-in battery, an active RFID tag can be used at large distances from the reader. However they show limited life, due to the limited energy in the battery, and higher costs.

*Semi-passive* tags have an on-board power source, such as a battery, which is used to provide the power to the microchip's circuitry. Despite the battery a semi-passive tag communicates by drawing power from the reader. Semi-passive tags show greater range than totally passive tags and have the ability to monitor sensor inputs even when they are not in the presence of an RF field.

*Passive* tags do not have an integrated power source thus they are generally powered by the reader antenna through an antenna located on the tag. The power transmission is performed through induction thanks to a specially designed antenna which generates a small voltage potential. Passive tags have in general a short-distance operating range. The power supply is typically generated using an energy harvester that converts the RF voltage coming from the antenna in a constant voltage used to supply the circuit.

RFID systems can operate at a number of designated frequencies, depending on the application requirements. Usually an RFID can be classified in the following categories: Low Frequency (125

kHz), High Frequency (13.56MHz), Ultra High Frequency (860-960 MHz) and Microwave (2.45 GHz).

A block diagram of a commercial RFID tag is reported in Figure 1.5 [9]. The main blocks are the envelope or peak detector, demodulator (consisting of an amplifier, a Schmitt trigger, an offset cancellation circuit, etc), the bias bandgap reference circuit (BGR) and the clock generator. All of these circuits are designed for low power operation in order to achieve an ultra-low power RFID tag chip.

Figure 1.5. Semi-passive RFID Block Diagram [9].

Figure 1.6. NFC mobile payment system.

Another important issue regarding RFIDs is the level of security. RFIDs are increasingly being used in manufacturing, pharmaceutical and military sector for tagging, tracking and locating. The widespread item-level RFID tagging of products such as clothing and electronics raises public concerns regarding personal privacy.

Thus RFID chips carry on personal information which in some cases should be protected from attacks. As a consequence several works are trying to solve this problem by implementing reliable systems for the protection of the intellectual property at chip level. A promising solution consists in Physical Unclonable Function exploiting the variability in CMOS process [10]-[13].

A particular kind of RFID system in which security is the main issue is represented by the Near-Field-Communication (NFC). It operates at 13.56 MHz on ISO/IEC 18000-3 standard [14]. NFC is nowadays commonly used for mobile payments (see Figure 1.6) [15]-[17].

# **1.4. Energy Harvesting**

Energy harvesting circuits convert the energy existing in a generic environment like linear motion, pressure, light, differences in temperature, into energy that can be used electrically.

A plenty of products that convert energy from Vibration (Piezo), PhotoVoltaic (Solar) and Thermal (TEC, TEG, Thermopiles, Thermocouples) sources are already on the market [18]. They provide high efficiency conversion to regulated voltages or to charge batteries and super capacitor storage elements. Usually these systems use boost capable of operating with a very low input signal, from 20mV [18] down to 10mV [19].

In this context of battery-free systems a small amount of energy is available, typically in the  $\mu$ W/cm<sup>2</sup> order of magnitude [20].

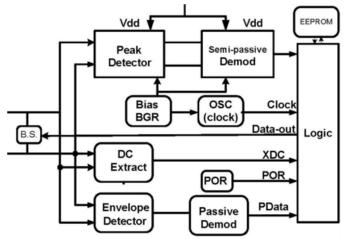

As a consequence the complex IC which has to manage the harvesting process has to ensure ultralow power operation. Moreover the electronics in these systems has to manage the problem of the intermittent and small amount of energy coming from the source. A typical energy-harvesting system is shown in Figure 1.7. It includes conversion, temporary storage block, a sophisticated power management circuit (MPPT), analog converters and ULP MCUs. From the design point of view the harvesting system poses several specifications like ultra-low leakage current, ultra-low voltage operation, very low power ADC with medium-high resolution.

# 1.5. Ultra-Low voltage VLSI design

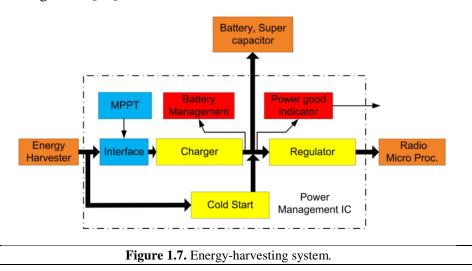

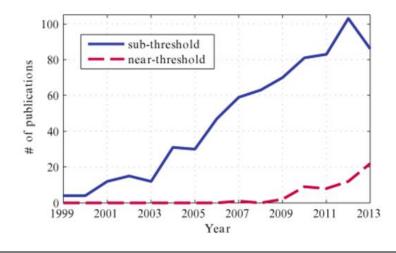

Figure 1.7 reports the operating supply voltage as a function of the technology node considering the publications on digital circuits design [21]. Most of the published works show a typical operating voltage of about 150 -200 mV with a minimum operating voltage of only 100 mV. It is really interesting also to take a look to the evolution of the publications over the years considering the operating regime of the circuits. This can be depicted by inspecting Figure 1.8 where the publications are classified based on the operating regime [21]. It is possible to note the exponential increasing in the number of publications in which the subthreshold regime is exploited. As an example, considering the year 2013, the works in subthreshold regime are about 4 times more than the works considering the near-threshold regime.

Figure 1.8. Minimum  $V_{DD}$  as a function of the technology node for digital systems [21].

Figure 1.9. Publications on VLSI circuits over the years. The data are extracted from the IEEE Xplore database [21].

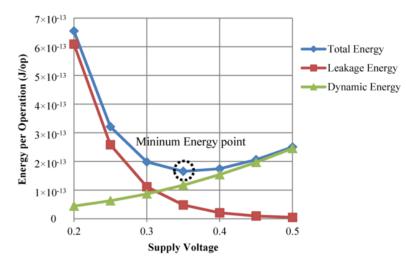

Again, the main reason of such a trend consists in the research of the maximum energy-efficiency or the minimum energy point (MEP). Combining the information reported in Figure 1.8 and Figure 1.9 the majority of the works in VLSI systems is performed in the direction of lowering the supply voltage in order to achieve subthreshold / near threshold conduction.

Figure 1.10. Dynamic, static and total energy in VLSI systems. The figure indicates the minimum energy point (MEP).

In fact, as well know, lowering the supply voltage has always a positive implication on the power consumed by the VLSI systems [22]-[24], as shown in Figure 1.10.

It is worth noting that subthreshold conduction ensures very low level of dynamic consumption while increasing the impact of the leakage current (subthreshold current). A lot of research is investigating what is the best region in terms of minimum energy point. Some claim the near-threshold conduction as the best [25]-[26], while in other systems the subthreshold seems the optimal operating regime for maximizing the energy efficiency of the systems [27]-[28].

# 1.6. Low power, low-voltage analog design

As shown before the supply voltage scaling is one of the most efficient ways to scale power consumption and to achieve energy efficient operation. This technique is particular efficient in the digital design context since the dynamic power consumption in a VLSI circuit scales by scaling the supply voltage. This concept is not true in the case of an analog circuit. Here the power consumption is defined by the energy necessary to ensure the proper operation of the circuit [29]. Specifically it is defined as the power consumed in analog signal processing circuits to maintain the signal energy above the fundamental thermal noise in order to achieve the required signal-to-noise ratio (SNR) [29]. The research of the minimum supply voltage and the minimum power consumption is still challenging from the design point of view of an analog system and a lot of research is still required in this field as reported in the technology trends report of the ISSCC [1]:

"The efficient control, storage, and distribution of energy are worldwide challenges, and are increasingly important areas of analog circuit research. While the manipulation and storage of information is efficiently performed digitally, the conversion and storage of energy is fundamentally performed with analog systems. Therefore, the key technologies for power management are collected from the environment via photovoltaic, piezoelectric, or thermoelectric transducers, with a trend toward the use of multiple sources at the same time. A significant focus here is on analog circuits that are able to harvest sub-microwatt power levels from multiple energy sources at tens of millivolts, to provide autonomy for remote sensors, or to supplement conventional battery supplies in mobile devices. To achieve this, the attendant analog circuits have to consume extremely low power, so that some energy is left over to charge a battery or supercapacitor. ......Analog circuits also serve as bridges between the digital world and the analog real world. Just like actual bridges, analog circuits are often bottlenecks and their design is critical to overall performance, efficiency, and robustness. Nevertheless, since digital circuits, such as microprocessors, drive the market, semiconductor technology has been optimized relentlessly over the past 40 years to reduce their size, cost, and power consumption. Analog circuitry has proven increasingly difficult to implement using these modern IC technologies. For example, as the size of transistors has decreased, the range of analog voltages they can handle as well as their analog performance have decreased, while the variation observed in the analog parameters has increased."

# **Bibliography**

- [1] **ISSCC 2015 tech trends**. http://isscc.org/doc/2015/isscc2015\_trends.pdf.

- [2] K.A. A. Makinwa, A. Baschirotto, P. Harpe, Efficient Sensor Interfaces. Advanced Amplifiers and Low Power RF Systems, *Springer*, 2015.

- [3] http://zeitgeistlab.ca/doc/Advanced\_WBANs\_for\_an\_Ageing\_e-Health\_Society.html

- [4] E. Sazonov, M. Neuman, Wearable Sensors. 1st edition, *Elsevier*, 2014.

- [5] J. Landt, "The History of RFID", in *IEEE Potentials*, vol. 24, no. 4, Oct.-November 2005, pp. 8-11.

- [6] H. Stockman, "Communication be means of reflected power", in *Proceeding of IRE*, vol. 36, no. 10, October 1948, pp. 1196-1204.

- [7] http://www.rfidjournal.com/articles/view?1338.

- [8] L. Yang, A. R. Manos M. Tentzeris, Design and Development of Radio Frequency Identification (RFID) and RFID-Enabled Sensors on Flexible Low Cost Substrates. Morgan & Claypool Publishers, 2009.

- [9] http://www.prototypexpress.com/rfidwhitepaper.htm.

- [10] S. Devadas, E. Suh, S. Paral, R. Sowell, T. Ziola, V. Khandelwal, "Design and Implementation of PUF-Based Unclonable RFID ICs for Anti-Counterfeiting and Security Applications", in *IEEE International Conference on RFID The Venetian*, 2008, pp. 58-64.

- [11] L. Bolotnyy and G. Robins, "Physically Unclonable Function -Based Security and Privacy", in RFID Systems, in *Proceedings of the IEEE International Conference on Pervasive Computing and Communications*, 2007, pp. 211-220.

- [12] http://www.rfidjournal.net/PDF\_download/Verayo\_031610\_Webinar.pdf.

- [13] H. Dirk, **RFID Security and Privacy**. Springer, 2008.

- [14] https://en.wikipedia.org/wiki/Near\_field\_communication.

- [15] http://www.mastercard.com/contactless/.

- [16] http://www.maestrocard.com/at/privatkunden/innovation\_kontaktlos.html.

- [17] https://developer.visa.com/paywavemobile.

- [18] http://www.linear.com/products/energy\_harvesting.

- [19] M. B. Machado, M. Sawan, M. Cherem Schneider; C Galup-Montoro, "10 mV 1V step-up converter for energy harvesting applications", in *Proceeding of the 27th Symposium on Integrated Circuits and Systems Design* (SBCCI), 2014, pp. 1-5.

- [20] http://www.mouser.com/pdfDocs/TI-ULP-meets-energy-harvesting-A-game-changing-combination-for-design engineers.pdf.

- [21] N. Reynders, W. Dehaene, Ultra-Low-Voltage Design of Energy-Efficient Digital Circuits. Springer 2015.

- [22] A. Wang, A. Chandrakasan, and S. Kosonocky, "Optimal supply and threshold scaling for subthreshold CMOS circuits," in *Proceeding of the IEEE Annual Symposium on VLSI*, Apr. 2002, pp. 5–9.

- [23] A. Wang and A. Chandrakasan, "A 180-mV subthreshold FFT processor using a minimum energy design methodology," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 1, pp. 310–319, Jan. 2005.

- [24] H. Soeleman, K. Roy, and B. C. Paul, "Robust subthreshold logic for ultralow power operation," *IEEE Transaction on Very Large Scale Integrated* (VLSI) *Systems*, vol. 9, no. 1, pp. 90–99, Feb. 2001.

- [25] Ronald G. Dreslinski, Michael Wieckowski, David Blaauw, Dennis Sylvester, Trevor Mudge, "Near-Threshold Computing: Reclaiming Moore's Law Through Energy Efficient Integrated Circuits," in *Proceedings of the IEEE, Special Issue on Ultra-Low Power Circuit Technology*, vol. 98, no. 2, February 2010, pp. 253 – 266.

- [26] Bo Zhai, Ronald G. Dreslinski, Trevor Mudge, David Blaauw, Dennis Sylvester, "Energy Efficient Near-threshold Chip Multi-processing," in ACM/IEEE International Symposium on Low-Power Electronics and Design (ISLPED), August 2007, pp.32-37.

- [27] A. Pajkanovic, T.J. Kazmierski, B. Dokic, "Minimum energy point of sub-threshold operated passtransistor circuits," in *IEEE Forum on Specification and Design Languages* (FDL), Sep. 2012, pp.202-2007.

- [28] A. Wang, B.H. Calhoun, A. Chandrakasan, Sub-threshold Design for Ultra Low-Power Systems. *Springer*, 2006.

- [29] C. Enz and E. A. Vittoz, "CMOS low-power analog circuit design," in *Proceeding of IEEE* International Symposium on Circuits and Systems (ISCAS), chapter 1.2, Tutorials, pp. 79–132, 1996.

## **2.1. Introduction**

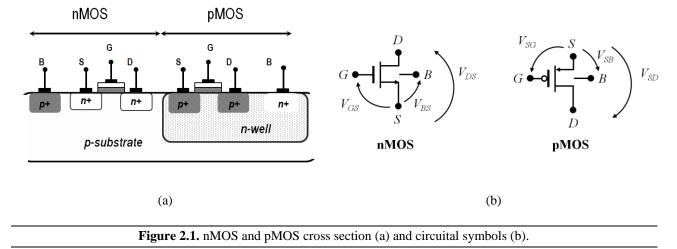

The Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET), is by far the most widespread component in the modern electronics [1]. The schematic and the cross section of the nMOS and pMOS transistor are reported in Figure 2.1(a) and 2.1(b) respectively. The four terminals (drain D, source S, body B and gate G) are used to change the operating regime of the transistor. The layer under the gate, also called channel, contains electrons in the case of the nMOSFET and holes in the cse of the pMOSFET. Thus an nMOS transistor has a p-type substrate while the pMOS transistor has an n-type substrate. The MOSFET is in able to implement the controlled switch which is ON (drop voltage equal to zero across drain and source) when the gate-source voltage is higher, in absolute value, than the threshold voltage and OFF (drain-source current equal to zero) when the gate-source voltage is lower than the threshold voltage. However the MOSFET operates in a more complex way than a simple switch. Since its introduction three regimes of operation have been identified for this component: the *cut-off regime*, the *triode regime* and the *saturation regime*. The operating regime in which the MOSFET works depends on the relationship between the gate-source ( $V_{GS}$ ) voltage and the threshold voltage  $V_{TH}$  of the device.

The operating regimes of the MOSFET as well as the models used to describe its behaviour have been revised during the years [2]-[7]. In particular the former cut-off regime has been revised discovering that the current flowing in this operating condition is not negligible, indeed the device shows an interesting exponential relationship which nowadays is widely exploited in all the low-power, low-voltage contexts [8]. This regime is nowaday knows as *weak inversion* or *subthreshold regime*.

In the following a brief overview on the different operating regimes of the MOSFET are reported with particular emphasis on the weak inversion regime of operation. The main considerations from the design point of view will be highlighted.

## 2.2. I-V MOSFET relationship

In this section the main relationships used to describe the behaviour of a MOSFET are reported. All the equations here reported refer to the nMOS transistor; nevertheless the equations for the pMOS can be simply derived by considering the absolute values of the voltages.

The most important parameter for defining the operating regime of the MOSFET is the threshold voltage  $V_{TH}$ . For a MOSFET the threshold voltage represents the gate-source voltage required to forms an inversion layer (channel) between the oxide and the substrate of the transistor. For an nMOSFET with long channel/width and uniform substrate doping concentration  $V_{TH}$  is defined as [4]:

$$V_{TH} = V_{TH,0} + \lambda_B \left( \sqrt{V_{SB} + \phi_S} - \sqrt{\phi_S} \right), \qquad (2.1)$$

where in (2.1)  $\phi_S$  is the surface potential,  $V_{SB}$  is the source-body voltage and  $V_{TH0}$  is the threshold voltage of a long channel device at zero substrate voltage.  $\lambda_B$  is the body coefficient equal to:

$$\lambda_B = \frac{t_{OX}}{\varepsilon_{OX}} \sqrt{2qN_A\varepsilon_{Si}} , \qquad (2.2)$$

with  $t_{OX}$  and  $C_{OX}$  oxide thickness and oxide permittivity respectively,  $\varepsilon_{Si}$  silicon permittivity, q elementary charge and  $N_A$  doping concentration. Depending on the relationship between the gatesource voltage and the threshold voltage, the MOSFET can operate in different regimes of operation.

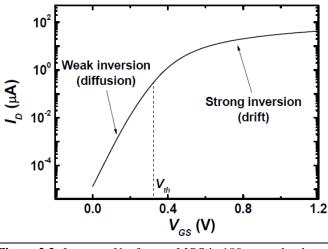

Figure 2.2.  $I_D$  versus  $V_{GS}$  for an nMOS in 180 nm technology.

Specifically, if

✓  $V_{GS} < V_{TH}$  the MOSFET is working in subthreshold regime or weak inversion regime;

- ✓  $V_{GS}$  >  $V_{TH}$  the MOSFET is working in above-threshold regime. In this case if

- $V_{DS} < V_{GS}$ - $V_{TH}$  then the MOSFET works in *triode regime*

- $V_{DS} > V_{GS}$ - $V_{TH}$  the MOSFET is in saturation regime.

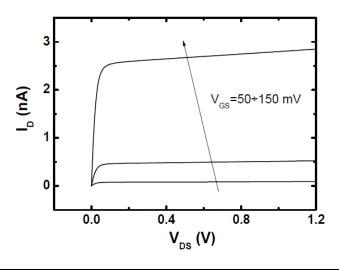

In Figure 2.2 the drain current ( $I_D$ ) against  $V_{GS}$  for an nMOS in 0.18 µm is reported while Figure 2.3 shows the  $I_D$ - $V_{DS}$  curve for an nMOS in the same technology.

There are different equations used to describe the  $I_D$  relationship in these different regimes of operation. Among them the models proposed in the BSIM [4]-[6] and in the EKV model [7] are considered nowadays as the industry standards. Despite the EKV model is more accurate in the description of the subthreshold operation, most of the industries release their design kits, commonly employed in SPICE simulators [8]-[9], using the BSIM model.

Figure 2.3.  $I_D$  versus  $V_{DS}$  for an nMOS in 180 nm technology.

In the equations (2.3)-(2.5) the most common expressions of the drain current for the subthreshold and above threshold conduction are reported. These equations represent the simplest version of the MOSFET model used in circuital simulations [10].

| Regime of<br>Operation | Drain Current                                                                                                                                  | Condition                                    |       |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------|

| Subthreshold           | $I_{DS} = \mu_N C_{OX} \frac{W}{L} V_T^2 \exp\left(\frac{V_{GS} - V_{TH}}{nV_T}\right) \left(1 - \exp\left(-\frac{V_{DS}}{V_T}\right)\right),$ | $V_{GS} < V_{TH}$                            | (2.3) |

| Triode                 | $I_{DS} = \frac{1}{2} \mu_N C_{OX} \frac{W}{L} [2(V_{GS} - V_{TH}) - V_{DS}] V_{DS},$                                                          | $V_{GS} > V_{TH}$ $V_{DS} < V_{GS} - V_{TH}$ | (2.4) |

| Saturation             | $I_{DS} = \frac{1}{2} \mu_N C_{OX} \frac{W}{L} [(V_{GS} - V_{TH})]^2 (1 + \lambda (V_{DS} - V_{DS,sat})).$                                     | $V_{GS} > V_{TH}$ $V_{DS} > V_{GS} - V_{TH}$ | (2.5) |

Despite the simplicity with respect to the more complex models these equations are in able to provide the main information about the effect of the bias voltages on the MOS transistor.

In the equations (2.3)-(2.5)  $\mu_N$  is the electron mobility,  $C_{OX}$  is the oxide capacitance per unit area transistor, W and L are the channel length and width respectively,  $V_T$  is the thermal voltage equal to kT/q (with k Boltzmann's constant, T absolute temperature and q elementary charge), n is the

subtreshold swing factor,  $V_{TH}$  is the threshold voltage,  $\lambda$  is the channel length modulation and  $V_{DS,sat}$  the saturation drain-source voltage [11].

Since this work is focused on low power, low voltage design, in the following the parameters used in the description of the weak inversion regime are considered more in detail.

The expression (2.3) shows that the current flowing in the MOSFET depends exponentially from the  $V_{GS}$  voltage in subthreshold regime. This means that the gate terminal has a very good control of the channel and consequently of drain current. Indeed, the gate transconductance  $g_m = \partial I_D / \partial V_{GS}$  in this regime is higher than in strong inversion regime as reported in the equations (2.6) and (2.7).

| Regime of Operation | Drain Current                                | _     |

|---------------------|----------------------------------------------|-------|

| $V_{GS} < V_{TH}$   | $g_m = \frac{I_D}{nV_T}$                     | (2.6) |

| $V_{GS} > V_{TH}$   | $g_m = \sqrt{2\mu_N C_{OX} \frac{W}{L} I_D}$ | (2.7) |

The parameter n, which is included in the expression of the drain current in subthreshold regime, represents a loss of coupling efficiency between the gate and channel caused by the body, which acts as a back gate. In weak inversion, n is related to the capacitive voltage division between the gate voltage and silicon surface potential resulting from the gate-oxide, depletion, and interface state capacitances [11]. It can be expressed as:

$$n \approx 1 + \frac{C_{DEP}}{C_{OX}},\tag{2.8}$$

where  $C_{DEP}$  is the depletion capacitance per unit area. This parameter is usually expressed in the subthreshold swing (SS):

$$SS \approx \ln(10)nV_T$$

, (2.9)

which defines the increment in  $V_{GS}$  necessary to achieve an 10 × increment in the drain current. Graphically it represents the slope of the curve  $I_D$ - $V_{GS}$  in weak inversion regime (linear region in Figure 2.2).

The expression of the subtreshold current reported in (2.3) shows that  $V_{DS}$  effects  $I_D$  only because of term (1- $exp(-V_{DS}/V_T)$ ). This contribution is negligible if  $V_{DS}>4V_T$  which is equal to about 104 mV at 25 °C. Thus, in such condition (saturation regime) the following equation can be used to describe the drain current in subtreshold regime:

$$I_{DS} \approx \mu_N C_{OX} \frac{W}{L} V_T^2 \exp\left(\frac{V_{GS} - V_{TH}}{nV_T}\right).$$

(2.10)

However  $V_{DS}$  influences the drain current also because of the Drain-Induced-Barrier-Lowering (DIBL) effect. From the design point of view this effect bring to a variation of the threshold voltage and consequently to a variation of the drain current. As reported in (2.1) also the body-source voltage can cause such a change. To model both effects, the following equation is commonly used [12]:

$$V_{TH} = V_{TH0} - \lambda_{DS} V_D - \lambda_B V_{BS}, \qquad (2.11)$$

where  $V_{TH0}$  is the zero-biased threshold voltage extracted at  $V_{DS}=V_{BS}=0$  while  $\lambda_D$  and  $\lambda_B$  represent the DIBL and body coefficient already defined in (2.2). The DIBL coefficient has an exponential relationship with the MOSFET channel length [13], thus long channel transistor can reduce this effect. In Figure 2.4 simulation results on  $\lambda_D$  obtained for an nMOS in 0.18 µm is reported. The SPICE simulations confirm the exponential relationship between  $\lambda_D$  and the channel length.

On the other hand the reduction of the body effect cannot be performed by simply adjusting the geometry of the transistor. The only solution to mitigate this effect consists in using a tripe well technology which allows performing the condition of  $V_{BS}$ =0 also for the stacked nMOS transistors. This results in a larger occupied area because of the additional masks [14].

**Figure 2.4.**  $\lambda_D$  (mV/V) against  $V_{DS}$  for an nMOS in 180 nm technology.

#### 2.2.1. Small signal behaviour

| parameter                                                      | sub-threshold                |         | above-threshold                                                             | !       |

|----------------------------------------------------------------|------------------------------|---------|-----------------------------------------------------------------------------|---------|

| $g_m = \frac{\partial I_D}{\partial V_{GS}}$                   | $\frac{I_D}{nV_T}$           | (2.12a) | $\sqrt{\frac{2\mu_{N}C_{OX}WI_{D}}{L}}$                                     | (2.12b) |

| $g_{mb} = \frac{\partial I_D}{\partial V_{BS}}$                | $\frac{\lambda_B I_D}{nV_T}$ | (2.13a) | $\frac{g_{_{M}}\lambda_{_{B}}}{2\sqrt{\left V_{_{SB}}\right +\phi_{_{S}}}}$ | (2.13b) |

| $r_d = \left[\frac{\partial I_D}{\partial V_{DS}}\right]^{-1}$ | $\frac{nV_T}{\lambda_D I_D}$ | (2.14a) | $\frac{1}{\lambda I_D}$                                                     | (2.14c) |

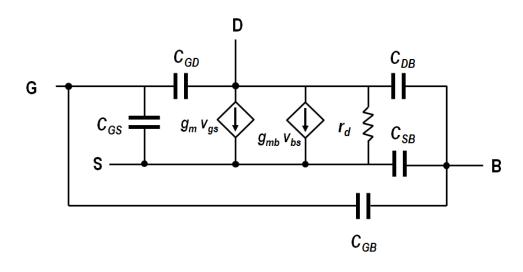

The MOSFET equivalent circuit valid both in the case of the above threshold regime and the weak inversion regime is reported in Figure 2.5. Despite the same model the small signal parameters are different for the two operating regime. The values of these parameters in above- and sub-threshold regime are reported in the equations (2.12a)-(2.14c). It is possible to note that the transconductance efficiency  $g_m/I_D$  is higher in weak inversion than in strong inversion. Moreover the  $g_m/I_D$  ration in subthreshold regime is independent from the geometry of the transistor except for the dependence of *n* from transistor's area. The intrinsic DC gain offered by the MOSFET is significantly higher in weak inversion regime ( $\propto 1/\lambda \sqrt{I_D}$ ).

Figure 2.5. MOSFET small-signal equivalent circuit.

| Capacitance     | Sub-threshold            | Triode                             | Saturation                         |

|-----------------|--------------------------|------------------------------------|------------------------------------|

| $C_{GB}$        | WLC <sub>OX</sub>        | Negligible                         | Negligible                         |

| $C_{GD}$        | $WL_DC_{OX}$             | $\frac{1}{2}WLC_{OX} + WL_DC_{OX}$ | $WL_DC_{OX}$                       |

| $C_{GS}$        | $WL_DC_{OX}$             | $\frac{1}{2}WLC_{OX} + WL_DC_{OX}$ | $\frac{2}{3}WLC_{OX}$              |

| $C_{GG}(total)$ | $WLC_{OX} + 2WL_DC_{OX}$ | $2WL_DC_{OX} + WLC_{OX}$           | $\frac{2}{3}WLC_{OX} + WL_DC_{OX}$ |

The small signal analysis allows also understanding the frequency behaviour of the MOSFET in the different operating regimes.

As reported in Table 2.I the values of the MOSFET capacitances are different in the different operating regimes [15]. The values reported in the table take into account also the parasitic capacitances due to the overlaps in the drain and source regions ( $L_D$  indicates the length of the overlap which is considered equal for the drain/source region) [15].

The frequency performances of the MOSFET can be investigated by considering the intrinsic bandwidth of the MOSFET, defined as the frequency where current gain from the gate input to the short circuit, drain output is equal to unity. It is defined as [11]:

$$f_{Ti} = \frac{g_m}{2\pi (C_{GS} + C_{GB})}.$$

(2.15)

Considering the (2.15) and substituting the values of  $C_{GS}$  and  $C_{GB}$  in weak inversion and strong inversion, the following expressions are obtained [11]:

$$\frac{\text{sub-threshold}}{f_{Ti} \approx \left(\frac{n}{n-1}\right) \frac{\mu_0 V_T}{\pi L^2} IC, \qquad (2.16a) \qquad f_{Ti} \approx \left(\frac{n}{n-1/3}\right) \frac{\mu_0 V_T}{\pi L^2} \sqrt{IC}, \qquad (2.16b)$$

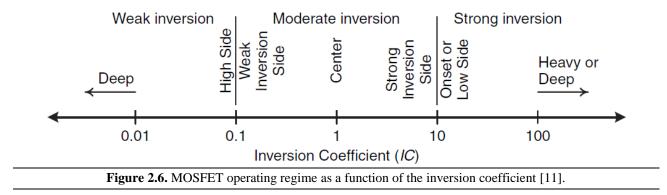

where in (2.16a) and (2.16b), the inversion coefficient (IC) is defined as [11]:

$$IC = \frac{I_D}{2\mu_0 n_0 C_{OX} V_T^2 \left(\frac{W}{L}\right)}.$$

(2.17)

In (2.16a), (2.16b) and (2.17)  $\mu_0$  and  $n_0$  represent the mobility and the subthreshold swing factor at the room temperature. The value of *IC* is in able to define the operating regime of the MOSFET depending on the magnitude of the drain current  $I_D$ . Figure 2.6 reports the relationship between *IC* and the operating regime. Since for the purpose of this work the concept of the *IC* is not essential is will not deeply investigated, however the MOSFET modeling based on the *IC* is becoming very popular also in the circuital community thanks to the diffusion of the EKV model [7], [11]. According to the definition of the *IC* parameter, from (2.16a) - (2.16b), the intrinsic bandwidth of the transistor is strongly reduced by increasing the channel length in both regime of operation.

The  $f_{Ti}$  increases in weak inversion at higher current and reach its maximum value near the moderate inversion regime. Due to the higher drain current, the frequency response of the MOSFET in weak inversion is reduced compared to the strong inversion regime.

#### 2.2.2. Temperature effect

Unlike the above threshold regime in which the current is mostly due to a drift mechanism, the subthreshold conduction is dominated by the diffusion mechanism.

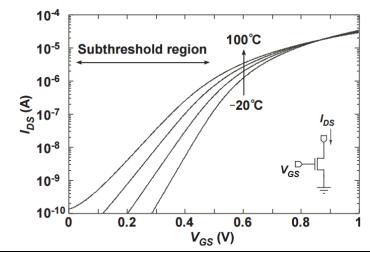

As a consequence the drain current depends on temperature more than in above threshold regime as shown in Figure 2.7. From the design point of view the main parameters which depend on temperature are the mobility, the thermal voltage, and the threshold voltage while a negligible influence of the temperature on the subthreshold swing factor is commonly assumed in the typical temperature range [11]. Equations (2.18)-(2.20) report the temperature dependence of these parameters [11].

| Parameter                    | Temperature Dependence                                                                   |        |

|------------------------------|------------------------------------------------------------------------------------------|--------|

| $V_T$                        | $V_T = 25.85mV \frac{T}{300K}$                                                           | (2.18) |

| $\mu_{\scriptscriptstyle N}$ | $\mu_{\scriptscriptstyle N}=\mu_{\scriptscriptstyle N}ig(T_0igg(rac{T}{T_0}igg)^{\!-m}$ | (2.19) |

| V <sub>TH</sub>              | $V_{TH} = V_{TH} \left( T_0 \right) - \kappa \left( T - T_0 \right)$                     | (2.20) |

In (2.19)  $\mu_N(T_0)$  represents the electron mobility at the room temperature  $T_0$ , while *m* is the mobility exponent which defines the relationship between the electron mobility and the temperature. Typically *m* is equal to about 1.2 - 2 for the nMOS. In (2.20)  $\kappa$  is the coefficient which defines the drops of the threshold voltage at higher temperatures. From (2.20) the threshold voltage decreases linearly by increasing the temperature.

From the previous equations it is possible to note that the temperature-dependent parameters are the same both in the case of subthreshold and above-threshold conduction. Nevertheless, since the subthreshold current depends exponentially on threshold voltage in subthreshold regime, the current becomes more sensitive on temperature in weak inversion than in strong inversion.

#### 2.2.3. Process stability

Working in subthreshold regime the designer has to take care, more than in above threshold design, of the problem related to the process variability. Due to the variations in the oxide thickness, doping concentration, Line Edge Roughness (LER) [16]-[17], the behaviour of the MOSFET can differ from the expected one. Because of this, the design should satisfy the expected requirements also in the worst case conditions of process variability. The latter concept is valid for any circuit independently from the operating regime. In subthreshold regime however this problem is emphasized since every single deviation from the nominal behaviour affects the threshold voltage which in turn affects exponentially the drain current. As a consequence a severe variation in the behaviour of the different components (delay, leakage current, stability, etc.) can be observed.

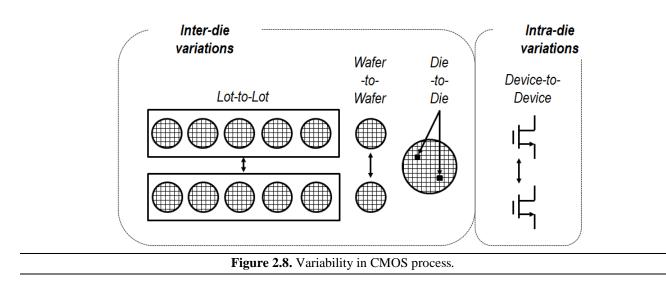

The variations of the process parameters can be classified into **inter-die** and **intra-die** variations. Inter-die or global variations refer to the lot-to-lot (L2L), wafer-to-wafer (W2W) and die-to-die (D2D) variations while the intra-die variations consider the variability at die level or within-die variations (WID) as shown in Figure 2.8 [17]. The intra-die variability can be classified in systematic and random. The systematic variations are usually strongly layout-dependent [17], while the random variations are completely unpredictable and result from the unpredictable process variability during fabrication. All the previous variations consider both the spatial as well as the temporal variations in the process which cause different dies and wafers to have different process parameters such as oxide thickness, dopant concentration, etc.

These variations are caused by of the differences in the manufacturing equipment during the process. If the parameters vary rapidly over distances smaller than the dimension of a die they result in WID variations while if the variations are more gradual over the wafer they will cause D2D variations. Considering the process steps, even more variability is present from wafer to wafer (W2W variations) and between different manufacturing runs (L2L variations).

The estimation of the effects of process variations is performed through SPICE simulations using intra-die and inter-die mismatch models and process corners models provided by the foundry as part of the SPICE models in the process design kit (PDK).

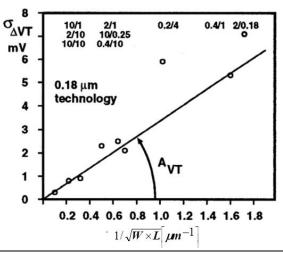

The effect of the random variations is defined using the Pelgrom's law [18]. According to Pelgrom, the following equation describes the standard deviation on threshold voltage between the two matched transistors on the same wafer:

$$\sigma(V_{TH}) = \frac{A_{VT}}{\sqrt{W \times L}},\tag{2.21}$$

where  $A_{VT}$  is a constant depending on the technology, while W and L are the effective channel width and length of the transistor respectively. In Figure 2.9 the standard deviation of the threshold voltage against the  $1/(W \times L)^{0.5}$  factor is reported for 0.18 µm CMOS process.

On the other hand to model the L2L variability the corner analysis is performed. The foundry provides information about the maximum variability in the process such as maximum/minimum oxide thickness, maximum/minimum value of the doping concentration, maximum/minimum value of the threshold voltage. In this case the variations are classified considering separately the parameters in the nMOS and pMOS transistors, thus five corners are specified: TT (Typical nMOS, Typical pMOS), SS (Slow nMOS, Slow pMOS), FF (Fast nMOS, Fast pMOS), SF (Slow nMOS, Fast pMOS) and FS (Fast nMOS, Slow pMOS).

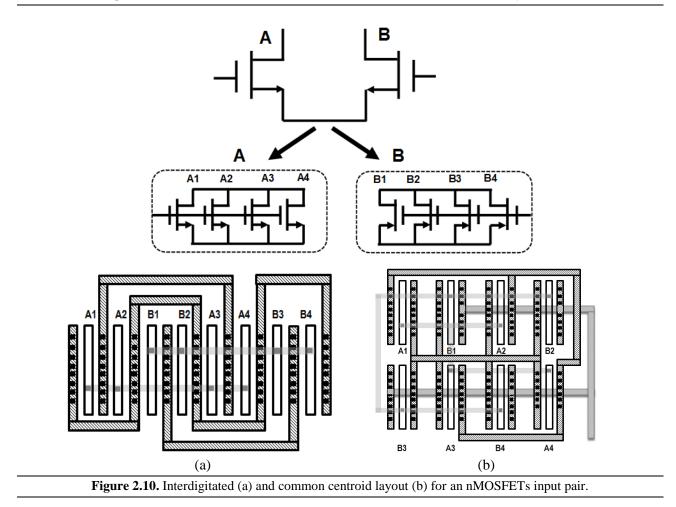

The problem of the process variability is particular important in structures in which a very good matching among different transistors is required such as input pair of operational amplifiers and current mirrors. Thus, to mitigate the effect of the mismatch, large area W/L transistors should be employed. Nevertheless it is worth noting that the equation (2.21) takes into account only for the random variations in CMOS process such as random dopant fluctuation but it does not take into account for systematic variations like temperature gradient or mechanical stress [19].

Usually the compensation for these effects is performed at layout level using interdigitated (Figure 2.10 (a)) or common centroid layout (Figure 2.10 (b)) [19]. Due to the layout rules required by process these solutions lead to a higher occupied area.

**Figure 2.9.** Standard deviation of  $V_{TH}$  as a function of transistor sizes in 0.18 µm CMOS.

# **Bibliography**

- [1] J. David Irwin. The Industrial Electronics Handbook, 2<sup>nd</sup> Edition, CRC Press, 2011.

- [2] C.T. Sah, "Evolution of the MOS transistor from conception to VLSI", in *Proceeding of IEEE*, vol. 76, no 10, Oct. 1988, pp. 1280-1326.

- [3] C.T. Sah, "A History of MOS Transistor Compact Modeling", in *Technical Proceeding of Workshop on Compact Modeling*, 1992, pp. 347-390.

- [4] W. Liu, X. Jin, J. Chen, M. Jeng, Z. Liu, Y. Cheng, K. Chen, M. Chan, K. Hui, J. Huang, R. Tu, P. Ko, and C. Hu, "BSIM3v3.2 MOSFET Model and Users' Manual". http://wwwdevice.eecs.berkeley.edu/~bsim3.

- [5] W. Liu. Mosfet Models for Spice Simulation: Including BSIM3v3 and BSIM4, John Wiley & Sons, 2001.

- [6] W. Liu, X. Jin, J. Chen, M. Jeng, Z. Liu, Y. Cheng, K. Chen, M. Chan, K. Hui, J. Huang, R. Tu, P. Ko and C. Hu. **BSIM4.6.4 MOSFET Model and Users' Manual**.

- [7] C. C. Enz, F. Krummenacher, E.A. Vittoz, "An Analytical MOS Transistor Model Valid in All Regions of Operation and Dedicated to Low-Voltage and Low-Current Applications", *Analog Integrated Circuits and Signal Processing Journal on Low-Voltage and Low-Power Design*, 8. pp. 83–114, July 1995.

- [8] L. W Nagel and D. O. Pederson, SPICE (Simulation Program with Integrated Circuit Emphasis), *Memorandum No. ERL-M382*, University of California, Berkeley, Apr. 1973.

- [9] http://bwrcs.eecs.berkeley.edu/Classes/IcBook/SPICE/.

- [10] http://people.rit.edu/lffeee/SPICE.pdf.

- [11] D. Binkley, Tradeoffs and Optimization in Analog CMOS Design. Wiley, 2008.

- [12] M. Alioto, "Understanding DC behaviour of subthreshold CMOS logic through closed-form analysis," IEEE Transaction on Circuits and Systems I, Regular Papers, vol. 57, no. 7, pp. 1597–1607, Jul. 2010.

- [13] Z.H. Liu, C. Hu, J.H. Huang, T.Y. Chan, M.C. Jeng, P.K. Ko, and Y.C. Cheng, "Threshold Voltage Model For Deep-Submicrometer MOSFETs," *IEEE Transaction on Electron Devices*, vol. 40, pp. 86-95, Jan., 1993.

- [14] S. H. Voldman, Latchup, chapter 5, Wiley, 2007.

- [15] D. K. Schroder, Semiconductor Material and Device Characterization, 3rd Edition, Wiley, 2006.

- [16] A. Asenov, S. Kaya, J.H. Davies, "Intrinsic threshold voltage fluctuations in decanano MOSFETs due to local oxide thickness variations," *IEEE Transaction on Electron Devices*, vol. 49, no 112, pp. 112-119, 2002.

- [17] J. Kawa, Design for Manufacturability and Yield for Nano-Scale CMOS. Springer, 2007.

- [18] M. Pelgrom, A. Duinmaijer, and A. Welbers, "Matching properties of MOS transistors," *IEEE Journal of Solid-State Circuits*, vol. 24, no. 1, pp. 1433-1439, Oct. 1989.

- [19] A. Hastings, The Art of Analog Layout. Englewood Cliffs. NJ: Prentice-Hall, 2001.

# **3. Low-voltage, low-power subthreshold voltage references**

# **3.1. Introduction**

As a consequence of the explosion of applications that require low power consumption, subthreshold circuits have gained much interest in the design community. RFID, implantable medical devices, micro-sensor networks, microcontroller unit (MCU) and digital signal processing (DSP) of portable devices are typical examples of applications that benefit from low energy operation [1].

In these devices the requirement for small size and weight imposes the use of small batteries which provide a small amount of energy for the different building blocks. At the same time, as explained in Chapter 1, many portable applications impose also the requirement of long lifetime such as in the case of passive RFIDs and implantable medical devices. Therefore the energy and size requirements can be simultaneously guaranteed only by using circuits that operate at low supply voltage and with low power consumption.

In such a context, the design of the voltage references becomes particularly challenging. Voltage references are used in all analog, digital and mixed-signal systems to generate a constant output voltage irrespective of temperature, process and supply voltage variations. There are several approaches to design a voltage reference. The most common solution consists in the bandgap voltage reference (BGR) implemented in bipolar technology [2]. Nevertheless, in order to ensure a major compatibility with the rest of the system, several works have implemented the operating principle of the classical BGR in CMOS process by exploiting the parasitic vertical BJTs [3]-[7] or BiCMOS technology [8]. However, all these solutions exhibit power consumption and a minimum supply voltage that are both too large for the typical low-power applications.

Alternative approaches employ MOSFETs working in strong inversion regime [9]-[10], part in strong inversion and subthreshold regime [11]-[14] or all in subthreshold regime [15]-[17]. Some of them use MOSFETs with same threshold voltage [10]-[11], [13]-[16] while in other cases MOSFETs with two different threshold voltages are employed [9], [12], [17].

Among the different approaches, subthreshold design represents the most promising solution for extreme low-power, low-voltage applications. Subthreshold operation results in a very low minimum supply voltage and in nW power consumption [16]-[17].

However, despite the significant advantages in terms of minimum supply voltage and power consumption, subthreshold operation poses several design issues. Of the utmost importance is the high process sensitivity due to the exponential relationship between the drain current and the threshold voltage [18], which is the most important process-dependent parameter.

In the following sections of this chapter the main performance specifications for a voltage reference and a brief overview on the most significant solutions are reported. Finally two new very lowvoltage, low-power solutions are introduced. The main design issues are addressed and the measurement results are reported and compared with the other solutions proposed so far.

#### **3.2.** Voltage reference performance specifications

From the operating point of view, a voltage reference is a three terminals device. It receives two inputs, the positive  $(V_{DD}+)$  and the negative  $(V_{DD}-)$  supply voltage, and generates a voltage as output  $(V_{OUT})$ . Since the main aim in the design of a voltage reference consists in generating a very stable output voltage, the main design specifications have the purpose to provide information about the stability of the generated voltage across different operating conditions like supply voltage  $V_{DD}$ , temperature, noise and process variations. Aside the above requirements, a voltage reference, especially if designed for the above mentioned applications, should satisfy the typical VLSI metrics such as the lowest possible power consumption and the minimum occupied area.

#### **3.2.1.** Line sensitivity

The line sensitivity (LS) of a voltage reference measures the stability of the output voltage against supply voltage variation. It is defined as

$$LS(\%) = 100 \times \frac{\Delta V_{REF}}{V_{REF} \times \Delta V_{DD}} \left[\frac{\%}{V}\right].$$

(3.1)

In (3.1)  $\Delta V_{REF}$  is the variation in Volts of the voltage reference (= $V_{REF,max}$ - $V_{REF,min}$ ) over the supply voltage range  $\Delta V_{DD} = V_{DD,min}$ - $V_{DD,max}$ , with  $V_{DD,min}$  and  $V_{DD,max}$  minimum and maximum operating supply voltage respectively.  $V_{REF}$  is the nominal value of the reference voltage. Usually  $V_{REF}$  is defined as the voltage at the room temperature for the minimum supply voltage. Thus, for the maximum stability with respect to  $V_{DD}$  variations, the LS should be as low as possible.

#### **3.2.2. Temperature coefficient**

The temperature coefficient (TC) measures the stability of the reference voltage against temperature variations. It is defined as:

$$TC = 10^{6} \times \frac{\Delta V_{REF}}{V_{REF} \times \Delta T} \left[ \frac{ppm}{^{\circ}C} \right].$$

(3.2)

In (3.2)  $\Delta V_{REF}$  is defined as the difference between the maximum and minimum voltage reference over the operating range of temperature  $\Delta T = T_{MAX} - T_{MIN}$ . In analogy with the LS also here  $V_{REF}$  is defined as the nominal output voltage evaluated at the room temperature for the minimum operating voltage. For the best stability the TC has to be as low as possible.

#### **3.2.3.** Power-Supply-Rejection-Rate (PSRR)

The power supply rejection rate (*PSRR*) is a measure of the capability of a voltage reference to reject the noise coming from the supply voltage. It is evaluated as

$$PSRR = 20\log_{10}\left(\frac{v_{out}}{v_{dd}}\right)[dB], \qquad (3.3)$$

where  $v_{out}/v_{dd}$  is the small signal ratio between the reference voltage and the supply voltage. The *PSRR* can be evaluated at different frequencies and considering the noise coming from  $V_{DD}$ + (*PSRR*+) and  $V_{DD}$ - (*PSRR*-).

#### **3.2.4.** Process stability

One of the most important requirements for a voltage reference is the stability against process variations. Ideally, the same voltage reference should provide the same value if fabricated N times across different wafers or on the same wafer. To evaluate the process stability it is necessary to evaluate the *coefficient of dispersion* ( $\sigma/\mu$ ) of N voltage references produced in the same wafer and/or different wafers. It is defined as

$$\frac{\sigma}{\mu} = 100 \times \frac{\sqrt{\frac{\sum_{i=1}^{N-1} (V_{REF}(i) - \mu)^2}{N-1}}}{\frac{1}{N} \sum_{i=1}^{N-1} V_{REF}(i)} [\%], \qquad (3.4)$$

where  $\mu$  is the mean value while  $\sigma$  is the standard deviation of the *N* samples. It is clear that the minimum value of  $\sigma/\mu$  is necessary for the maximum process stability.

## **3.3. Voltage references**

The very first voltage reference circuit, **the bandgap voltage reference (BGR)**, was proposed by Widlar [2]. The basic concept behind the idea of the BGR is to perform compensation between a proportional-to-absolute temperature (PTAT) voltage and complementary-to-absolute temperature (CTAT) Voltage.

For the generation of the CTAT voltage the base-to-emitter ( $V_{BE}$ ) voltage of a bipolar transistor or the forward voltage of a *pn* junction was exploited. Considering the case of a BJT, the collector current  $I_C$  can be expressed as:

$$I_C = I_S \exp\left(\frac{V_{BE}}{V_T}\right),\tag{3.5}$$

where  $I_s$  is the saturation current equal to  $I_s=\mu kTn_i^2$  with  $\mu$  minor carrier mobility, k Boltzmann's constant, T absolute temperature in Kelvin and  $n_i$  the intrinsic minority carrier concentration. Introducing in (3.5) the temperature dependence of the mobility and carrier concentration, the following expression can be obtained [19]:

$$I_s = bT^{4+m} \exp\left(-\frac{E_g}{kT}\right). \tag{3.6}$$

In (3.6) b is a proportional factor, m is the temperature coefficient of the mobility and  $E_g$  the energy gap of the silicon equal to about 1.12 V. Considering that  $V_{BE}=V_T ln(I_C/I_S)$ , the TC of such a voltage is equal to:

$$TC(V_{BE}) = \frac{\partial V_{BE}}{\partial T} = \frac{\partial V_T}{\partial T} \ln\left(\frac{I_C}{I_S}\right) - \frac{V_T}{I_S} \frac{\partial I_S}{\partial T} = \frac{V_{BE} - (4+m)V_T - E_g/q}{T}.$$

(3.7)

From (3.7) the TC of the  $V_{BE}$  voltage is a function of the magnitude of the same voltage. Thus, for a given value of  $V_{BE}$ , its TC can be evaluated. However since the TC is always lower than 0,  $V_{BE}$  is a CTAT voltage.

Regarding the generation of the PTAT voltage the difference between two  $V_{BE}$  voltages can be exploited [19]. In particular, if two different currents are injected into two BJTs with equal geometry, the difference between the two  $V_{BE}$  is a PTAT voltage. This can be demonstrated by simply considering the (3.5) and assuming in BJT1 a current  $I_C=nI$  and in BJT2 a current  $I_C=I$ . In this case the difference between the two  $V_{BE}$  is equal to:

$$\Delta V_{BE} = V_{BE,1} - V_{BE,2} = V_T \ln(n).$$

(3.8)

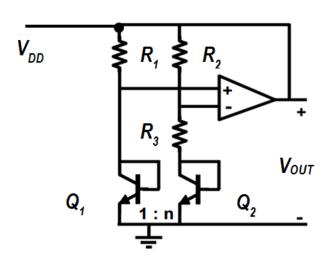

Having a PTAT and a CTAT voltage, a temperature compensated voltage can be obtained. A possible circuit which can perform such compensation is reported in Figure 3.1. The output voltage  $V_{OUT}$  is equal to:

$$V_{OUT} = V_{BE2} + V_T \left( 1 + \frac{R_2}{R_3} \right) \ln(n).$$

(3.9)

Figure 3.1. Bandgap voltage reference (BGR) [19].

Thus, for a zero TC voltage reference, the term  $R_2/R_3$  should be properly chosen. Since at room temperature  $\partial V_{BF}/\partial T$ =-1.5 mV/K, and  $\partial V_T/\partial T$ =0.0087 mV/K, a possible solution to achieve temperature compensation consists in imposing

$$\left(1+\frac{R_2}{R_3}\right)\ln(n) = \frac{0.087}{1.5} = 17.2,$$

(3.10)

which leads to a ratio  $R_2/R_3=4$ .

The classical implementation of the BGR is in able to generate an output voltage equal to about 1.25 V [2]-[19], quite close to the bandgap energy of the silicon. As a consequence the classical solution of the BGR does not allow obtaining a solution capable of operating at  $V_{DD}$  lower than 1.25 V. Another important problem of the classical BGR consists in the compatibility of such a component with the rest of the CMOS system.

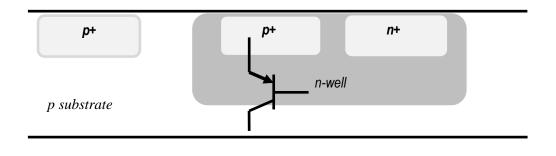

As a consequence different solutions have been proposed to implement such a component also in CMOS process by exploiting the vertical parasitic BJT available in the standard CMOS process (see Figure 3.2) or by using a BiCMOS process.

Figure 3.2. Parasitic BJT in the standard CMOS process.

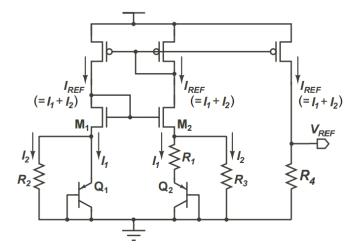

A sub-1 V BRG voltage reference completely compatible with the standard CMOS process was proposed by Bamba [5]. The schematic of the voltage reference is reported in Figure 3.3.

Figure 3.3. Sub-1V voltage reference proposed in [5].

In this solution the operating currents are equal to

$$I_{1} = \frac{V_{BE2} - V_{BE1}}{R_{1}} = \frac{V_{T} \ln(K_{2} / K_{1})}{R_{1}},$$

$$I_{2} = \frac{V_{BE1}}{R_{2}},$$

(3.11)

where  $K_1$  and  $K_2$  indicate the geometry of the BJT Q1 and Q2 respectively. The current  $I_{REF}=I_1+I_2$  is injected through the resistor  $R_4$ , generating the output voltage  $V_{REF}$ :

$$V_{REF} = \frac{R_4}{R_2} V_{BE1} + \frac{R_4}{R_1} V_T \ln(K_2 / K_1), \qquad (3.12)$$

thus imposing  $\partial V_{REF}/\partial T=0$  the value of  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$ ,  $K_1$  and  $K_2$  which allows the temperature compensation can be obtained. The solution proposed in [5] operates at  $V_{DD}=0.84$  V generating a reference voltage of about 0.5 V. The information on power consumption is not reported. An alternative sub-1V BGR in BiCMOS technology is proposed in [8]. The schematic of the solution is reported in Figure 3.4.

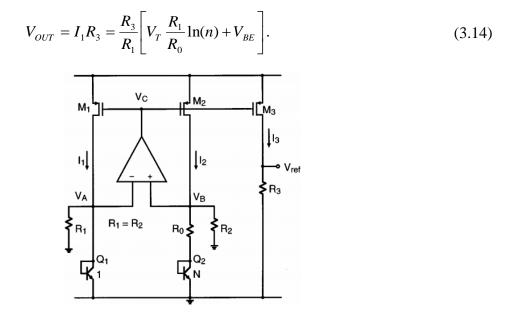

In this solution the operational amplifier forces the voltages  $V_A$  and  $V_B$  to be equal. As a consequence the current flowing in the two nominally equal resistors  $R_1$  and  $R_2$  is equal and proportional to  $V_{BE}$ . Thus, the current flowing in M<sub>1</sub>, M<sub>2</sub> and M<sub>3</sub> is equal to:

$$I_1 = \frac{V_{BE}}{R_1} + \frac{V_T \ln(n)}{R_0}.$$

(3.13)

Since the output voltage is coincident with the voltage across  $R_3$ , it can be expressed as:

Figure 3.4. Voltage reference proposed in [8].

From (3.14) the temperature compensation of  $V_{OUT}$  is achieved by choosing the right value of *n* and  $R_I/R_0$ . Specifically from (3.14), to obtain TC=0, the following condition holds [8]:

$$\frac{R_1}{R_0}\ln(n) = 22. \tag{3.15}$$

The circuit proposed in [8] starts to work from 1 V, generating a reference voltage of about 0.5 V. The power consumption is 92  $\mu$ W.

#### 3.3.1. Low-voltage, low-power voltage references

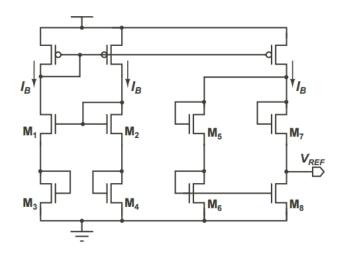

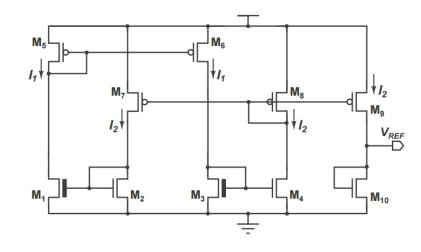

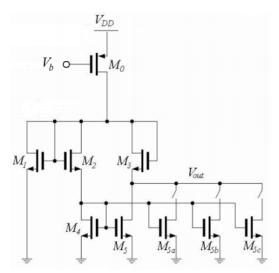

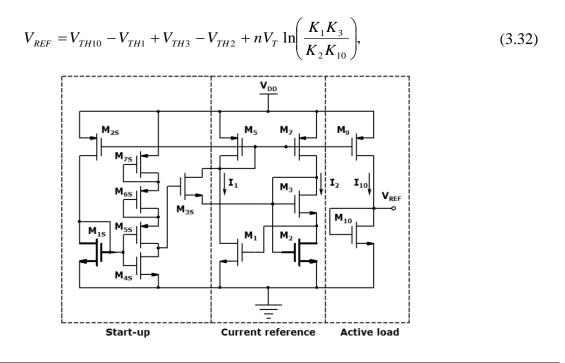

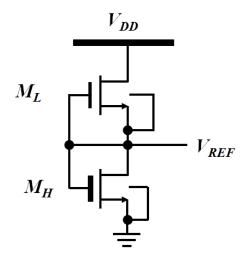

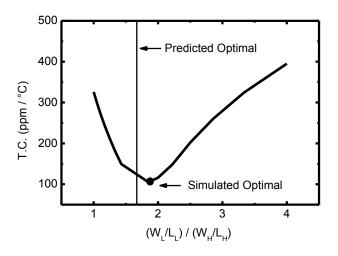

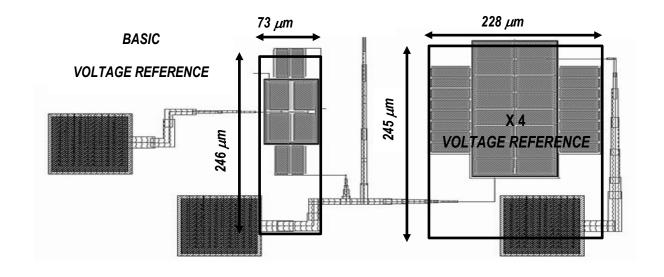

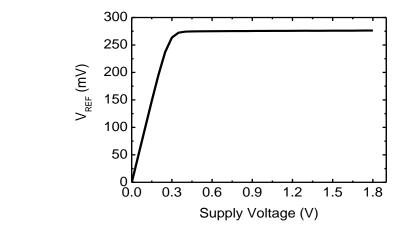

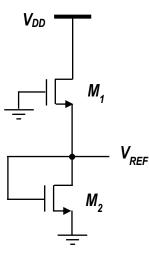

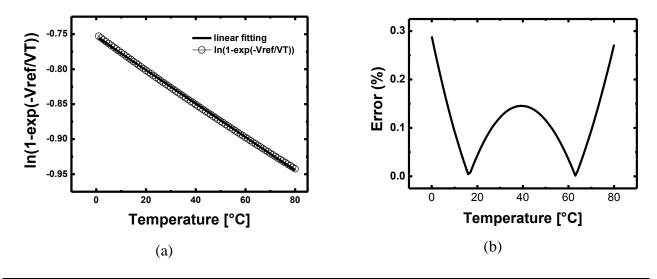

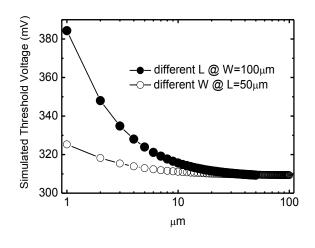

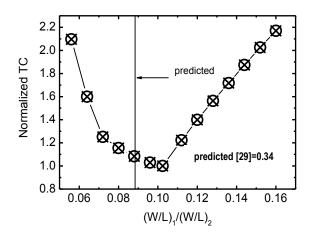

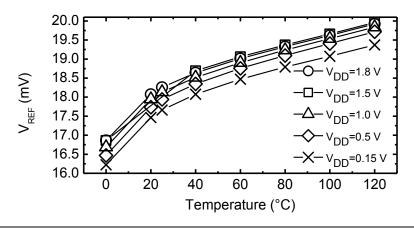

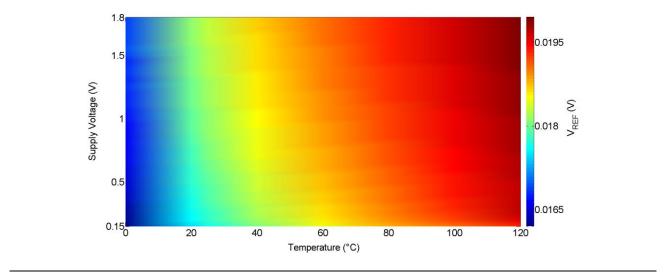

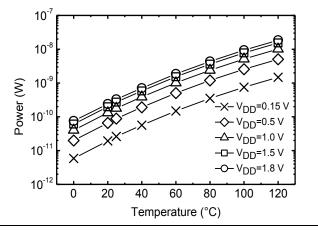

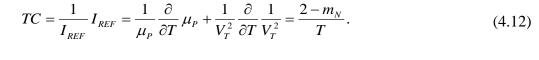

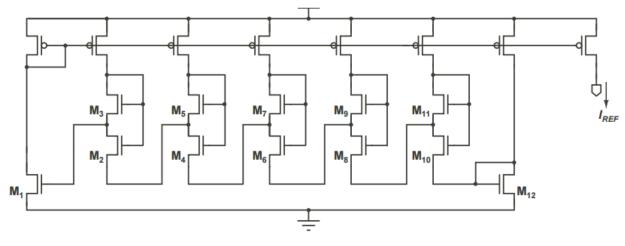

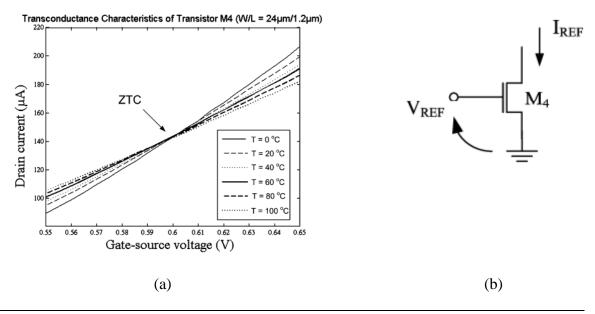

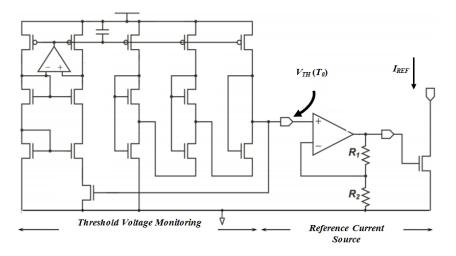

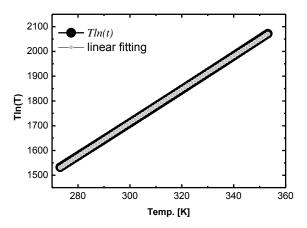

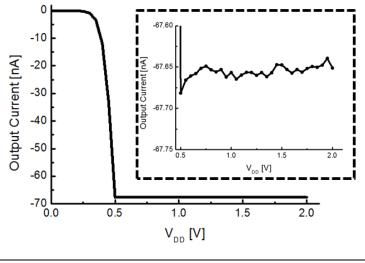

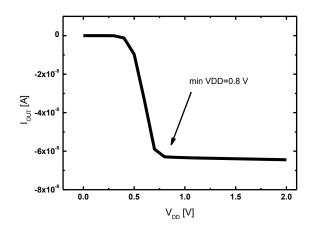

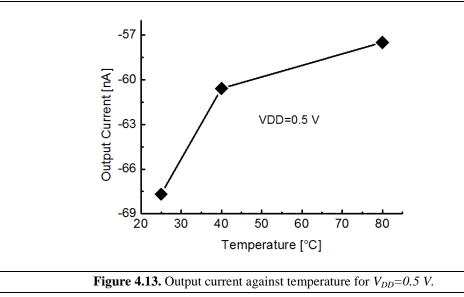

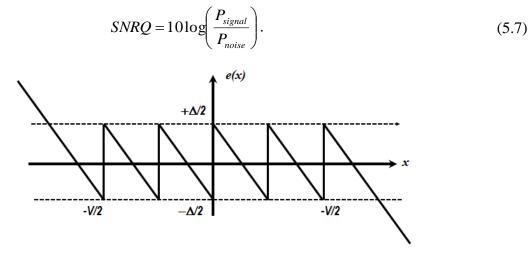

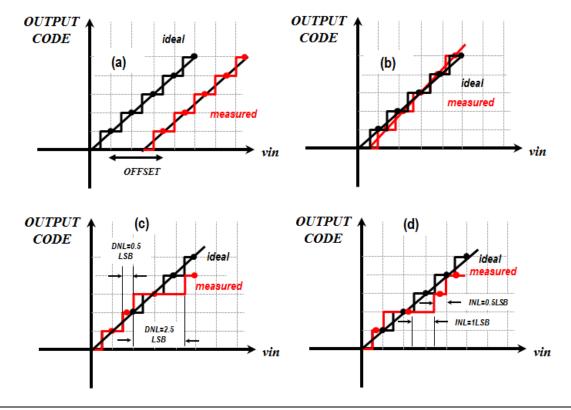

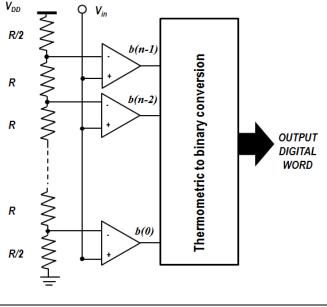

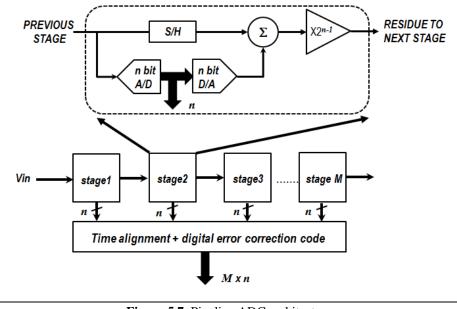

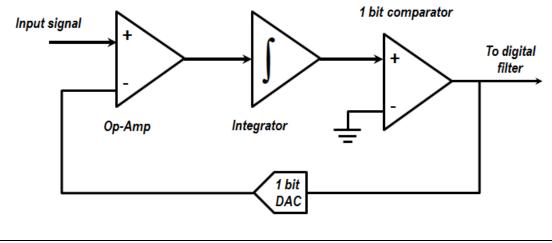

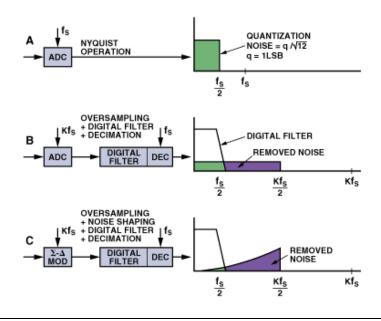

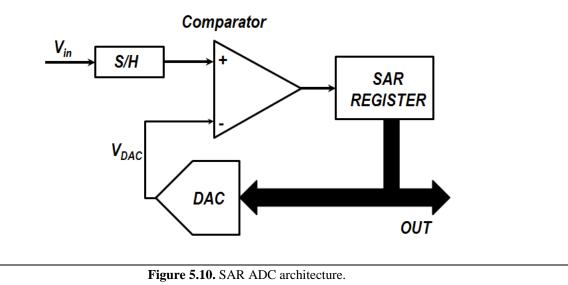

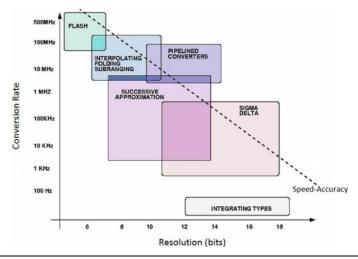

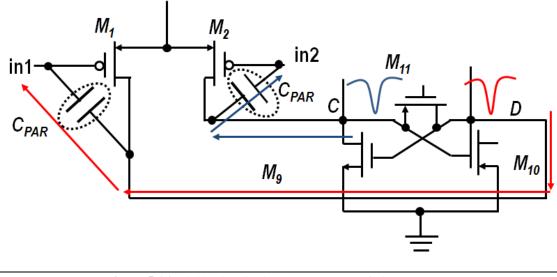

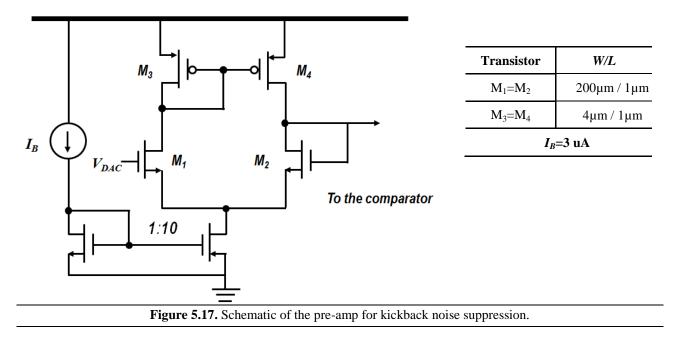

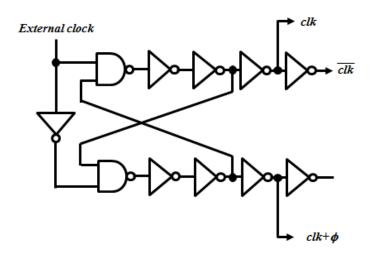

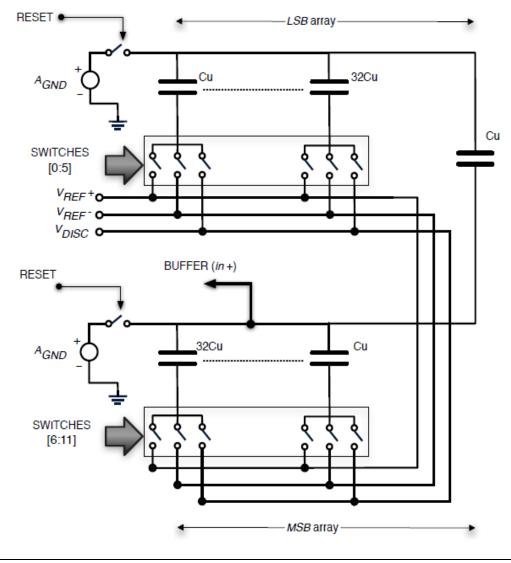

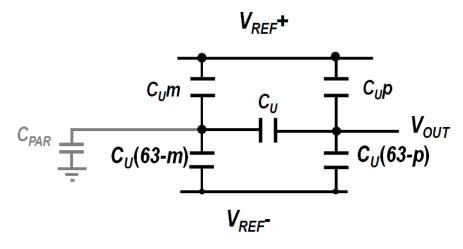

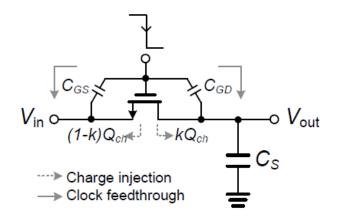

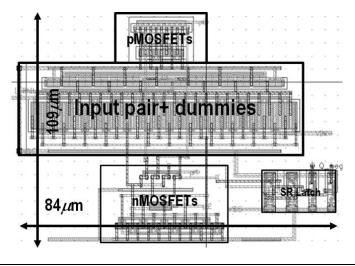

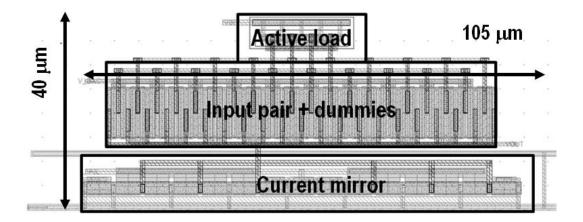

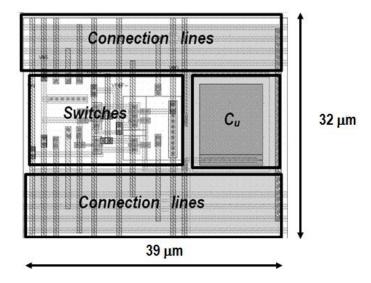

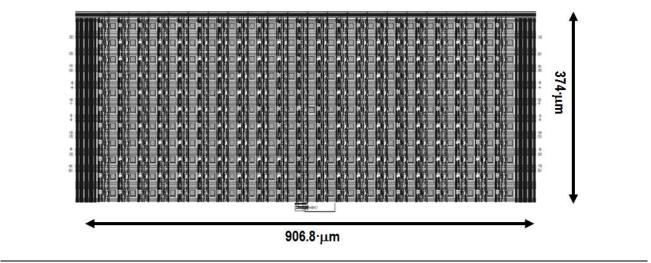

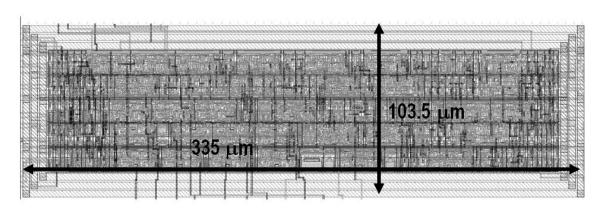

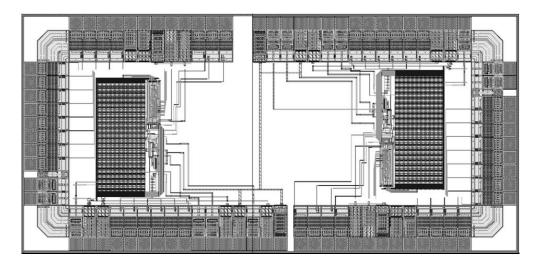

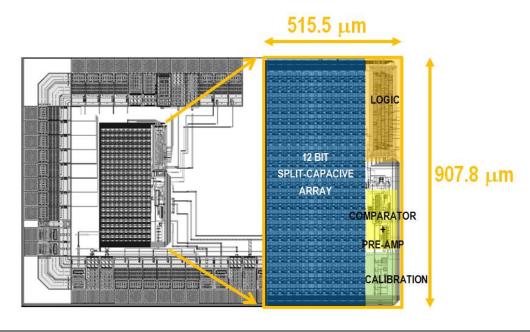

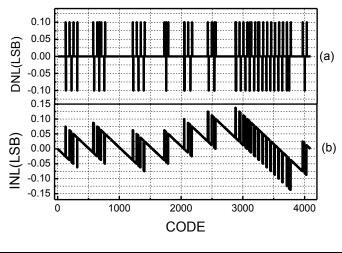

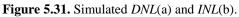

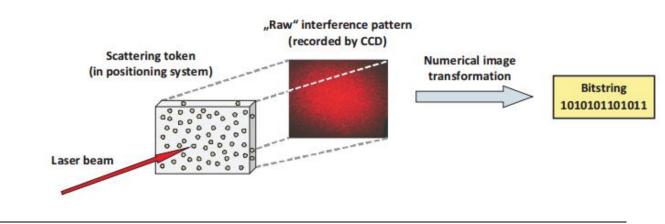

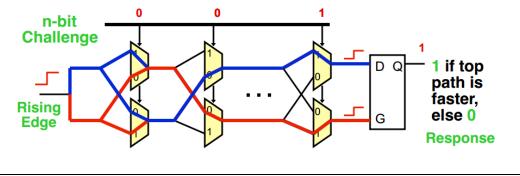

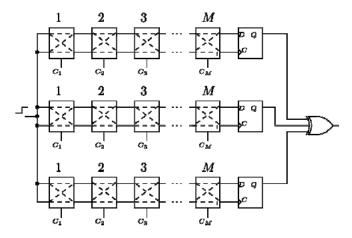

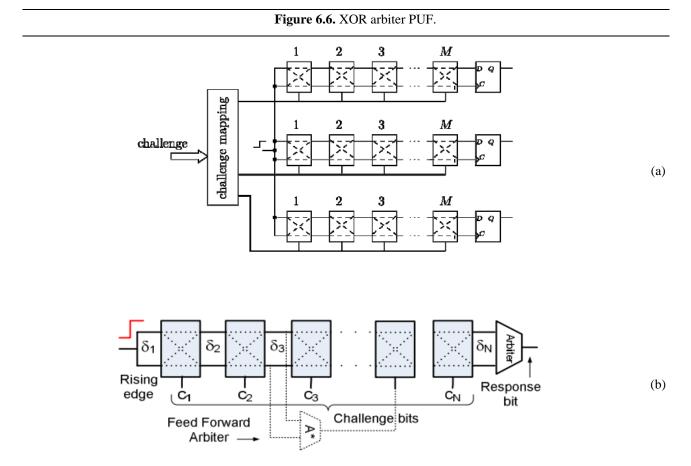

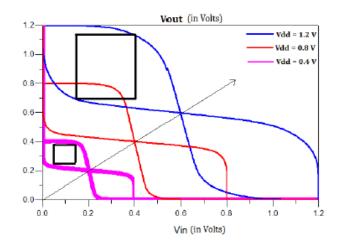

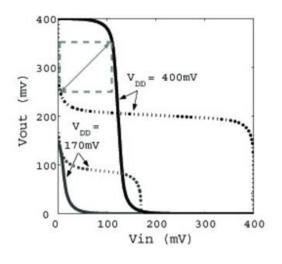

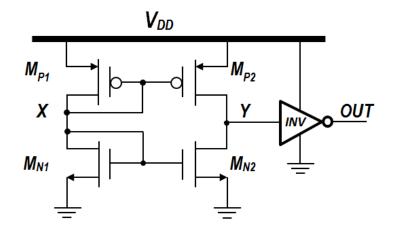

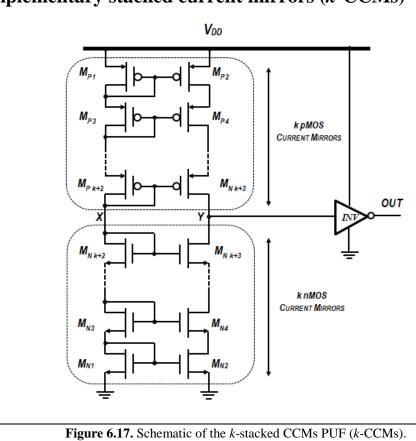

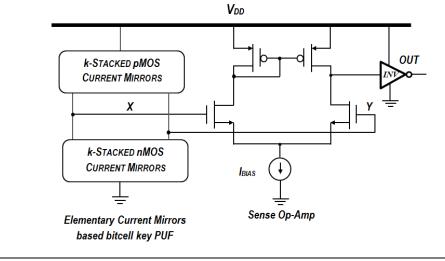

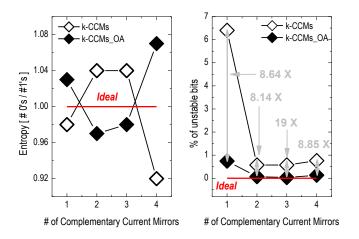

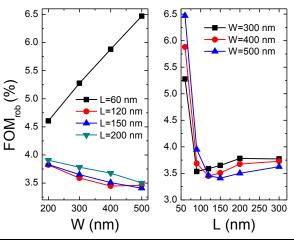

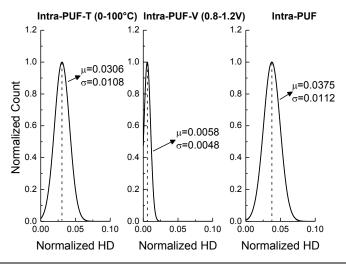

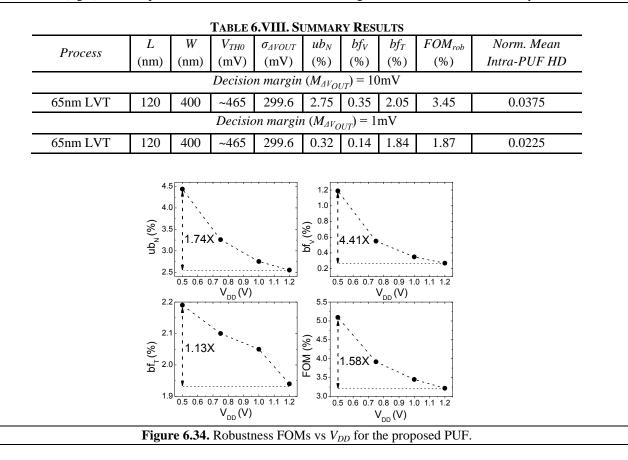

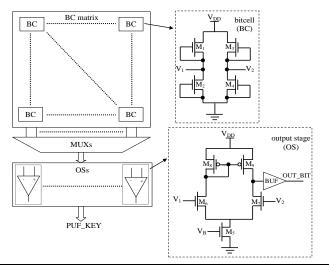

Despite the previous solutions are in able to ensure the sub-1V operation and the compatibility with the CMOS process, they result in high power consumption, widely over 1  $\mu$ W. As a consequence several solutions have tried to obtain low voltage operation and low power consumption at the same time. An improvement in terms of power consumption can be obtained by using fully-CMOS solutions instead of Bi-CMOS solutions.