#### UNIVERSITA' DELLA CALABRIA

Dipartimento di Ingegneria Informatica, Modellistica, Elettronica e Sistemistica (DIMES)

Scuola di Dottorato

Archimede

Indirizzo

Scienze, Comunicazione e Tecnologie

CICLO

XXVIII

#### TITOLO TESI

Low Voltage Digital Design exploiting dynamic body biasing techniques

Settore Scientifico Disciplinare ING-INF/01

Direttore: Firma

Prof. Pietro Pantano ieto Into

Supervisore: Prof. Marco Lanuzza Firma

Dottorando: Ramard Taco Firma

| Contents |

|----------|

|----------|

| A  | bstract                                                                    | 5       |  |  |  |  |  |

|----|----------------------------------------------------------------------------|---------|--|--|--|--|--|

| So | Sommario 9                                                                 |         |  |  |  |  |  |

| 1  | Introduction & Background                                                  | 14      |  |  |  |  |  |

|    | 1.1 Toward High Speed and Energy - efficient Designs                       | 14      |  |  |  |  |  |

|    | 1.2 Ultra-low Voltage (ULV) digital design: Characteristics and Issue      | es18    |  |  |  |  |  |

|    | 1.3 Minimum Energy per Operation                                           | 22      |  |  |  |  |  |

|    | 1.4 Body Biasing as an efficient knob in ULV operation                     | 27      |  |  |  |  |  |

|    | 1.5 Logic family exploiting Dynamic Body Biasing in ULV                    | 30      |  |  |  |  |  |

|    | 1.6 Purpose of this work                                                   | 33      |  |  |  |  |  |

| 2  | Analytical Modeling for Dynamic Gate – Level Body Biased Logic<br>Circuits | e<br>35 |  |  |  |  |  |

|    | 2.1 GLBB Operating Principle                                               | 36      |  |  |  |  |  |

|    | 2.2 Analytical Model                                                       | 39      |  |  |  |  |  |

|    | 2.3 Design Criteria and Analysis Validations                               | 50      |  |  |  |  |  |

|    | 2.4 Logic Gates with Stacked Transistors                                   | 57      |  |  |  |  |  |

|    | 2.5 Final Remarks on Design Criteria                                       | 69      |  |  |  |  |  |

| 3  | Dynamic Gate – Level Body Biasing Technique in Bulk<br>technologies        | 70      |  |  |  |  |  |

|    | 3.1 Physical constraints for gate-level body biasing technique             | 71      |  |  |  |  |  |

|    | 3.2 Final Remarks of Gate – Level Body Biasing in bulk technology.         | 83      |  |  |  |  |  |

| 4  | Dynamic Gate – Level Body Biasing Technique in UTBB F technologies     | D – SOI<br>85 |

|----|------------------------------------------------------------------------|---------------|

|    | 4.1 UTBB FD – SOI Technology Overview                                  | 86            |

|    | 4.2 Design Optimization for Gate-level Body Biasing                    |               |

|    | 4.3 Basic Gates: Design and Operating Characteristics                  | 93            |

|    | 4.4 Final Remarks of Gate-level Body Biasing in UTBB FD-S              | OI96          |

| 5  | Case studies: Application of the GLBB Technique to Arithmetic circuits | metic<br>98   |

|    | 5.1 Mirror Full Adder                                                  | 98            |

|    | 5.2 Ripple Carry Adder                                                 | 102           |

|    | 5.3 Baugh Wooley Multiplier                                            | 107           |

|    | 5.4 Final Remarks of Gate-level Body Biasing Technique to A Circuits   |               |

| 6  | Conclusions                                                            | 113           |

| Bi | ibliography                                                            | 115           |

| A  | cknowledgments                                                         | 127           |

| Li | ist of Publications                                                    | 128           |

## Abstract

Power supply voltage (VDD) scaling below the transistor threshold voltage (VTH) is one of the most effective approaches to achieve low energy consumption at the expense of large performance degradation and a much higher sensitivity to process variations and temperature fluctuations. While acceptable for niche markets, the delay and the robustness issues of conventional subthreshold CMOS circuits can be very limitative for a broader set of applications. In order to increase speed and robustness against process and temperature variations while maintaining high levels of energy efficiency, the forward body biasing (FBB) technique can be adopted.

The FBB technique can be applied (also dynamically) at different levels of granularity ranging from the macro-block level to the transistor level. The key rationale for applying forward body biasing at the macro-block level is to amortize the area and the body control signal routing of a finer grained implementation. However, there is a cost to pay: when threshold voltage is reduced at the block level to compensate for variations and/or to provide a temporary speed boost, leakage power is increased for all the gates in the block, while speed-up would be needed only on timing critical gates. Better energy-delay tradeoffs can be obtained by reducing the body-bias control granularity.

A feasible way to control body biasing at the transistor level is provided by the dynamic threshold voltage (DTMOS) logic. DTMOS logic uses transistors whose gates are tied to their substrates. As the substrate voltage varies with the gate voltage, the threshold voltage of the device is dynamically changed. In the ON-state, the device threshold voltage drops, thus providing a much higher ON current with respect to a standard MOSFET configuration. On the other hand, the behavior of a DTMOS transistor in the OFF-state is similar to that of a regular MOSFET. However, the DTMOS configuration implies input capacitances significantly larger than that of a standard CMOS static gate. Additionally, DTMOS logic incurs in higher energy consumption due to unnecessary charge/discharge of the substrate for input signals that doesn't produce a change in the output voltage of the gate.

In this thesis a gate-level dynamic body biasing technique to overcome the energy limits of DTMOS logic gates, while also improving the gate switching speed has been developed. Logic gates, designed exploiting dynamic body biasing technique exhibit input capacitances equal to those of the standard CMOS configuration. Moreover, when input signals switch without changing the logic gate status the body capacitances are not charged/discharged as occurs in DTMOS logic gates, thus enabling considerable energy saving.

Initially the gate level body biasing technique was modeled and analytically justified. Initially the inverter was adopted as reference circuit to develop the main design guidelines for the body biasing generator and the logic section of the gate. As an extension, logic gates with stacked transistors, (i.e. NAND2, NOR2) was also considered obtaining a good agreement between the predicted and the simulated results.

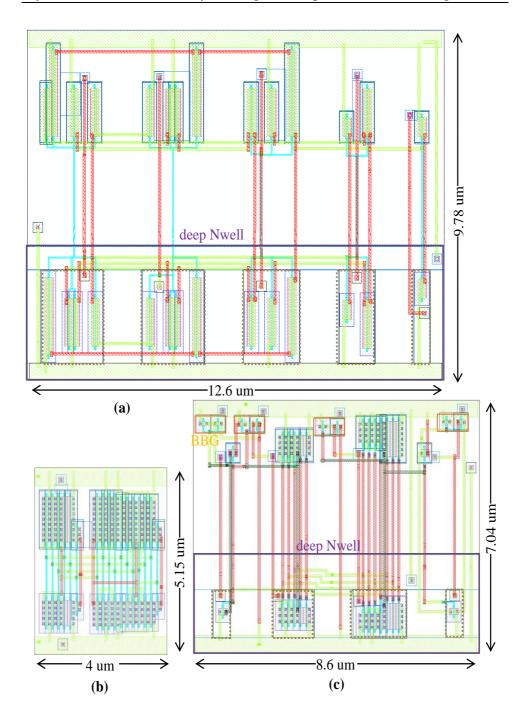

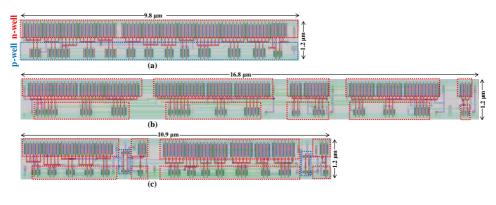

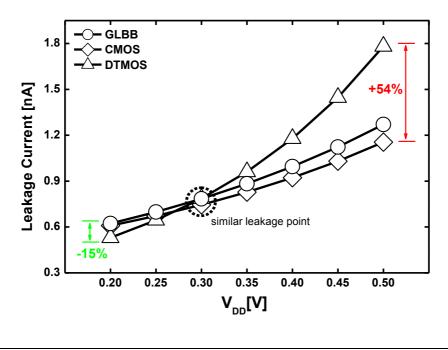

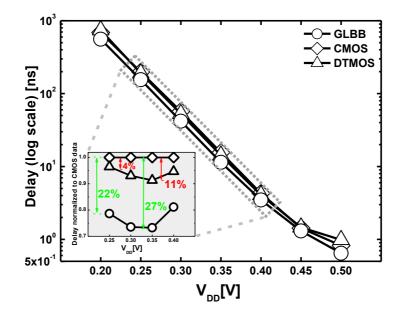

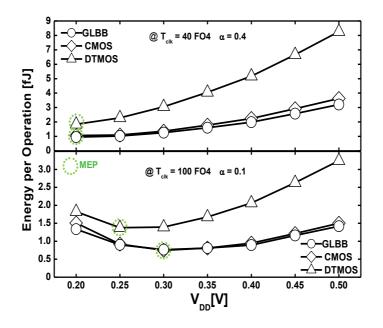

Following, a preliminary analysis performed on basic gates demonstrated that the speed boosting provided by the gate-level body biased (GLBB) allows to reach performances which are unaffordable for both conventional CMOS and DTMOS configurations. Subsequently parasitic effects of body biasing were taken into account by post layout simulations of a GLBB mirror full adder and compared against its conventional CMOS and DTMOS counterparts. The physical design of the compared circuits was carried out considering the design rules imposed by the ST 45 nm bulk CMOS triplewell technology. Despite of the large area occupancy compared to conventional CMOS, comparative post layout results have shown that the GLBB design style is, at the parity of leakage power consumption, able to obtain significantly higher performance with reduced total energy per operation consumption.

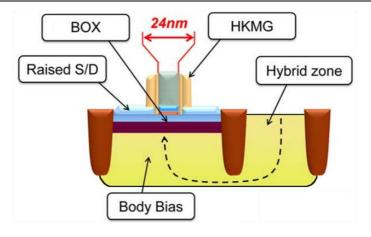

The ultra-thin box and body (UTBB) fully-depleted silicon-on-insulator (FD-SOI) technology is emerging as a valid platform to cope with ULV design bottlenecks in the more scaled technology nodes. The fully depleted channel of devices in this technology avoids the issue of the random dopant fluctuation, thus reducing the impact of process variability. Moreover, the ultra-thin (<30 nm) buried oxide (BOX) guarantees a good electrostatic control of the channel and allows more effective body biasing with respect to bulk CMOS to be applied. The latter is a key feature of the UTBB FD-SOI technology which improves the benefits of the FBB technique for ULV designs in advanced technologies.

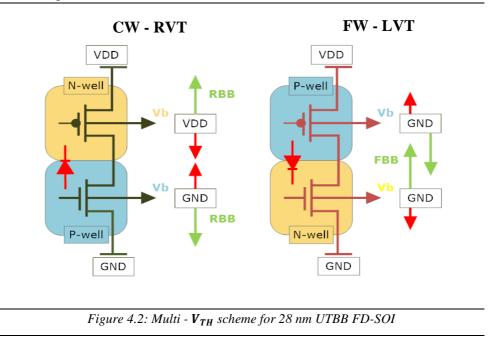

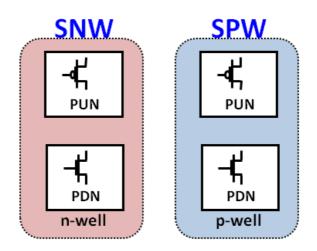

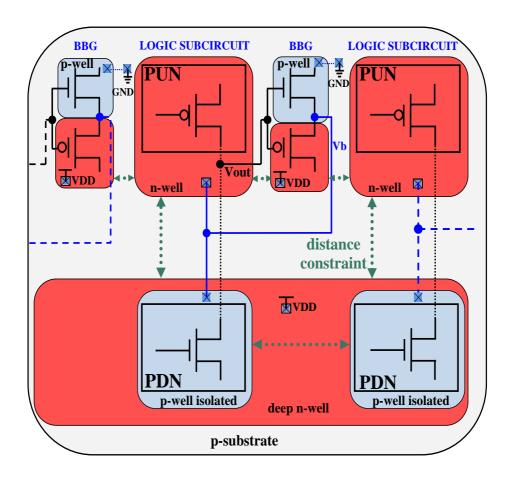

In order to reduce the area occupancy of the GLBB technique, several benchmarks has been implemented according to the GLBB technique in 28 nm STM UTBB FD-SOI technology for ULV logic design. The unique feature offered by the technology to integrate PMOS and NMOS devices into a common well configuration has been exploited to achieve improvements in terms of both performance and area.

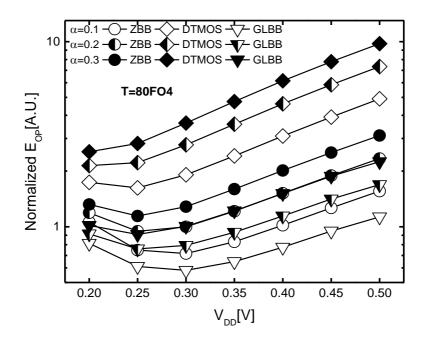

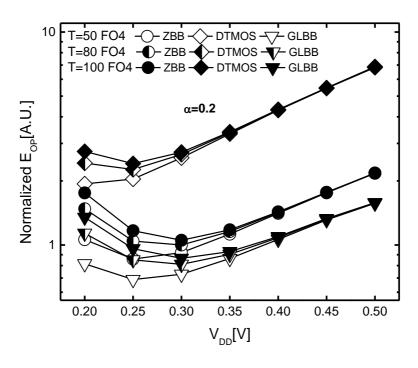

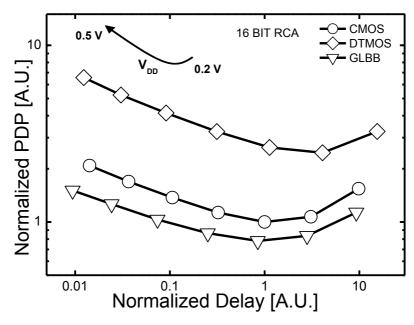

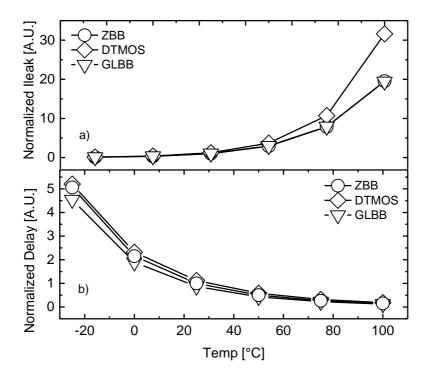

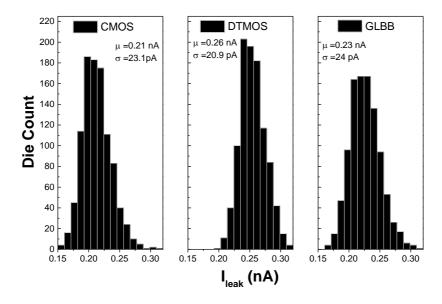

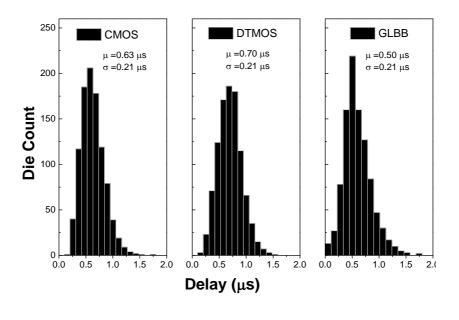

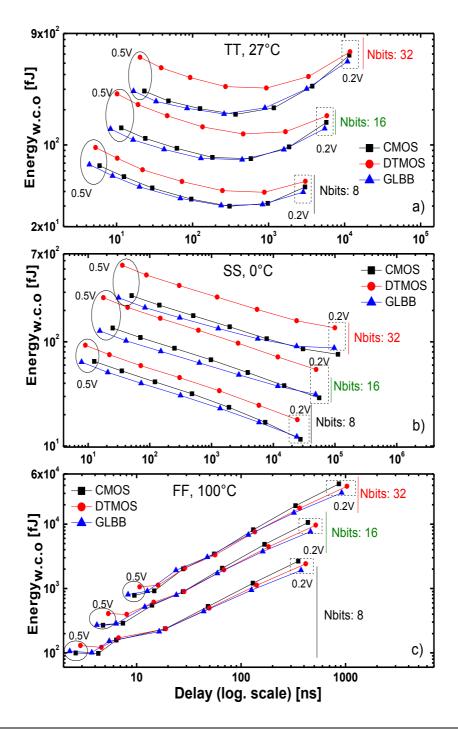

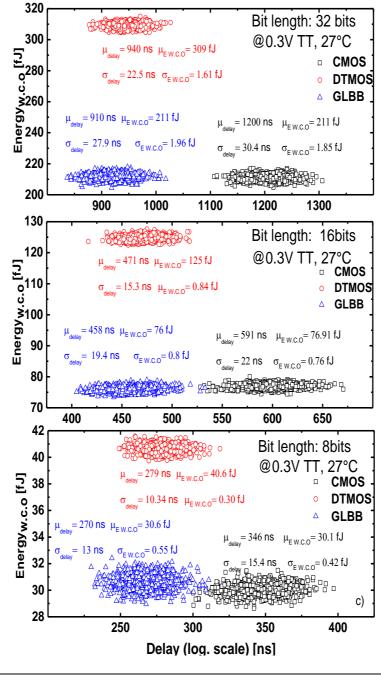

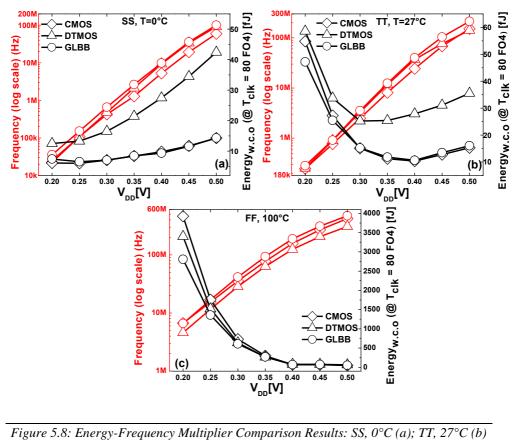

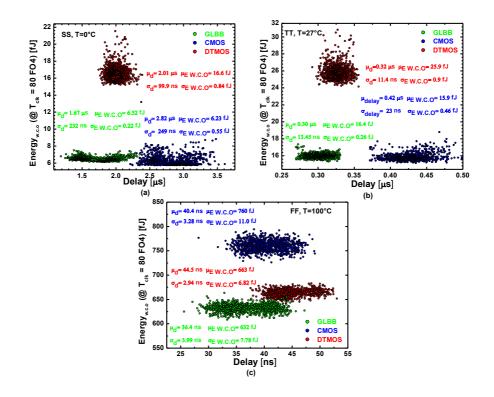

The efficiency of the GLBB technique for ULV design in UTBB FD-SOI is evaluated by considering three arithmetic benchmarks in ascending order of complexity. As a first benchmark, the GLBB mirror full adder (FA) was considered. As a second benchmark a n-bit RCAs were designed according the evaluated techniques under a wide range of process and temperature (PT) conditions. For the TT/27°C condition, the DTMOS technique shows higher energy consumption mainly due to the larger input capacitances of DTMOS gates. On the contrary, GLBB and CMOS designs exhibit very similar Energy for the worst case operation (E W.C.O.) values, even for long chains of FAs. The GLBB designs always demonstrate better performances than their competitors. For example, at VDD=0.4 V, an advantage of 33% and 46% is achieved in terms of speed and energy when compared to CMOS and DTMOS designs, respectively.

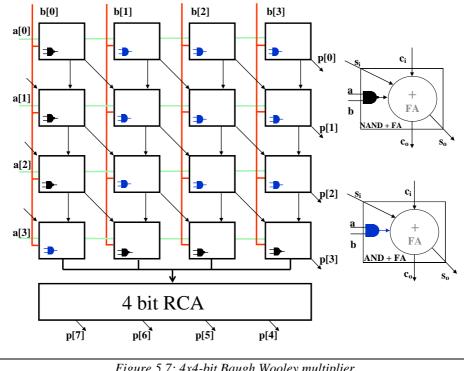

As third benchmark, a 4 x 4-bit Baugh Wooley multiplier was evaluated. At VDD = 0.3 V, the proposed approach leads to a delay reduction of about 30% with respect to a conventional static CMOS design. Such results were obtained while maintaining similar energy consumption and at the only expense of about 13% larger area. Significantly better energy (39%) and area (34%). The above delay and energy benefits are maintained over a wide range of PVT variations.

## Sommario

Lo scaling della tensione di alimentazione (VDD) al di sotto della tensione di soglia dei transistor (VTH) è uno degli approcci più efficaci per ottenere un basso consumo energetico a discapito di un'elevata riduzione delle prestazioni e una sensibilità molto più elevata alle variazioni di processo e di temperatura. Sebbene accettabile per un mercato di nicchia, l'elevato ritardo e la ridotta robustezza dei circuiti sottosoglia CMOS convenzionali possono essere molto limitativi per una gamma più ampia di applicazioni. Al fine di incrementare le prestazioni e la robustezza contro variazioni di processo e di temperatura, pur mantenendo elevati livelli di efficienza energetica, la tecnica di polarizzazione diretta del bulk/body dei transistori (forward body biasing - FBB) può essere adottata.

La tecnica FBB può essere applicata (anche dinamicamente) a diversi livelli di granularità che vanno dal livello di macroblocco al livello di singolo transistor. Applicando la tecnica FBB a livello di macro blocco si riduce il numero di segnali destinati al controllo della tensione di body, riducendo così la complessità del routing. Di contro, si riduce la flessibilità di controllo della tensione di soglia dei singoli transistori con un impatto negativo sul consumo energetico. Diversamente, l'implementazione della tecnica FBB a livello di singolo transistore permette di gestire con minore granularità la tensione di body dei mosfet. Così facendo è possibile agire, incrementandone le prestazioni, solo sui transistori che sono coinvolti nella determinazione del path critico del circuito.

Un esempio di applicazione della tecnica FBB a livello di singolo transistor è rappresentato dalla logica a "tensione di soglia dinamica" (DTMOS). Tale logica utilizza transistor i cui terminali di gate sono collegati al substrato. Di conseguenza, la tensione di soglia del dispositivo cambia dinamicamente in funzione della tensione di gate e quindi della tensione di substrato. Pertanto, nello stato di ON, la tensione di soglia diminuisce, garantendo così una corrente di ON più elevata rispetto alla configurazione standard CMOS. D'altra parte, il comportamento dei transistor in logica DTMOS nello stato di OFF è simile a quello della configurazione CMOS standard. Tuttavia, l'utilizzo della configurazione DTMOS provoca un significativo incremento delle capacità di input rispetto a una porta statica CMOS. Inoltre, la logica DTMOS comporta un maggiore consumo di energia dovuto al verificarsi di eventi di carica/scarica del substrato non necessari per segnali di ingresso che non producono una variazione della tensione di uscita della porta.

In questa tesi è stata proposta una tecnica di polarizzazione dinamica del substrato (gate level body biasing - GLBB) da impiegare a livello di porta logica per ridurre il consumo di energia nelle porte logiche DTMOS e garantire allo stesso tempo una maggiore frequenza di switching. L'implementazione di questa tecnica consente di ottenere capacità di input identiche a quelle delle porte logiche CMOS standard. Inoltre, quando la commutazione dei segnali di ingresso non produce un cambiamento di stato della porta logica, le capacità di substrato non si caricano/scaricano come avviene nella logica DTMOS, consentendo perciò un notevole risparmio di energia.

Inizialmente, è stato sviluppato un modello analitico per validare la tecnica proposta. In questa prima fase, l'inverter è stato adottato come circuito di riferimento per ricavare le principali linee guida per la progettazione del generatore di polarizzazione del substrato e della sezione logica della porta. Inoltre, sono state analizzate anche alcune porte logiche con transistor connessi in serie (ad esempio, NAND2 e NOR2), ottenendo un buon accordo tra i risultati predetti con il modello analitico e quelli ottenuti con le simulazioni.

Successivamente, è stata effettuata un'analisi preliminare su porte logiche basilari per dimostrare che l'impiego della tecnica di polarizzazione del substrato a livello di porta logica consente di ottenere prestazioni superiori alle configurazioni CMOS standard e DTMOS. In seguito, sono state effettuate anche simulazioni post-layout di un circuito "mirror full adder" realizzato con la tecnica GLBB per includere gli effetti parassiti della polarizzazione del substrato. I risultati di queste simulazioni sono stati confrontati con quelli ottenuti per lo stesso circuito realizzato con le tecniche CMOS standard e DTMOS. La progettazione dei circuiti da confrontare è stata realizzata utilizzando la tecnologia ST 45-nm bulk CMOS triple-well. I risultati comparativi hanno dimostrato che la tecnica di progettazione GLBB, a parità di consumo di potenza di leakage, consente di ottenere un significativo incremento delle prestazioni con un ridotto consumo di energia, a discapito di una maggiore occupazione di area rispetto alla logica CMOS convenzionale.

La tecnologia "ultra-thin box and body (UTBB) fully-depleted silicon-oninsulator (FD-SOI)" sta emergendo come una valida soluzione per la progettazione di circuiti a bassissima tensione di funzionamento (ultra low voltage -ULV) in nodi tecnologici sempre più scalati. La presenza di un canale completamente svuotato nei dispositivi realizzati con questa tecnologia consente di eliminare il problema della fluttuazione causale del drogaggio e quindi di ridurre l'impatto della variabilità di processo. Inoltre, il ridotto spessore dell'ossido sepolto (<30 nm) assicura un buon controllo elettrostatico del canale e quindi un più efficace impatto della tecnica di polarizzazione del substrato rispetto alla tecnologia CMOS convenzionale. Quest'ultima rappresenta la caratteristica chiave della tecnologia UTBB FD-SOI, che consente di incrementare i benefici della tecnica FBB nella progettazione di circuiti ULV implementati in nodi tecnologici avanzati.

Diversi circuiti di test sono stati implementati nella tecnologia 28-nm STM UTBB FD-SOI allo scopo di ridurre l'occupazione di area dovuto all'uso della tecnica GLBB. Difatti, grazie alla peculiarità offerta da tale tecnologica di integrare transistor PMOS a NMOS in una configurazione a substrato comune, notevoli miglioramenti sono stati ottenuti sia in termini di prestazioni che di occupazione di area.

L'efficienza della tecnica GLBB per progetti ULV in tecnologia UTBB FD-SOI è stata valutata considerando tre differenti circuiti aritmetici di test in ordine crescente di complessità. Il primo circuito di test considerato è stato un "mirror full adder". Il secondo circuito di test è stato un "ripple carry adder - RCA" a *n* bit, analizzato per studiare l'impatto delle differenti tecniche di progettazione in un'ampia gamma di condizioni di processo e temperatura. Nelle condizioni TT/27°, la tecnica DTMOS ha mostrato un elevato consumo di energia, principalmente dovuto alle elevate capacità di input nelle porte logiche DTMOS. Al contrario, i circuiti progettati con le tecniche GLBB e CMOS standard hanno esibito un analogo consumo di energia nelle condizioni operative peggiori (worst-case operation), anche in presenza di lunghe catene di full adder. Inoltre, il circuito GLBB ha mostrato sempre le migliori prestazioni. Ad esempio, con una VDD di 0.4 V, il circuito GLBB consente di ottenere un vantaggio del 33% e del 46% in termini di velocità ed energia rispetto ai circuiti CMOS standard e DTMOS.

Infine, è stato analizzato come terzo circuito di test un moltiplicatore 4 x 4bit Baugh Wooley. Con una VDD di 0.3 V, l'approccio proposto ha portato ad una riduzione del ritardo di circa il 30% rispetto al circuito CMOS standard. Questi risultati sono stati ottenuti mantenendo inalterato il consumo di energia, a discapito solo di un incremento di area del 13%. Da un confronto con la logica DTMOS si è ottenuto invece un risparmio di energia di circa il 39% ed una riduzione dell'area del 34%. I precedenti benefici in termini di ritardo ed energia sono mantenuti entro un'ampia gamma di variazioni PVT.

# One

## 1 Introduction & Background

#### 1.1 Toward High Speed and Energy - efficient Designs

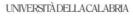

The ever increasing demand for portable devices to achieve enhanced productivity, a better user experience and multimedia quality drive innovation in digital circuit systems. In the late 1990s, the first commercial phone weighed 16 ounces and had half-hour of talk time. This GSM phone equipped with a simple RISC processor run at 26MHz and supported a primitive user interface [1]. After a steady increase in clock frequency to roughly 300MHz in the early 2000s, there has been a sudden spurt towards 1GHz and beyond [2]. More than 10 years later a wide set of computing capabilities (such as video processing, augmented reality, etc.) are offered by portable devices. Figure 1.1 illustrates the major trends from 2004 to 2014 in smartphones and tablets relevant to digital circuits.

Figure 1.1: Application processor trends in smart phones from 2004 to 2014 [2]

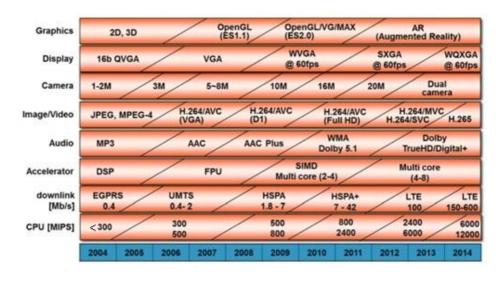

Such impressive achievements have been obtained thanks to the miniaturization of the integrated digital circuits. In 1965 Gordon Moore predicted that technology scaling will allow to increase the number of components to the double every 12-24 months at minimum economical cost [3]. This

Figure 1.2: Real scaling trends over the years 1975-2010 obeying the Moore's law [3].

trend has been followed by semiconductor industry as shown in Figure 1.2 increasing to millions the transistor count per chip.

In general, a CMOS technology when is scaled to the next generation node improves: (1) transistor and interconnection speed, (2) transistor density and (3) switching energy consumption [4]. Although portable devices have been taking advantage of technology scaling to offer higher performance, in the last years as technology nodes enters into the deep submicron era, leakage power consumption rises as a main issue.

To be more specific, traditional scaling of FETs consists in the reduction of supply-voltage ( $V_{DD}$ ) and threshold - voltage ( $V_{TH}$ ) to accommodate both performance and power requirements, but the increasing impact of leakage currents and number of transistors on a single chip has placed limits on this scaling strategy.

At circuit level, voltage scaling (with a fixed threshold voltage) has been demonstrated as the most efficient solution for power constrained applications [5]–[9]. In 1991, some digital signal processors operated at the lower 3V range in the 0.8 µm node. The authors realized that 5V specifications could be relaxed for their performance requirements therefore they operate at lower voltage to dissipate less power [1].

Voltage scaling is certainly a very effective lever to reduce energy and power consumption at expense of performance. As it can be easily observed by Equation (1.1) leakage power has a linear dependency on  $V_{DD}$ :

$$P_{leak} = V_{DD}I_{leak}$$

(1.1)

Thus decreasing  $V_{DD}$  down to a voltage level lower than  $V_{TH}$  linearly reduces leakage power by from 2.5 x to 9 x for various technologies as shown in Table 1.1

| Technology<br>node (V <sub>DD</sub> . nominal) | 65 nm (1V) | 0.13 μm (1.2V) | 0.18 μm (1.8V) |

|------------------------------------------------|------------|----------------|----------------|

| V <sub>DD</sub> (subthreshold)                 | 1          | 1.2            | 1.8            |

| 0.4                                            | 2.5 X      | 3 X            | 4.5 X          |

| 0.3                                            | 3.3 X      | 4 X            | 6 X            |

| 0.2                                            | 5 X        | 6 X            | 9 X            |

Table 1.1: Leakage power saving from  $V_{DD}$  reduction [10]

Additionally, as it is shown by the well-known equation of dynamic energy consumed by a digital circuit in (1.2).

$$E_{active} = C_{eff} V_{DD}^2$$

(1.2)

As  $V_{DD}$  is reduced, quadratic energy savings are obtained since effective switching capacitance are maintained. Again, scaling  $V_{DD} < V_{TH}$  reduce considerable dynamic energy by from 60 x to 80 x as shown in Table 1.2

Table 1.2: Dynamic Energy saving form  $V_{DD}$  reduction [10]

| Technology<br>node (V <sub>DD</sub> . nominal) | 65 nm (1V) | 0.13 μm (1.2V) | 0.18 µm (1.8V) |

|------------------------------------------------|------------|----------------|----------------|

| V <sub>DD</sub> (subthreshold)                 | 1          | 1.2            | 1.8            |

| 0.4                                            | 6.25 X     | 9 X            | 20.25 X        |

| 0.3                                            | 11.1 X     | 16 X           | 36 X           |

| 0.2                                            | 25 X       | 36 X           | 81 X           |

Although operation in sub threshold regime demonstrates significant power and energy saving compared to strong-inversion operation, significant performance loss and higher sensitivity to variations occur [11]–[24]. Such limitations have maintained subthreshold digital design for a strictly narrow set of applications while a broader market demand high performance and energy-efficient designs.

### 1.2 Ultra-low Voltage (ULV) digital design: Characteristics and Issues

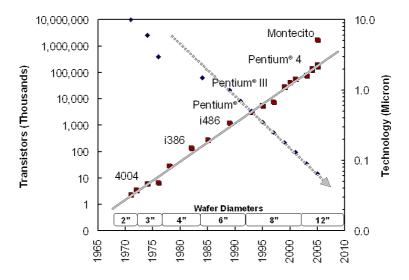

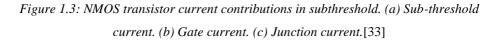

As  $V_{DD}$  is reduced to minimize energy per operation, FETs make the transition from strong inversion with large gate overdrive to subthreshold operation in weak inversion. Current of a NMOS transistor operating in subthreshold regime has three main contributions as illustrated in Figure 1.3: (a) the subthreshold current  $I_{ST}$ , due to diffusion of minority carriers between drain and source [25], (b)  $I_G$  due to tunneling through the dielectric and (c)  $I_J$  mainly due to band-to-band tunneling current across the thin depletion regions [26]. Because of the stronger dependence on the gate voltage,  $I_G$  and  $I_J$  tend to be much lower than  $I_{ST}$  at low voltages. Hence the NMOS current operating at subthreshold region represented in (1.3) is mainly dominated by  $I_{ST}$ .

$$I_{D:subthreshold} \approx I_{ST} = I_0 \exp\left(\frac{V_{GS} - V_{TH}}{nV_T}\right)$$

(1.3)

Subthreshold operation differs from strong inversion operation primarily because the  $I_{ST}$  depends exponentially on threshold voltage ( $V_{TH}$ ) and gate - source voltage ( $V_{GS}$ ), while the typical strong inversion operation oncurrent ( $I_{on-super}$ ) depends roughly linearly on  $V_{TH}$  and  $V_{GS}$ .

The exponential characteristic of  $I_{ST}$  drastically affect circuit behavior in several aspects such as the exponential performance degradation, large pMOS / nMOS imbalance and higher sensitivity to variations.

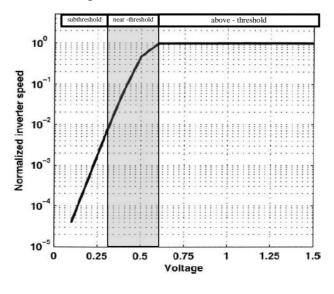

A first issue of circuits operating in subthreshold region is that the delay increase exponentially due to the dependency of the current on  $V_{TH}$  and  $V_{DD}$ . As observed in Figure 1.4 the normalized speed of the basic inverter has two clear stages as  $V_{DD}$  is reduced: (1) in strong operation region the speed slightly decrease with voltage, (2) in sub/near threshold, an exponential decrease in speed is clear. Large performance decrease in subthreshold regime severely limits the range of applications to those requiring medium or slow speeds.

Figure 1.4: Relative inverter speed through all the power supply range

A second important issue in ULV digital designs is the high imbalance between the nMOS and pMOS strength. Symmetrical pMOS and nMOS currents ensure adequate noise margin, reasonably symmetric rise-fall transitions and reduce minimum voltage operation [27]. At subthreshold regime operation, the nMOS/pMOS imbalance is typically much higher than above threshold operation [28]–[30]. For example in the specific case of 65 nm technology the nMOS/pMOS imbalance is obtained by increasing pMOS strength by 7 at the expense of larger capacitances [31].

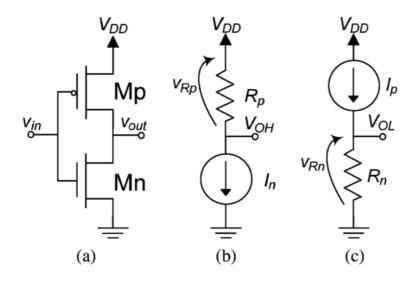

The large nMOS/pMOS imbalance at ULV operation has important consequences on the DC behavior. Figure 1.5 represents the model of an inverter for b) low and c) high voltage input. The on transistor Mn is equivalent to a current source, whereas Mp is equivalent to a resistance. From the resulting equivalent model of the inverter the output voltage  $V_{OH}$  suffers a voltage drop  $\Delta V_{OH}$  across Mn [1], [27]:

$$V_{OH} = V_{DD} - \Delta V_{OH}$$

$$\Delta V_{OH} = R_P I_n = v_T \frac{\beta_n}{\beta_p} e^{-V_{DD}/n_n v_t}$$

(1.4)

Similarly, for a high voltage input

$$\Delta V_{OL} = v_T \frac{\beta_p}{\beta_n} e^{-V_{DD}/n_n v_U}$$

(1.5)

Where  $\beta_n$ ,  $\beta_p$  are nMOS, pMOS strength respectively. From (1.4) and (1.5), the output levels are exponentially degraded as  $V_{DD}$  is reduced, and their values depend on the nMOS/pMOS strength ratio. In other words

CMOS logic at ULV operation suffers a degradation in the output logic level, hence on the voltage swing [27].

A side effect of voltage swing degradation is the increase in the leakage power consumption of the subsequent logic gate. To be more specific a degradation of  $\Delta V_{OL}$  in the ouput voltage determines an equal increase in the gate-source voltage of the off nMOS transistor in the next logic gate. Thus a perfect nMOS/pMOS balance should be achieved by increasing the strength (i.e. increase the sizing and/or reducing  $V_{TH}$ ) of the weaker transistor.

*Figure 1.5: a) Schematic of the inverter gate and equivalent representation for b) high input and c) low input voltages* [33]

And third, as shown in (1.3) the exponential dependence of  $I_{ST}$  on  $V_{TH}$  means that variations due to random doping fluctuations has a larger impact than above threshold operation. Thus the previously discussed issues of subthreshold digital designs are more critical taking into account process (P) variation [32]. For example, the large impact in the nMOS/pMOS imbalance presented before increases ~2X taking into account process var-

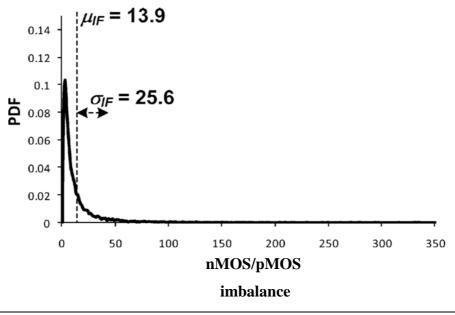

iation. The data obtained from Monte Carlo simulations in the 65nm technology is plotted in Figure 1.6 the shape of the PDF presents a mean value of  $\mu = 13.9$  and a standard deviation of  $\sigma = 25.6$ . Hence the increasing factor of pMOS strength by 7 mentioned in the previous analysis is underestimated taking into account process variations. Indeed this large underestimation is due to the large variability of  $\sigma/\mu = 185\%$  [33].

Figure 1.6: Probability density function of the nMOS/pMOS imbalance from 10,000 Monte Carlo simulations under itradie and interdie variations [33]

#### **1.3** Minimum Energy per Operation

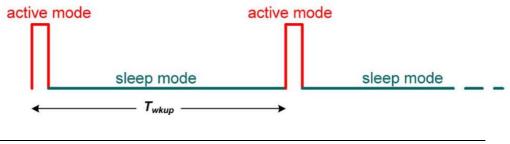

In ULV systems a repetitive short task is performed at a given wake up period  $T_{wkup}$ . Thus, as shown in Figure 1.7, power consumption can be drastically reduced through duty cycling. Duty cycling systems contain two blocks: (1) a very simple always – on block that stores information and periodically triggers a (2) more complex block which works in active mode

for about 0.1% - 1% of the period and in sleep mode for most of the time according to the application [33].

Figure 1.7: Operation of duty - cycled blocks in Ultra Low Power systems.[33]

In duty-cycled ULV systems the average consumption is equal to

$$P_{avg} = P_{always-on} + P_{sleep} + \frac{E_{active}}{T_{wkup}}$$

#### (1.6)

Where  $P_{always-on}$  is the average power consumed by the always-on blocks,  $P_{sleep}$  and  $E_{active}/T_{wkup}$  is the average power consumed by duty cycled block in sleep and active mode respectively. Since duty cycled block is far more complex than always on circuitry  $P_{sleep}$  easily ceeds  $P_{always-on}$ . Indeed in applications with a fraction of a second wake up period (or less) energy consumed by duty cycled blocks in active mode dominates  $P_{avg} \approx E_{active}/T_{wkup}$ . This justifies the extensive research in the last decade in digital circuit designs toward minimum energy per operation. To be more specific ULV design should be optimized for low power consumption (always on block) and minimize energy per operation (consumed by more complex duty cycled block) during active mode.

For large classes of circuits, minimum energy consumption occurs when the voltage is scaled below the device threshold voltage ( $V_{GS} < V_{TH}$ ) [1], [34]. In this region, energy consumption can be reduced by 20x compared to standard superthreshold ( $V_{DD} > V_{TH}$ ) operation at the cost of circuit performance [35].

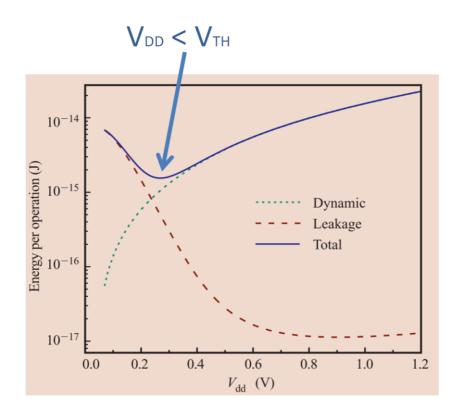

Figure 1.8 illustrates that as  $V_{DD}$  is reduced a minimum energy point is achieved due to the trade - off between static and dynamic energy at a specific power supply  $V_{DD}$  and voltage threshold  $V_{TH}$ .

Figure 1.8: Minimum Energy Operation Point for a fixed threshold voltage [35].

As shown in Figure 1.8 minimum energy consumption relies upon a compromise between dynamic ( $E_{DYN}$ ) and leakage ( $E_{LEAK}$ ) energies, expressed in (1.7), **Errore. L'origine riferimento non è stata trovata.** [36], [37], assuming rail-to-rail swing ( $V_{GS} = V_{DD}$ )

$$E_{DYN} = C_{eff} V_{DD}^2$$

$$(1.7)$$

$$E_{LEAK} = I_{leak} V_{DD} T_D$$

$$(1.8)$$

Thus taking into account the  $I_{ST}$  the total energy as presented in [1] is,

$$E_{TOT} = E_{DYN} + E_{LEAK}$$

$$E_{TOT} = V_{DD}^2 \left( C_{eff} + W_{eff} K C_g L_{DP} \exp\left(\frac{-V_{DD}}{nv_t}\right) \right)$$

(1.9)

Where  $L_{DP}$  is the depth of critical path in characteristic inverter delay,  $C_{eff}$  is the average effective switched capacitance of the entire circuit, including the average activity factor, short circuit current, glitching effects, etc.  $C_{eff}$  and  $W_{eff}$  estimates the total width, related to the characteristic inverter, that consumes leakage current.

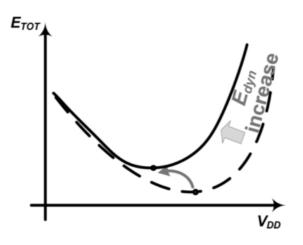

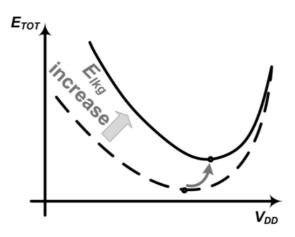

Equation (1.9) indicates that the location of the minimum energy operation point is entirely determined by the operating scenario, environment and temperature of the circuit. To be more specific any decrease in  $E_{LEAK}$  or increase  $E_{DYN}$  will push the optimum  $V_{DD}$  to lower values. On the contrary increase in  $E_{LEAK}$  or decrease  $E_{DYN}$  will push the optimum  $V_{DD}$  to larger values. These types of changes can occur for a given circuit without changing its intrinsic attributes.

Figure 1.9 shows the impact of varying the activity factor on the energy characteristics. The  $E_{DYN}$  increases in proportion to the activity factor due to the amount of switched capacitance per operation thus optimum power supply shifts toward lower values. On the contrary Figure 1.10 shows the

impact of changing duty cycle on the energy characteristics. A longer idle time spent for each operations increments leakage energy consumption and the minimum energy point moves to higher voltages.

Figure 1.9: Energy versus **V**<sub>DD</sub> varying workload in a 8-bit 8-tap FIR filter [1]

Figure 1.10: Energy versus  $V_{DD}$  varying duty cycle in a 8-bit 8-tap FIR filter [1]

#### 1.4 Body Biasing as an efficient knob in ULV operation

Even though energy has become increasingly important, the attention has focused on the high performance tail of the energy-delay Pareto curve. Designers tried to minimize energy consumption while meeting high performance frequency constraints. As demonstrated by [33], [38], [39][40] body biasing is considered as an effective knob for tuning the transistor strength and the impact to alleviate issues raised by subthreshold operation such as large performance degradation and sensitivity to variations.

For this analysis an extended expression of (1.3) is presented taking into account the width, length of the transistor, usually written in the following form [25],[41]:

$$I \approx I_{ST} = I_0 \frac{W}{L} e^{\left(\frac{V_{GS} - V_{TH}}{nv_t}\right)} (1 - e^{(-V_{DS}/v_t)})$$

(1.10)

Where  $I_0$  is the technology-dependent subthreshold current extrapolated for  $V_{GS} = V_{TH}$ . In (1.10) the threshold voltage  $V_{TH}$  also depends on the drain-source voltage  $V_{DS}$  and bulk-source voltage  $V_{BS}$  through DIBL and body effect, respectively.

$$V_{TH} = V_{T0} - \lambda_{DS} V_{DS} - \lambda_{BS} V_{BS}$$

(1.11)

$\lambda_{DS} > 0$  is the DIBL coefficient and  $\lambda_{BS} > 0$  is the body coefficient [4]. For a better insight, it is convenient to rewrite (1.10) and (1.11) according to [33]:

$$I = \beta e^{\left(\frac{V_{GS}}{nv_t}\right)} \left[ e^{\lambda_{DS}/nv_t} \left( 1 - e^{-V_{DS}/v_t} \right) \right]$$

(1.12)

$$\beta = I_0 \frac{W}{L} e^{-(V_{TO} - \lambda_{BS} V_{BS})/nv_t}$$

(1.13)

Where the exponential dependence on  $V_{GS}$  and  $V_{DS}$  is highlighted and all other terms related to the transistor strength are grouped in the parameter  $\beta$ .

From (1.13) the transistor strength can be tuned by three parameters: aspect ratio W/L, threshold voltage  $V_{TO}$  and statically or dynamically tuning the bulk voltage  $V_{BS}$ .

Is easy to observe that W/L has a linear dependency in  $\beta$  and an implicit dependence in  $V_{TH}$  which is significant for narrow or short channels. More specifically, an increase in W leads to threshold increase due to narrow channel effect (RNCE) [25]. Additionally as shown in (1.9) the increase in transistor sizes will increment  $C_{eff}$  rising the energy consumption. Theoretically minimum energy circuits should use minimum sized. As a result, W is not an effective knob to increase the strength of the transistor

A more effective knob to tune the strength of the transistor is  $V_{T0}$  and  $V_{BS}$  thanks to the exponential dependency on  $\beta$ . As an example we compared two  $V_{T0}$  flavors offered in the 65nm technology:  $low - V_{TH}$  transistors are about 18 times stronger compared to  $std - V_{TH}$  transistors with the same sizing.

Similarly body biasing has a significant impact in  $\beta$ . Applying a Forward Body Bias (FBB) of  $V_{BS} = 300mV$  transistor strength increased 2.3X compared to Zero Body Bias  $V_{BS} = 0 mV$  [33].

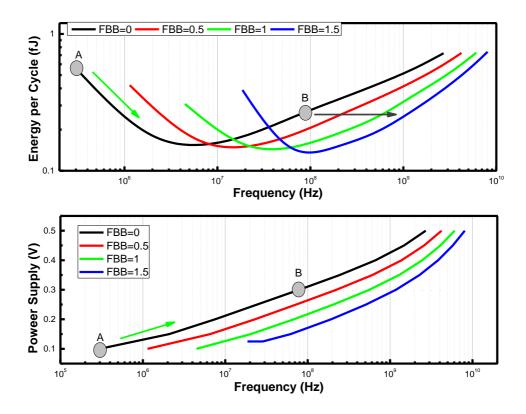

It should be mention that FBB can be applied dynamically to satisfy ondemand application requirements. Due to the high impact on the transistor strength and freedom to manage  $V_{BS}$  at different levels of abstraction (i.e. gate-level, circuit-level, etc.)  $V_{BS}$  is an efficient knob to achieve minimum energy consumption for a wide operating scenarios. This principle is better explained in the Figure 1.11. The location of the minimum energy operation point is determined by the tradeoff between  $E_{LEAK}$  and  $E_{DYN}$  thus  $V_{DD}$ and  $V_{BS}$  can tune the performance at run time in the most energy-efficient way. In point A ( $E_{lkg} \gg E_{dyn}$ ) (low activity), performance should be increased by increasing  $V_{DD}$  since this leads to an exponential performance increase and energy decrease. On the other hand in point B ( $E_{dyn} \gg E_{lkg}$ ), performance should be increased by Body Bias, since this leads to an exponential performance increase and a fairly small energy increase.

In conclusion the most powerful knobs to tune the performance at run time are the supply voltage  $V_{DD}$  and the body bias voltage  $V_{BS}$ . The above discussed guidelines demonstrates that dynamic body bias should be used for circuits under timing constraints.

Figure 1.11: Energy per cycle under timing constraints shows  $V_{BS}$  and  $V_{DD}$  as powerful knobs to tune the performance and energy at run time

#### 1.5 Logic family exploiting Dynamic Body Biasing in ULV

The body biasing can be applied (also dynamically) at different levels of granularity ranging from macro-block level to the transistor level. The key rationale for applying, such a technique at the macro-block level is to amortize the silicon area and the body control signal routing complexity of a finer grained implementation. As a drawback, when V<sub>TH</sub> is reduced at the block level to compensate for variations and/or to provide a temporary speed boost, leakage power is increased for all the gates in the block, while speed-up would be needed only on timing critical gates. Better energy-delay tradeoffs can be obtained by reducing the body-bias control granularity, at the expense of larger silicon area occupancy [42]–[44].

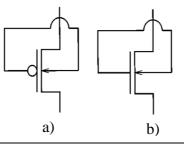

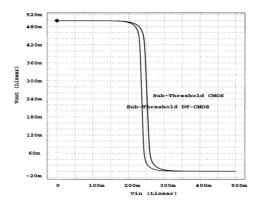

Dynamic Threshold MOSFET (DTMOS) is a logic family introduced in [19] which exploits dynamic body biasing at gate level without using additional circuitry control. In this logic family as the substrate voltage varies with the gate voltage, the  $V_{TH}$  of the device is dynamically changed. When the device is turned ON, its threshold voltage is forced to drop, thus allowing a much higher ON current than a standard MOSFET. For example in the off-state  $V_{in} = 0$  ( $V_{in} = V_{DD}$ ) for nMOS (pMOS) the characteristics are exactly the same as a regular MOS transistor. On the other side, in the on state  $V_{BS}$  is FBB and thus reduces the  $V_{TH}$  of the DTMOS transistor. The subthreshold slope of DTMOS improves and approaches the ideal 60 mV/decade which makes it more efficient in subthreshold logic circuits to obtain higher gain [19]. It leads to higher oncurrent compared to conventional CMOS to drive more transistors or faster transitions and robustness.

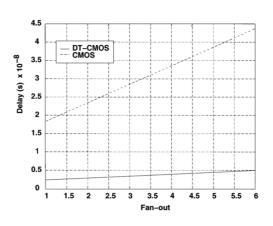

DC characteristics of DTMOS and conventional CMOS are presented in Figure 1.13. Both show a very good noise margin however, due to higher drive current capability, DTMOS logic can have a higher number of fan-

tors [19]

out, and therefore larger and more complex gates can be implemented without sacrificing the performance as presented in Figure 1.14.

Figure 1.13: Voltage Transfer Curve of conventional CMOS and DTMOS logic families

Figure 1.14: Delay versus Fan comparison for conventional CMOS and DTMOS logic families [19]

As a drawback of DTMOS the forward-biased has to be less than 0.6 V. This is to prevent forward-biasing the parasitic PN junction diode thus strong inversion operation is permitted applying limiter transistors which incur in energy consumption. As an additional drawback, the large body capacitance and resistance [45] of devices provide an additional RC delay in charging the substrate and the input nodes of the DTMOS logic gates [46]. Moreover, the substrate bias voltage of DTMOS logic gates would change also when input transitions do not imply output switching. This would charge and discharge the large body capacitances, thus wasting precious dynamic energy [47]. All the above effects can erode the expected advantages of DTMOS circuits.

#### **1.6 Purpose of this work**

This thesis work focuses on the design of energy – efficient circuits exploiting Gate-level Body Biasing (GLBB) technique, which has been proposed as an effective solution to increase speed at expense of very low energy increasing. The first chapter presents an introduction to basic concepts and design issues related to circuits operating at ultralow voltage regime. The second chapter presents an accurate model of the technique with important design guidelines validated through Cadence Spectre simulations in 45nm Bulk CMOS triple-well technology[48]. The third chapter addressed more complex designs taking into account physical limitations of the technique implemented in Bulk CMOS triple-well technology [49], [50]. In the fourth chapter, after a briefly introduction to the UTBB FD-SOI technology and distinguish the superior body biasing efficiency compared to Bulk CMOS technologies, we propose single well configuration allowed by the technology to significantly reduce the area penalty of lowgranularity body-biasing voltage control[51]. Finally, the fifth chapter presents improved performance and energy characteristics of the GLBB technique demonstrated by comparing several benchmarks (from basic gates to

a Baugh Wooley multiplier) to their conventional CMOS and DTMOS counterparts over a wide range of PVT variations[52],[53].

## Two

## 2 Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits

In this chapter the gate-level body biasing design (GLBB) technique that overcomes DTMOS logic family is explained and theoretically justified through an accurate closed-form analytical modeling. Initially, an inverter was adopted as reference circuit and the main static and dynamic behaviors were modeled with the purpose of furnishing important guidelines to design efficient digital circuits under very low voltage operation. Modeling and design criteria derived for the inverter gate are then extended to more complex logic gates with transistors' stacks. The theoretical analysis and the design considerations have been fully validated by comparing the results predicted by models with Cadence Spectre simulations performed on different process corners and for different temperatures exploiting a commercial 45-nm CMOS technology. The good agreement between the predicted and the simulated results makes the proposed modeling a valuable support during the circuit design phase

## Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits

In the first chapter the FBB has been demonstrated as an energyefficient knob to speed up a circuit and reduce the impact of variations. Furthermore, DTMOS has been analyzed as a logic family which exploits body biasing knob at gate-level. The main drawbacks of DTMOS configuration are: (1) reduced intrinsic speed advantages due to larger input capacitances than a standard CMOS and (2) unnecessary charge and discharge large body capacitances according to the input wastes precious dynamic energy [47].

In this chapter an energy efficient dynamic gate level body biasing (GLBB) technique [47] to overcome the speed and energy limits of DTMOS logic gates is presented. The proposed GLBB technique exhibit input capacitances equal to those of the standard CMOS configuration. Moreover, when input signals switch without changing the logic gate status, the body capacitances are not charged/discharged as occurs in DTMOS logic gates, thus saving considerable energy with respect to a DTMOS design.

#### 2.1 GLBB Operating Principle

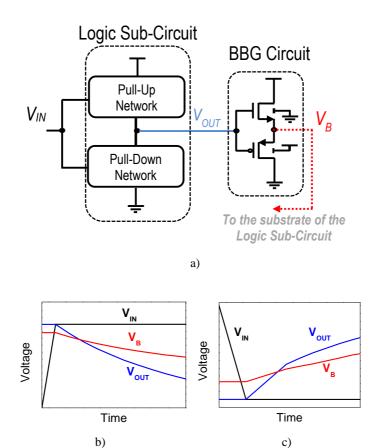

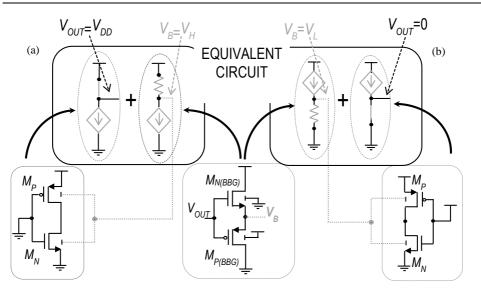

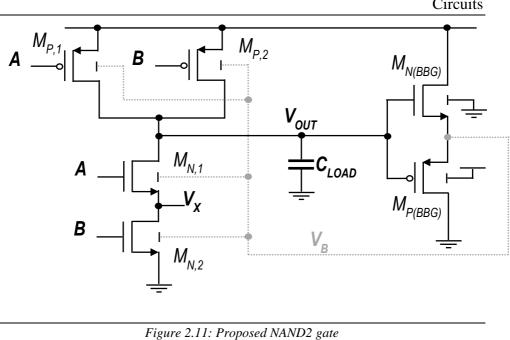

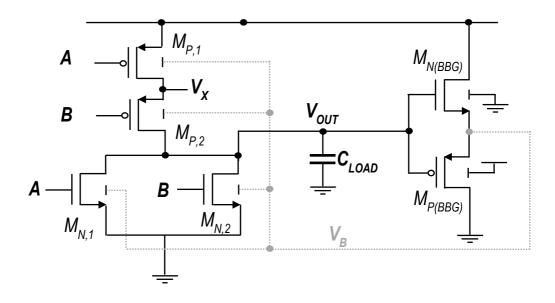

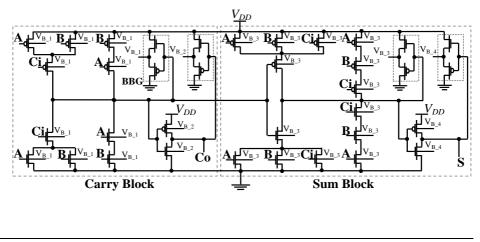

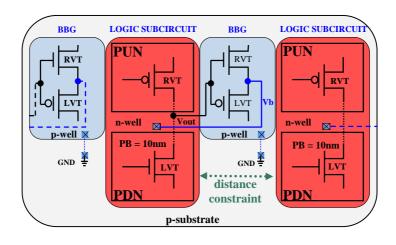

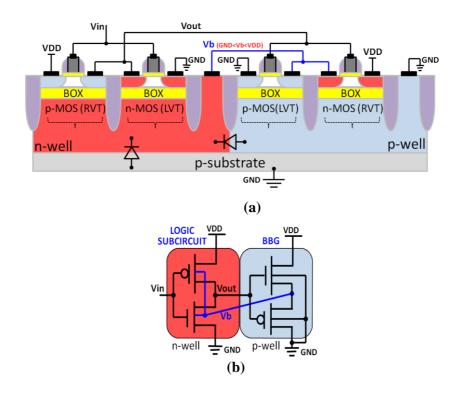

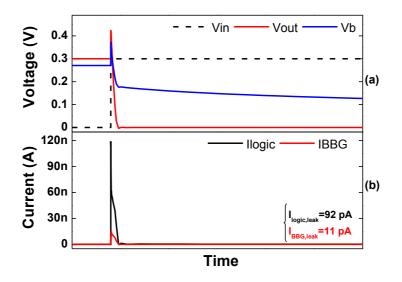

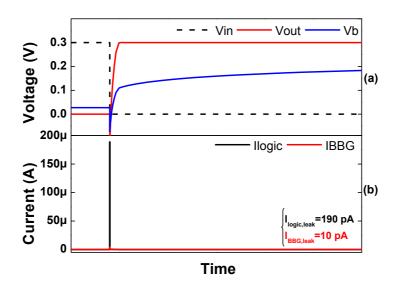

As shown in Figure 2.1 (a), the generic logic gate, designed according to the suggested approach, consists of two sub-circuits: the logic subcircuit which is responsible for the logical functionality of the gate and the body biasing generator (BBG) which manages the body voltage ( $V_B$ ) for both the pull-up and the pull-down networks. The BBG is a simple pushpull amplifier, which acts as a voltage follower for the output voltage  $V_{OUT}$ , while decoupling the large body capacitances from the output node. In Figure 2.1 (b-c) the transient behavior for the input voltage ( $V_{IN}$ ), the output voltage ( $V_{OUT}$ ) and the body voltage ( $V_B$ ) is reported for the falling and rising output transitions, respectively.

When  $V_{OUT}$  is equal to  $V_{DD}$  (0V), the BBG transfers a high (low) voltage on the  $V_B$  net, thus preparing the pull-down (pull-up) network for a faster logic gate switching. Since the MOSFETs of the switching network (either pull-up or pull-down) are already forward body biased before gate inputs' arrival, the gate output transition is largely favored by a switching current significantly higher in comparison to the case of conventional body biasing scheme.

Speed and energy advantages exist with respect to a DTMOS configuration [47]. In fact, the transition of the input signals is not slowed down from the body capacitive effects as occurs in DTMOS gates, whereas the high capacitive load seen by the BBG does not constitute a speed bottleneck, since  $V_B$  voltage is always established well before inputs' transition. On the contrary, inspecting the behavior of the BBG circuit (see Figure 2.1 (b-c)), in the proposed scheme the logic sub-circuit benefits from the large body capacitances since they allow a slower transition for the body voltage and consequently a faster transition in the output. Additionally, when input signals switch without changing the gate output voltage, the BBG does not waste energy by charging/discharging the body capacitances.

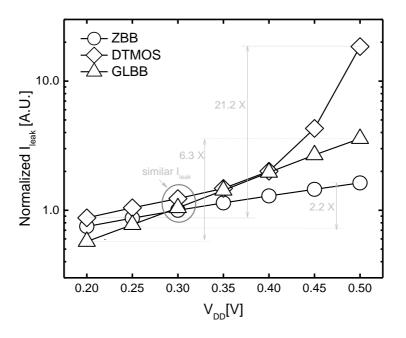

Due to the FBB effects and the additional BBG circuitry, logic gates, designed as here proposed, show increased leakage current with respect to the conventional static CMOS counterparts.

Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits

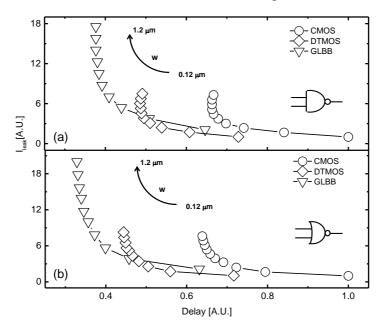

Figure 2.1: Logic gate with gate level dynamic body biasing (a) and transient behavior for falling (b) and rising (c) output voltage

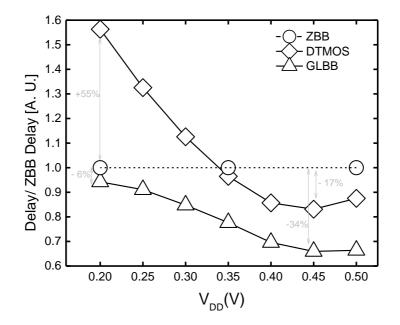

Figure 2.2 depicts (a-b) leakage current  $(I_{leak})$  versus delay curves in the case of NAND2 and NOR2 logic gates for the conventional CMOS, DTMOS and GLBB implementations, respectively. At a parity of W, the GLBB technique shows leakage current higher than the other competitors. This means that, among the different evaluated choices, the GLBB style is the less suitable if the minimization of static power. On the contrary, if the speed requirement represents the main design aim, the GLBB style becomes the most reasonable choice allowing higher performance to be

reached at the parity of leakage power consumption since the boosting action of the BBG allows the delay target to be reached using smaller transistors. Moreover, the GLBB technique allows performance ranges which are unaffordable for both CMOS and DTMOS configurations.

Figure 2.2: Leakage current-delay plots for NAND2 (a) and NOR2 (b) logic gates

### 2.2 Analytical Model

In the following, analytical models for leakage current and delay of the inverter gate, designed according to the suggested technique, are derived. The developed models are then validated by comparing the predicted results with Spectre simulations performed for the 45-nm ST CMOS Low Power technology. Moreover, the theoretical analysis is also exploited to define proper design guidelines (both for the BBG and the logic subcircuits) with the main aim to obtain fast and power efficient subthreshold logic circuits. In particular, since reducing power consumption is a main concern in subthreshold design, the obtained design guidelines were extracted by comparing the proposed approach with the conventional static CMOS style, which represents a good solution in terms of leakage power.

#### 2.2.1 Leakage Current Analysis

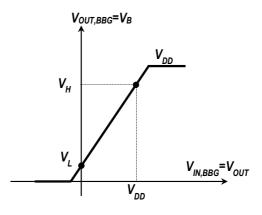

Figure 2.3 illustrates the DC transfer function of the BBG sub-circuit. Note that, in the steady state, the BBG output voltage differs from  $V_{DD}$  and 0V. This is because a nMOS (pMOS) device is used for charging (discharging) the BBG output node (see Figure 2.1(a)). In the following  $V_H$  and  $V_L$  are used to indicate the voltage transferred by the BBG when  $V_{IN,BBG} = V_{OUT} = V_{DD}$  and  $V_{IN,BBG} = V_{OUT} = 0$ , respectively.

Figure 2.3: DC transfer function of the BBG

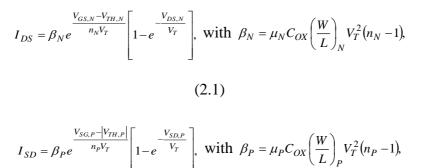

To estimate the leakage current, an analytical expression of the BBG output voltage is initially derived. The starting point is the following pair of subthreshold drain current equations for nMOS and pMOS transistors, respectively [25]:

(2.2)

where  $\beta_N$  ( $\beta_P$ ) is subthreshold current factor for the nMOS (pMOS) transistor,  $\mu_N$  ( $\mu_P$ ) is the electron (hole) mobility,  $C_{OX}$  is the oxide capacitance per unit area, W is the channel width, L is the channel length,  $V_T = kT/q$ (with k Boltzmann constant, T absolute temperature and q elementary charge) is the thermal voltage,  $n_N$  ( $n_P$ ) is the subthreshold slope factor for the nMOS (pMOS) transistor,  $V_{GS,N}$  ( $V_{GS,P}$ ) is the gate-to-source (sourceto-gate) voltage for the nMOS (pMOS) transistor,  $V_{DS,N}$  ( $V_{SD,P}$ ) is the drain-to-source (source-to-drain) voltage of the nMOS (pMOS) transistor,  $V_{TH,N}$  ( $V_{TH,P}$ ) is the threshold voltage of the nMOS (pMOS) transistor.

In (2.1),  $V_{TH,N}$  depends on  $V_{DS,N}$  through the drain induced barrier lowering (DIBL) effect and on body-to-source voltage ( $V_{BS,N}$ ) through the body effect. Similarly,  $|V_{TH,P}|$  in (2.2) depends on source-to-drain voltage  $V_{SD,P}$  and on source-to-body voltage  $V_{SB,P}$ . This is expressed by [1]: Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits

$V_{TH,N} = V_{TH,N}^{0} - \lambda_{D}^{N} V_{DS}^{N} - \lambda_{B}^{N} V_{BS}^{N}$  (2.3)  $\left|V_{TH,P}\right| = \left|V_{TH,P}^{0}\right| - \lambda_{D}^{P} V_{SD}^{P} - \lambda_{B}^{P} V_{SB}^{P},$  (2.4)

where,  $V_{TH,N}^{0} \left( V_{TH,P}^{0} \right)$  is the zero bias threshold voltage for the nMOS (pMOS) transistor,  $\lambda_{D}^{N} \left( \lambda_{D}^{P} \right)$  and  $\lambda_{B}^{N} \left( \lambda_{B}^{P} \right)$  are the DIBL and body effect coefficients of the nMOS (pMOS) device, respectively. The expression of the subthreshold drain current of the nMOS transistor in the BBG circuit is obtained by replacing in (2.1) and (2.3)  $V_{GS,N} = V_{OUT} - V_B, V_{DS,N} = V_{DD} - V_B$  and  $V_{BS} = -V_B$ . Similarly, the drain current in the pMOS transistor is obtained by replacing in (2.2) and (2.4)  $V_{SG,P} = V_B - V_{OUT}; V_{SD,N} = V_B$  and  $V_{SB,P} = V_B - V_{DD}$ . By neglecting the contribution of the term in square brackets in (2.1) and (2.2) and equating the currents of the nMOS and pMOS transistor, the following expression holds for the BBG output voltage:

$$V_B \approx \frac{V_{OUT}\left(1 + \frac{n_N}{n_P}\right) - V_{TH,N}^0 + V_{DD}\left(\lambda_D^N + \lambda_B^P\right) + \left|V_{TH,P}^0\right| - n_N V_T \ln\left(\frac{\beta_P}{\beta_N}\right)}{1 + \frac{n_N}{n_P} + \frac{n_N}{n_P} \lambda_D^P + \lambda_D^N + \lambda_B^N + \lambda_B^P}$$

$$(2.5)$$

From (2.5), both  $V_H$  and  $V_L$  can be easily evaluated, by substituting  $V_{OUT} = V_{DD}$  and  $V_{OUT} = 0V$ , respectively. Figure 2.4 shows the equivalent circuits used to evaluate the leakage current of the whole gate (logic sub-

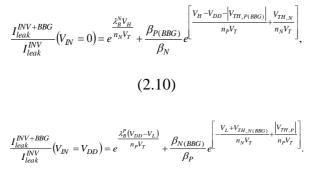

circuit + BBG) when  $V_{IN}$  is low (Figure 2.4(a)) and high (Figure 2.4(b)), respectively. Taking into account that for  $V_{IN} = 0V$  ( $V_{OUT} = V_{IN,BBG} = V_{DD}$ )  $V_B$  is equal to  $V_H$ , while when  $V_{IN} = V_{DD}$  ( $V_{OUT} = V_{IN,BBG} = 0V$ )  $V_B$  is equal to  $V_L$ , the leakage current of the proposed inverter gate can be expressed as (N(BBG) and P(BBG) indicate the nMOS and pMOS in the BBG, respectively):

$I_{leak}^{INV+BBG}(V_{IN}=0) = \beta_{N}e^{-\frac{V_{TH,N}^{0}-\lambda_{D}^{N}V_{DD}-\lambda_{B}^{N}V_{H}}{n_{N}V_{T}}} + \beta_{P(BBG)}e^{\frac{V_{H}-V_{DD}-|V_{TH,P(BBG)}^{0}|+\lambda_{D}^{P(BBG)}V_{H}+\lambda_{B}^{P(BBG)}(V_{H}-V_{DD})}{n_{P}V_{T}}},$

(2.6)

$I_{leak}^{INV+BBG}(V_{IN}=V_{DD}) = \beta_{P}e^{\frac{|V_{TH,P(BBG)}^{0}|-\lambda_{D}^{P(BBG)}V_{DD}-\lambda_{B}^{P(BBG)}(V_{DD}-V_{L})}{n_{P}V_{T}}} + \beta_{N(BBG)}e^{\frac{V_{L}+V_{TH,N(BBG)}^{0}-\lambda_{D}^{N(BBG)}(V_{DD}-V_{L})-\lambda_{B}^{N(BBG)}V_{L}}{n_{N}V_{T}}}.$ (2.7)

It is easy to verify that (2.6) and (2.7) are obtained exploiting subtreshold drain current expressions given in (2.1)-(2.4) where the term  $1 - e^{-V_{DS,N}/n_NV_T}$  and  $1 - e^{V_{SD,P}/n_PV_T}$  are neglected since both  $V_{DS,N}$  and  $V_{SD,P}$  are greater than  $4V_T$  [33]. The first term in (2.6) and (2.7) is related to the leakage current in the logic section of the gate, whereas the second additive term captures the static current flowing through the BBG. From (2.6) and(2.7), it is clear that the proposed technique incurs in leakage penalties with respect to the conventional CMOS approach not only because of the FBB of the OFF transistors in the logic section but also because of the additional static current flowing through the BBG. In the following, we quantify this leakage current penalty.

# Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits

Figure 2.4: Equivalent circuits for leakage analysis when  $V_{IN}$  is low (a) and high (b), respectively.

For a conventional static CMOS inverter, the leakage current in the steady state can be expressed as [3, 4]:

$$I_{leak}^{INV}(V_{IN} = 0) = \beta_{N}e^{-\frac{V_{TH,N}^{0} - \lambda_{D}^{0}V_{DD}}{n_{N}V_{T}}},$$

(2.8)

$$I_{leak}^{INV}(V_{IN} = V_{DD}) = \beta_{P}e^{-\frac{|V_{TH,P}^{0}| - \lambda_{D}^{P}V_{DD}}{n_{P}V_{T}}}$$

(2.9)

It is worth noting that (2.8) and (2.9) can be also obtained from (2.6) and (2.7) by simply removing the impact of the BBG on leakage current (second term in (2.6) and (2.7)) and imposing the conditions of  $V_H = 0V$  and  $V_L = V_{DD}$  ( $V_{BS,N} = V_{SB,P} = 0$ ). Hence, when the nMOS is the leaky tran-

sistor, the leakage penalty is obtained by calculating the ratio between (2.6) and (2.8) while, when the pMOS is the leaky transistor, the penalty in terms of leakage current is obtained by evaluating the ratio between (2.7) and (2.9):

| $(\mathbf{n})$ | 1 | 1 | 1 |

|----------------|---|---|---|

| (2.            | I | I | ) |

From (2.10) and (2.11), the leakage penalty consists of the sum of two different contributions. The first term isolates the effect of the FBB provided by BBG, which causes the threshold voltage reduction of leaky devices belonging to the logical section of the gate. The second term provides the increment of the leakage current due to the additional push-pull amplifier, which is also dependent on the body voltage of devices belonging to the logical section of the gate. Moreover, such a term depends linearly on the ratio between the current factors of the leaky transistor in the logic section and the dual device in the BBG. According to (2.10) and (2.11) the impact of the proposed technique on leakage current can be reduced: 1) by lowering  $V_H$  and increasing  $V_L$ ; 2) by choosing an aspect ratio for the BBG transistors much lower than the aspect ratio of the transistors used in the logic sub-circuit; 3) by using higher threshold voltage transistors for the MOSFETs in the BBG. All the conclusions here obtained can be easily extended to a generic logic gate.

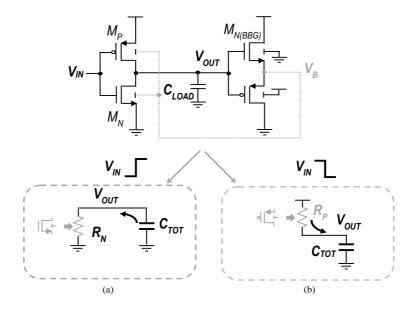

### 2.2.2 Delay analysis

Without loss of generality, we initially consider that a  $0 \rightarrow 1$  step input transition occurs. During the  $1\rightarrow 0$  output switching, the nMOS transistor is turned on and the inverter gate can be schematized through the equivalent circuit shown in Figure 2.5 (a). Here,  $R_N$  represents the effective resistance of the nMOS, forward body biased by the BBG sub-circuit, and  $C_{TOT}$  is the overall capacitance on the output node which is given by the sum of the load capacitance  $C_{LOAD}$ , the input capacitance  $C_{IN,BBG}$  of the additional BBG circuit and the internal subthreshold capacitance [54]  $C_{INT}$  of the logic sub-circuit. Modeling the output discharging as shown in Figure 2.5 (a), the H to L delay can be expressed as [55]:

$$\tau_{HL} = \ln(2)C_{TOT}R_N,$$

(2.12)

where  $R_N$  is evaluated considering the  $V_{OUT}$  transition from  $V_{DD}$  to  $V_{DD}/2$  [55]:

$$R_N = \frac{2}{V_{DD}} \int_{V_{DD}/2}^{V_{DD}} \frac{V_{OUT}}{I_N} dV_{OUT}$$

(2.13)

where  $V_{out} = V_{DS,N}$  and  $I_N$  represent the drain-to-source voltage and the drain current of transistor  $M_N$ , respectively. The expression of the drain current can be evaluated by using (2.1) and (2.3) and imposing  $V_{GS,N} = V_{DD}$ ,  $V_{DS,N} = V_{OUT}$  and  $V_{BS,N} = V_B$ . For supply voltages higher than about 200 mV, the contribution due to the term  $e^{-V_{DS,N}/n_N V_T}$  can be neglected

without loss of accuracy. This is because, for  $V_{OUT}$  falling from  $V_{DD}$  to  $V_{DD}/2$ ,  $V_{DS,N}$  is always higher than  $4V_T$  (~104 mV @ 27°C) [33].

Figure 2.5: Equivalent circuits to model inverter switching in the case of an L to H (a) and H to L (b) input transition

In order to obtain an easier expression for  $V_B$ , the gain of the push-pull amplifier is here approximated by its DC value. Thus, according to the previous considerations, the body voltage  $V_B$  during the H to L and L to H transition can be expressed as:

$$V_B \approx \begin{cases} V_H - A(V_{DD} - V_{OUT}) & H \to L \\ V_L + AV_{OUT} & L \to H \end{cases},$$

$$(2.14)$$

where *A* is the DC gain of the push-pull amplifier (i.e. the BBG). Using (2.14) to compute  $I_N$  and solving the integral in (2.13), the H to L delay given by (2.12) becomes equal to:

Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits

$$\tau_{HL} = \ln(2)C_{TOT} \frac{2}{V_{DD}} \frac{1}{k_{HL}k_N^2} \times \left[ e^{-\frac{V_{DD}}{2}k_N} \left( \frac{V_{DD}}{2} k_N + 1 \right) - e^{-V_{DD}k_N} \left( V_{DD} k_N + 1 \right) \right]$$

(2.15)

where  $k_{HL} = \beta_N e^{\frac{V_{DD} - V_{TH,N}^0 + \lambda_B^N (V_H - V_{DD})}{n_N V_T}}$  and  $k_N = \left(\lambda_D^N + A\lambda_B^N\right) / n_N V_T$ .

The L to H delay can be evaluated in a similar way. The charging phase of the capacitance  $C_{TOT}$  is modeled as shown in Figure 2.5 (b), where the current flowing through the transistor  $M_P$  is obtained from (2.2) and (2.4) with the conditions:  $V_{SG,P} = V_{DD}$ ,  $V_{SD,P} = V_{DD} - V_{OUT}$  and  $V_{SB,P} = V_{DD} - V_B$ . Also in this case the contribution due to the term  $e^{-V_{SD,P}/n_PV_T}$  can be neglected. Finally, the L to H delay results to be:

$$\tau_{LH} = \ln(2)C_{TOT} \frac{2}{V_{DD}} \frac{1}{k_{LH}k_P^2} \times \left[ e^{\frac{V_{DD}}{2}k_P} \left( \frac{V_{DD}}{2}k_P + 1 \right) - \left( V_{DD}k_P + 1 \right) \right],$$

(2.16)

where

$$k_{LH} = \beta_P e^{\frac{V_{DD} - |V_{1H,P}^0| + \lambda_D^P V_{DD} + \lambda_B^P (V_{DD} - V_L)}{n_P V_T}}$$

and  $k_P = (\lambda_D^P + A \lambda_B^P) / n_P V_T$ .

As previously done for the leakage current, we evaluate the speed improvement offered by the proposed scheme in comparison to the conventional static CMOS solution. In the case of a static CMOS inverter, expressions for H to L and L to H delays can be obtained from (2.15) and (2.16), respectively by canceling the effect of the FBB on the switching device (i.e.  $V_H = 0, V_L = V_{DD}, A = 0$ ). Thus, we find:

$$\tau_{HL}^{CONV} = \ln(2)C \frac{2}{V_{DD}} \frac{1}{k_{HL,C} k_{N,C}^2} \times \left[ e^{-\frac{V_{DD}}{2} k_{N,C}} \left( \frac{V_{DD}}{2} k_{N,C} + 1 \right) - e^{-V_{DD} k_{N,C}} \left( V_{DD} k_{N,C} + 1 \right) \right],$$

(2.17)

$$\tau_{LH}^{CONV} = \ln(2)C \frac{2}{V_{DD}} \frac{1}{k_{LH,C} k_{P,C}^2} \times \left[ e^{\frac{V_{DD}}{2} k_{P,C}} \left( \frac{V_{DD}}{2} k_{P,C} + 1 \right) - \left( V_{DD} k_{P,C} + 1 \right) \right],$$

(2.18)

where  $k_{HL} = \beta_N e^{\frac{V_{DD} - V_{TH,N}^0}{n_N V_T}}$ ,  $k_N = \lambda_D^N / n_N V_T$ ,  $k_{LH} = \beta_P e^{\frac{V_{DD} - |V_{TH,P}^0| + \lambda_D^P V_{DD}}{n_P V_T}}$  and  $k_P = \lambda_D^P / n_P V_T$ . It is worth noting that, in both (2.17) and (2.18), the output capacitance of the static CMOS inverter is indicated with  $C = C_{LOAD} + C_{INT}$  instead of  $C_{TOT} = C_{LOAD} + C_{IN,BBG} + C_{INT}$  in order to take into account the reduced output loading capacitance (i.e. the BBG loading capacitance is not included). From the ratio between (2.15) and (2.17), the delay reduction during the H to L transition is given by:

$$\frac{\tau_{HL}^{CONV}}{\tau_{HL}} = \frac{C}{C_{TOT}} \left( 1 + A \frac{\lambda_B^N}{\lambda_D^N} \right)^2 e^{\frac{\lambda_B^N V_H}{n_N V_T}} \times \frac{\left[ e^{-\frac{V_{DD}}{2} k_{N,C}} \left( \frac{V_{DD}}{2} k_{N,C} + 1 \right) - e^{-V_{DD} k_N} \left( V_{DD} k_{N,C} + 1 \right) \right]}{\left[ e^{-\frac{V_{DD}}{2} k_N} \left( \frac{V_{DD}}{2} k_N + 1 \right) - e^{-V_{DD} k_N} \left( V_{DD} k_N + 1 \right) \right]},$$

(2.19)

Similarly, the delay reduction during the L to H transition is obtained from the ratio between (2.16) and (2.18):

Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits

$$\frac{\tau_{LH}^{CONV}}{\tau_{LH}} = \frac{C}{C_{TOT}} e^{\frac{\lambda_B^P(V_{DD} - V_L)}{n_P V_T}} \left(1 + A \frac{\lambda_B^P}{\lambda_D^P}\right)^2 \times \frac{\left[e^{\frac{V_{DD}}{2}k_{P,C}} \left(\frac{V_{DD}}{2}k_{P,C} + 1\right) - \left(V_{DD}k_{P,C} + 1\right)\right]}{\left[e^{\frac{V_{DD}}{2}k_P} \left(\frac{V_{DD}}{2}k_P + 1\right) - \left(V_{DD}k_P + 1\right)\right]}.$$

(2.20)

From (2.19) and (2.20), the delay reduction during H to L and L to H output transitions is enhanced by raising  $V_H$  and lowering  $V_L$ , respectively. In addition, since  $C_{TOT} \approx C + C_{IN,BBG}$ , the speed advantage of the proposed technique is increased if the input capacitance of the push-pull amplifier is minimized.

### 2.3 Design Criteria and Analysis Validations

The analytical modeling previously discussed is here exploited to define proper design criteria for both logic sub-circuit and BBG. From (2.10) and (2.11), a way to limit the static current flowing in the BBG consists of increasing the threshold voltage of devices employed in the push-pull amplifier. For this reason, both  $M_{N(BBG)}$  and  $M_{P(BBG)}$  are chosen as high threshold voltage (HVT) transistors. Note that this choice emphasizes the inherent limitation of the static current in the BBG due to the reverse body biasing of its transistors  $V_{BS,N}$  and  $V_{SB,P}$  are always less than zero for  $M_{N(BBG)}$  and  $M_{P(BBG)}$ , respectively). Furthermore, since HVT transistors in the referred CMOS technology have the same oxide thickness (i.e. the same  $C_{OX}$ ) but different doping profile in comparison to standard threshold voltage (SVT) devices, this choice does not have any additional impact on the gate loading capacitance. On the other hand, to guarantee higher gate speed, standard threshold voltage (SVT) transistors are employed in the logic section of the gate. Since different threshold voltage devices and triple well option are widely available in modern foundry technologies [55].

From (2.19) and (2.20), the input capacitance of the BBG has to be minimized to further improve the gate speed. To this aim, the minimum sizing (W=120 nm and L=40 nm) allowed by the chosen design kit is used for both  $M_{N(BBG)}$  and  $M_{P(BBG)}$ . This has also a beneficial impact on the leakage current (because of the reduced W). It is worth noting that the option of lowering leakage current of the logic sub-circuit by decreasing  $V_H$  and increasing  $V_L$  was avoided since it has an adverse impact in terms of speed.

Sizing the BBG for the minimum static current and the minimum input capacitance leads to the obvious condition of  $V_L \neq V_{DD} - V_H$  This effect, in conjunction with the difference in mobility, DIBL and body coefficients of the nMOS and pMOS transistors employed in the logic sub-circuit, leads to an implicit asymmetry between the H to L and L to H gate responses. However, as for conventional CMOS logic gates, such asymmetry in the response can be easily compensated by proper sizing transistors in the logic sub-circuit.

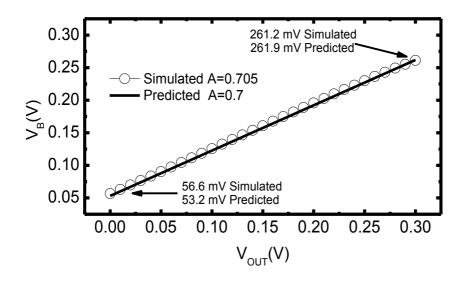

In order to validate our theoretical analysis, we compared the predicted results with the simulation data obtained by Cadence Spectre. To ensure subthreshold operation, all comparisons discussed in this paper are performed imposing a power supply voltage ( $V_{DD}$ ) of 300 mV. Figure 2.6 shows the predicted (i.e. evaluated by (2.5)) and the simulated DC transfer function for the BBG. In particular, the predicted value for  $V_H$  ( $V_L$ ) is 261.2 mV (53.2 mV) instead of the simulated value of 261.9 mV (56.6 mV). This small difference is due to the fact that the contribution of the terms 1-

$$e^{\frac{V_{DS,N}}{V_T}}$$

and  $1 - e^{\frac{V_{SD,P}}{V_T}}$  was neglected in (2.5). In fact, since  $V_{DS,N}$  and  $V_{SD,P}$  are

both lower than  $4V_T$ , these terms are slightly lower than 1. As shown in Figure 2.6, the proposed sizing for the BBG leads the high logic state to be transferred slightly better than the low logic state.

Figure 2.6: Predicted versus simulated BBG DC transfer function

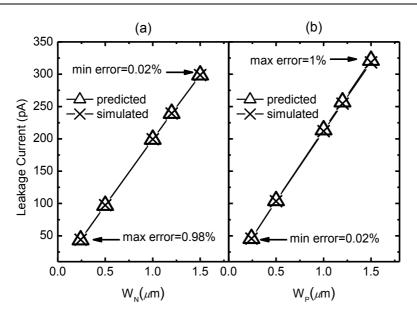

As explained before, the DC analysis of the BBG provides the background needed for the leakage current evaluation. Figure 2.7 shows a very good agreement between the predicted and the simulated leakage currents due to the pull-down (Figure 2.7(a)) and pull-up (Figure 2.7(b)) transistors. As predicted by (2.6) and (2.7) the impact of the BBG leakage is about 1.1% of the overall leakage current, thus confirming the goodness of the design criteria used to limit the static current of the BBG.

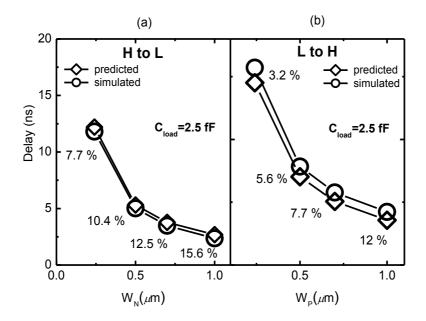

In order to validate the developed delay analysis, the H to L and the L to H delays were evaluated for different transistor widths by using (2.16) and (2.19), respectively. In such expressions technological parameters (i.e. current factor  $\beta$ , DIBL and body coefficients,...) were extracted using the Ca-

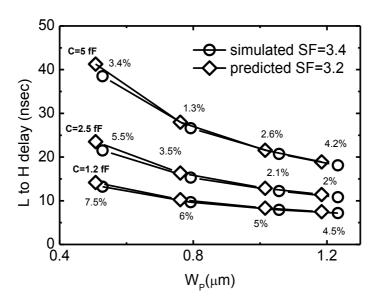

dence Spectre simulator. Figure 2.8 compares the predicted and the simulated delay data. Percentage errors are also reported. All the results were obtained considering a channel width for the OFF transistors equal to 120 nm, a load capacitance of 2.5 fF, typical-typical (TT) process corner and an operating temperature of 27 °C. By inspecting Figure 2.8, it is easy to observe that the predicted delay values track well the simulation results. Mean errors are 11.5% and 7.1% for L to H delay and H to L delay, respectively. It is worth noting that our delay modeling also provides useful guidelines for sizing the transistors in the logic sub-circuit. By exploiting the results obtained from (2.15) and (2.16), the optimum transistor sizing ratio  $W_P/W_N$  which ensures the condition of near equal delay on the minimum sized transistors ( $W_N = 0.24 \ \mu$ m) in the two output transitions is predicted to be 1.28 which is very close to the simulated value equal to 1.33. This means a difference of only 3.8 % between the simulated and the predicted dimensioning for the transistors in the pull-up network.

Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits

Figure 2.7: Predicted versus simulated leakage currents for low (a) and high (b) input logic value

Figure 2.8: Simulated vs predicted L to H (a) and H to L (b) delay results (channel width of the OFF transistor is equal to 120 nm)

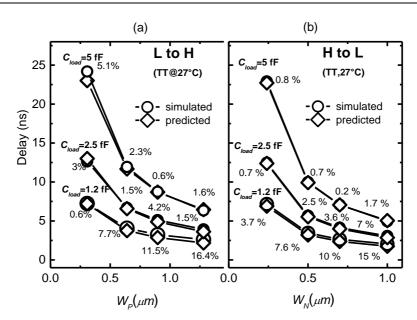

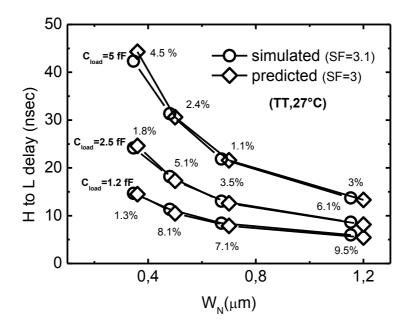

Figure 2.9 reports the predicted and the simulated delay values for the L to H and the H to L transition for different values of the load capacitance. To evaluate the goodness of the design obtained by using the proposed modeling instead of the use of Cadence Spectre simulator, in Figure 2.9 the predicted results are obtained for  $W_P/W_N=1.28$  (predicted optimal) and compared with the simulated delay values obtained assuming the simulated optimal value of 1.33. Comparing the predicted and the simulated results, the mean error in the L to H transition is equal to 9%, 2.5 % and 2.4 % for  $C_{load}$  equal to 1.2 fF, 2.5 fF, and 5 fF, respectively. In the case of the H to L transition, the mean error becomes 9.1% @ 1.2 fF, 2.4% @ 2.5 fF and 0.8% @ 5 fF.

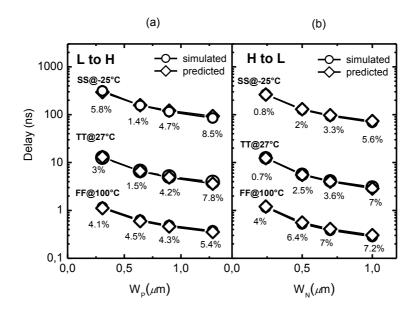

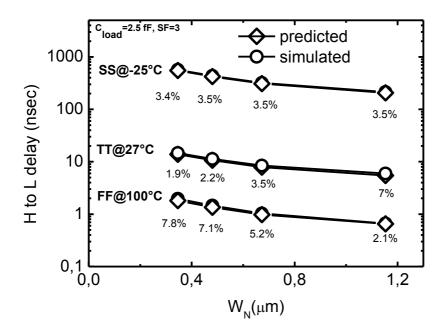

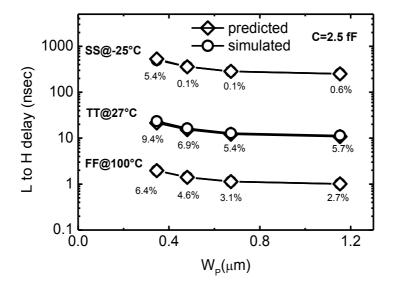

In Figure 2.10 the proposed modeling is further validated for different process corners and temperatures. In particular delay results are extracted for the typical-typical (TT) process corner at the standard temperature of 27 °C, the fast-fast (FF) process corner at the temperature of 100°C and the slow-slow (SS) process corner at the temperature of -25°C. All the results are obtained considering  $C_{load} = 2.5 fF$  and  $W_P/W_N=1.28$ . For the L to H transition the observed mean error (absolute value) is 4.1 %, 4.6 % and 5.1 % for the (TT,27°C), (FF,100°C) and (SS,-25°C) conditions, respectively. Similar percentage errors are obtained in the case of H to L transition.

Table 2.1 and Table 2.2 compare predicted (based on analytically optimization, i.e.  $W_P/W_N=1.28$ ) and simulated (based on only a simulation optimization, i.e.  $W_P/W_N=1.33$ ) delay results for different operating conditions and for a load capacitance of 2.5 fF. Again, the good agreement between the simulated and predicted results confirms the goodness of the proposed approach for sizing the logic sub-circuit.

Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits

Figure 2.9: Comparison between the predicted (WP/WN = 1.28) and simulated (WP/WN = 1.33) L to H (a) and H to L delay (b) for different values of the load capacitance

Figure 2.10: Corner analysis for the L to H (a) and H to L (b) output transitions (WP/WN=1.28 and Cload=2.5 fF)

Table 2.1: H to L inverter delay comparison for different process corner and temperatures. inverter delay comparison for different process corner

| $W_p/W_n = \beta$ | TT @ 27°C      |                | FF @ 100°C     |                | SS @ -25°C     |                |

|-------------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                   | Pred.          | Sim.           | Pred.          | Sim.           | Pred.          | Sim.           |

| W <sub>N</sub>    | $\beta = 1.28$ | $\beta = 1.33$ | $\beta = 1.28$ | $\beta = 1.33$ | $\beta = 1.28$ | $\beta = 1.33$ |

| (µm)              | [ns]           | [ns]           | [ns]           | [ns]           | [ns]           | [ns]           |

| 0.24              | 12.5           | 12.5           | 1.2            | 1.2            | 262            | 263            |

| 0.5               | 5.7            | 5.7            | 0.5            | 0.5            | 130            | 1.30           |

| 0.7               | 4.1            | 4.2            | 0.4.           | 0.4            | 97             | 97.5           |

| 1                 | 3.1            | 3.1            | 0.3            | 0.3            | 73.5           | 73.9           |

and temperatures.

Table 2.2: L to H inverter delay comparison for different process corner and temperatures.

| $W_p/W_n = \beta$ | TT @ 27°C      |                | FF @           | 100°C          | SS @ -25°C     |                |

|-------------------|----------------|----------------|----------------|----------------|----------------|----------------|

|                   | Pred.          | Sim.           | Pred.          | Sim.           | Pred.          | Sim.           |

| W <sub>N</sub>    | $\beta = 1.28$ | $\beta = 1.33$ | $\beta = 1.28$ | $\beta = 1.33$ | $\beta = 1.28$ | $\beta = 1.33$ |

| (µm)              | [ns]           | [ns]           | [ns]           | [ns])          | [ns]           | [ns]           |

| 0.24              | 12.6           | 12.2           | 1.2            | 1.1            | 296            | 285            |

| 0.5               | 6.7            | 6.4            | 0.6            | 0.6            | 158            | 153            |

| 0.7               | 5.1            | 4.9            | 0.5            | 0.5            | 121            | 117            |

| 1                 | 3.9            | 3.8            | 0.4            | 0.4            | 93             | 90             |

### 2.4 Logic Gates with Stacked Transistors

In this section, the developed delay analysis is extended to logic gates with transistor stacks, such as NAND2 and NOR2.

# NAND2

Figure 2.11 shows the schematic of the proposed NAND2 gate. When  $V_{OUT}$  undergoes a L to H output transition, the worst case delay occurs

# Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits

when the charging of the total output capacitance is driven by just one of the pMOS transistors in the pull-up network. Consequently, the L to H delay modeling can be reduced to that already described for the inverter gate when the pMOS is switched on. On the contrary, the delay modeling for the H to L output transition cannot be easily traced to the switching of a single nMOS with equivalent width. During the H to L output switching, the voltage  $V_X$  at the intermediate node of the pull-down network is greater than 0 V [56], thus reducing the overdrive voltage of the upper transistor in the stack. This effect, which is particularly severe in the subthreshold regime due to the exponential relationship between the drain current and the gate-to-source voltage, has been properly taken into account in the following analysis. The starting point to find an analytical expression for  $V_X$  is obtained by equating the currents flowing in the two stacked transistors:

$$I_{N,1} = \beta_{N,1} e^{\frac{V_{DD} - V_X - V_{TH,N(1)}}{n_N V_T}} \left[ 1 - e^{\frac{V_{OUT} - V_X}{V_T}} \right] = \beta_{N,2} e^{\frac{V_{DD} - V_{TH,N(2)}}{n_N V_T}} \left[ 1 - e^{\frac{V_X}{V_T}} \right] = I_{N,2}.$$

$$(2.21)$$

Typically,  $V_X \approx 0.1 V_{DD}$  [56], thus the term  $e^{-(V_{OUT}-V_X)/V_T}$  can be neglected without any significant penalty in terms of model accuracy. Using this simplification, (2.21) can be rewritten as:

$$\frac{W_{N,1}}{W_{N,2}} e^{\frac{V_{TH,N(2)} - V_{TH,N(1)}}{n_N V_T}} \approx e^{\frac{V_X}{n_N V_T}} \left[ 1 - e^{-\frac{V_X}{V_T}} \right].$$

(2.22)

Since  $M_{N,1}$  and  $M_{N,2}$  have the same zero bias threshold voltage, the difference  $V_{TH,N(2)}$ - $V_{TH,N(1)}$  only depends on the difference between the drainsource and body-source polarizations. Replacing in (2.3) the conditions:  $V_{DS}=V_{OUT}-V_X$ ,  $V_{BS}=V_B-V_X$  for  $M_{N,1}$  and  $V_{DS}=V_X$ ,  $V_{BS}=V_B$  for  $M_{N,2}$ , the difference between the two threshold voltages is given by:

$$V_{TH,N(1)} - V_{TH,N(2)} = \lambda_D^N V_{OUT} - V_X \left( 2\lambda_D^N + \lambda_B^N \right)$$

(2.23)

$$e^{\frac{V_{X}}{n_{N}V_{T}}} \left[ 1 - e^{-\frac{V_{X}}{V_{T}}} \right] \approx a_{X} e^{b_{X}V_{X}},$$

$$(2.24)$$

For a fixed value of temperature, the second term in (2.22) can be approximated as:

where  $a_x$  and  $b_x$  are two fitting parameters which depend on the considered voltage range for  $V_X$ . For example, assuming  $V_X$  in the range from 25 mV to 50 mV the value of  $a_x$  and  $b_x$  are equal to 0.487 and 35, respectively. Replacing (2.23) and (2.24) into (2.22), the following expression for  $V_X$  is obtained:

$$V_X \approx \frac{n_N V_T \left[ \ln \left( \frac{W_{N,1}}{W_{N,2}} \right) - \ln(a_x) \right] + \lambda_D^N V_{OUT}}{n_N V_T b_x + 2\lambda_D^N + \lambda_B^N},$$

(2.25)

where  $W_{N,1}$  and  $W_{N,2}$  are the channel width of transistor  $M_{N,1}$  and  $M_{N,2}$ , respectively. As demonstrated in [56], only negligible improvements in terms of current driving are achieved by considering skewed sizing for transistors in the stack. For this reason, the condition  $W_{N,1}=W_{N,2}$  is assumed for the rest of this analysis. Such a choice also reduces the design complexity [56]. With reference to the upper transistor  $M_{N,1}$ , the driving cur-

rent flowing in the stack, during the H to L output transition, can be expressed as:

$$I_{stack} \approx \beta_{N,1} e^{\frac{V_{DD} - V_X - V_{TH,N(1)}}{n_N V_T}}$$

$$SF = \frac{W_{stack}}{W_{\sin gle}} \approx \frac{C_{NAND}}{C_{INV}} e^{\frac{V_X \left(1 + \lambda_D^N + \lambda_B^N\right)}{n_N V_T}}.$$

(2.27)

From (2.26) the stacking factor (SF) which ensures the condition of equal delay between the NAND2 gate and the inverter in the H to L delay is equal to:

In (2.27)  $C_{NAND}$  is the total output capacitance in the NAND2 gate while  $C_{INV}$  represents the total output capacitance in the inverter gate. According to (2.27), two stacked transistors should be sized up by SF in relation to a single device for similar current drivability. Moreover, (2.27) shows that *SF* depends exponentially on voltage  $V_X$ , which according to (2.25), mainly depends on  $V_{OUT}$ , DIBL coefficient, body coefficient and subthreshold slope factor. This means that it is quite difficult to ensure the equality

Analytical Modeling for Dynamic Gate – Level Body Biased Logic Circuits